正如英特爾公司CEO Pat Gelsinger所言:“我們正在加快制程工藝創(chuàng)新的路線圖,以確保到2025年制程性能再度領(lǐng)先業(yè)界。”

在今日凌晨舉辦的先進(jìn)工藝及封裝技術(shù)大會(huì)上,除了公布有史以來(lái)最詳細(xì)的制程技術(shù)路線圖以及公司在封裝、晶圓代工、極紫外光刻(EUV)工藝上的規(guī)劃以外,英特爾還宣布了一個(gè)令人震驚的消息:將為高通提供代工服務(wù),這還是開天辟地頭一次。高通也將因此成為英特爾重整代工業(yè)務(wù)以來(lái)最大、最具重量級(jí)的客戶。

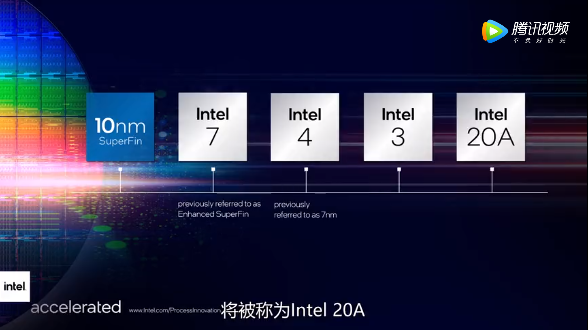

全新的制程節(jié)點(diǎn)命名體系

據(jù)Pat Gelsinger介紹,從2021年至2025年,英特爾計(jì)劃每年至少都將推出一款新的中央處理器(CPU),而且每一款都將基于比前一代更先進(jìn)的晶體管技術(shù)。英特爾公司還公布了未來(lái)四年將要推出的5個(gè)制程工藝發(fā)展階段,包括10nm、7nm、4nm、3nm以及20A。這次,英特爾還為其制程節(jié)點(diǎn)引入了全新的命名體系,其中包含新的節(jié)點(diǎn)命名和實(shí)現(xiàn)每個(gè)制程節(jié)點(diǎn)的創(chuàng)新技術(shù)如下:

圖片源自英特爾視頻會(huì)議截圖

●Intel 7(此前稱之為10nm Enhanced SuperFin)

通過(guò)FinFET晶體管優(yōu)化,每瓦性能比英特爾10納米SuperFin提升約10% - 15%,優(yōu)化方面包括更高應(yīng)變性能、更低電阻的材料、新型高密度蝕刻技術(shù)、流線型結(jié)構(gòu),以及更高的金屬堆棧實(shí)現(xiàn)布線優(yōu)化。Intel 7將在這些產(chǎn)品中亮相:于2021年推出的面向客戶端的Alder Lake,以及預(yù)計(jì)將于2022年第一季度投產(chǎn)的面向數(shù)據(jù)中心的Sapphire Rapids。

●Intel 4(此前稱之為Intel 7nm)

與Intel 7相比,Intel 4的每瓦性能提高了約20% ,它是首個(gè)完全采用EUV光刻技術(shù)的英特爾FinFET節(jié)點(diǎn),EUV采用高度復(fù)雜的透鏡和反射鏡光學(xué)系統(tǒng),將13.5納米波長(zhǎng)的光對(duì)焦,從而在硅片上刻印極微小的圖樣。相較于之前使用波長(zhǎng)為193納米的光源的技術(shù),這是巨大的進(jìn)步。Intel 4將于2022年下半年投產(chǎn),2023年出貨,產(chǎn)品包括面向客戶端的Meteor Lake和面向數(shù)據(jù)中心的Granite Rapids。

● Intel 3

Intel 3將繼續(xù)獲益于FinFET,較之Intel 4,Intel 3將在每瓦性能①上實(shí)現(xiàn)約18%的提升。這是一個(gè)比通常的標(biāo)準(zhǔn)全節(jié)點(diǎn)改進(jìn)水平更高的晶體管性能提升。Intel 3實(shí)現(xiàn)了更高密度、更高性能的庫(kù);提高了內(nèi)在驅(qū)動(dòng)電流;通過(guò)減少通孔電阻,優(yōu)化了互連金屬堆棧;與Intel 4相比,Intel 3在更多工序中增加了EUV的使用。Intel 3將于2023年下半年開始生產(chǎn)相關(guān)產(chǎn)品。

●Intel 20A

PowerVia和RibbonFET這兩項(xiàng)突破性技術(shù)開啟了埃米時(shí)代。PowerVia是英特爾獨(dú)有、業(yè)界首個(gè)背面電能傳輸網(wǎng)絡(luò),它消除晶圓正面的供電布線需求,優(yōu)化信號(hào)布線,同時(shí)減少下垂和降低干擾。RibbonFET是英特爾研發(fā)的Gate All Around晶體管,是公司自2011年率先推出FinFET以來(lái)的首個(gè)全新晶體管架構(gòu),提供更快的晶體管開關(guān)速度,同時(shí)以更小的占用空間實(shí)現(xiàn)與多鰭結(jié)構(gòu)相同的驅(qū)動(dòng)電流。Intel 20A預(yù)計(jì)將在2024年推出。

●Intel 18A

從Intel 20A更進(jìn)一步的Intel 18A節(jié)點(diǎn)也已在研發(fā)中,將于2025年初推出,它將對(duì)RibbonFET進(jìn)行改進(jìn),在晶體管性能上實(shí)現(xiàn)又一次重大飛躍。

為何要如此命名?

一直以來(lái),芯片業(yè)界都是采用基于納米的方式對(duì)傳統(tǒng)制程節(jié)點(diǎn)進(jìn)行命名,英特爾此次引入全新的名字體系有何深意?實(shí)際上,英特爾一直沿用這種歷史模式,即使用反映尺寸單位(如納米)的遞減數(shù)字來(lái)為節(jié)點(diǎn)命名。但在如今整個(gè)行業(yè)使用著各不相同的制程節(jié)點(diǎn)命名和編號(hào)方案的情況下,這些多樣的方案既不再指代任何具體的度量方法,也無(wú)法全面展現(xiàn)如何實(shí)現(xiàn)能效和性能的最佳平衡。

為此,英特爾引入了基于關(guān)鍵技術(shù)參數(shù)——包括性能、功耗和面積等的新命名體系。從上一個(gè)節(jié)點(diǎn)到下一個(gè)節(jié)點(diǎn)命名的數(shù)字遞減,反映了對(duì)這些關(guān)鍵參數(shù)改進(jìn)的整體評(píng)估。同時(shí),隨著芯片工藝制程逼近極限,行業(yè)越來(lái)越接近“1nm”節(jié)點(diǎn)的局面下,英特爾改變命名方式以更好地反映全新的創(chuàng)新時(shí)代。比如在Intel 3之后的下一個(gè)節(jié)點(diǎn)被命名為Intel 20A,這一命名反映了向新時(shí)代的過(guò)渡,即工程師在原子水平上制造器件和材料的時(shí)代——半導(dǎo)體的埃米時(shí)代。這種命名體系將創(chuàng)建一個(gè)清晰而有意義的框架,來(lái)幫助行業(yè)和客戶對(duì)整個(gè)行業(yè)的制程節(jié)點(diǎn)演進(jìn)有更準(zhǔn)確的認(rèn)知,進(jìn)而做出更明智的決策。這也是為了順應(yīng)英特爾代工服務(wù)(IFS)的推出,以便于讓客戶比以往都更加清晰了解情況。

兩大創(chuàng)新性技術(shù):RibbonFET和PowerVia

英特爾在演講中提到,公司將于2024年上半年推出的Intel 20A會(huì)成為制程技術(shù)的又一個(gè)分水嶺。它擁有兩大開創(chuàng)性技術(shù)——RibbonFET的全新晶體管架構(gòu),名為PowerVia的史無(wú)前例的創(chuàng)新技術(shù),可優(yōu)化電能傳輸。

全新晶體管架構(gòu)RibbonFET

在上文中我們提到,步入Intel 20A階段,英特爾的工藝名稱指的是埃而不是納米,這也意味著英特爾將從FinFET設(shè)計(jì)過(guò)渡到一種新的晶體管(GAAFET),而英特爾將其稱之為RibbonFET(也有的芯片廠商將其稱為MCBFET)。人們預(yù)計(jì),隨著摩爾定律逼近極限,F(xiàn)inFET設(shè)計(jì)無(wú)法再為先進(jìn)工藝制程提供支持時(shí),GAAFET設(shè)計(jì)將會(huì)成為主流。相比之下,F(xiàn)inFET依賴于源極/漏極的多個(gè)量化鰭片和多個(gè)鰭片軌跡的單元高度,而GAAFET支持可變長(zhǎng)度的單個(gè)鰭片,從而允許在功率、性能或面積方面優(yōu)化每個(gè)單獨(dú)單元器件的電流。

據(jù)英特爾介紹,RibbonFET是一個(gè)Gate All Around晶體管,從設(shè)計(jì)上看,這個(gè)全新設(shè)計(jì)將柵極完全包裹在通道周圍,可實(shí)現(xiàn)更好的控制,并在所有電壓下都能獲得更高的驅(qū)動(dòng)電流。新的晶體管架構(gòu)加快了晶體管開關(guān)速度,最終可打造出更高性能的產(chǎn)品。通過(guò)堆疊多個(gè)通道,即納米帶,可以實(shí)現(xiàn)與多個(gè)鰭片相同的驅(qū)動(dòng)電流,但占用的空間更小。通過(guò)對(duì)納米帶的部署,英特爾可以使得帶的寬度可以被調(diào)整,以適應(yīng)多種應(yīng)用。

早在去年的國(guó)際VLSI會(huì)議上英特爾就曾披露過(guò)關(guān)于GAAFET設(shè)計(jì)的相關(guān)信息,當(dāng)時(shí)被告知英特爾批量實(shí)施GAAFET設(shè)計(jì)的時(shí)間會(huì)在5年內(nèi)。如今,英特爾的20A工藝將采用RibbonFET設(shè)計(jì),根據(jù)上述路線圖,很可能在2024年底實(shí)現(xiàn)規(guī)模化量產(chǎn)。

當(dāng)然,GAAFET設(shè)計(jì)也并非英特爾獨(dú)家專屬,臺(tái)積電預(yù)計(jì)將在2nm工藝上采用GAAFET設(shè)計(jì),而三星將在其3nm工藝節(jié)點(diǎn)中引入GAAFET設(shè)計(jì)。其中三星可能是第一個(gè)邁入GAAFET大門的。

全新背面電能傳輸網(wǎng)絡(luò)PowerVia

另外一項(xiàng)全新技術(shù)——PowerVia,這是由英特爾工程師開發(fā)的全新背面電能傳輸網(wǎng)絡(luò),也將在Intel 20A中首次采用。眾所周知,現(xiàn)代電路的制造過(guò)程從晶體管層M0作為最小層開始,在此之上以越來(lái)越大的尺寸添加額外的金屬層,以解決晶體管與處理器不同部分之間所需的所有布線。這種傳統(tǒng)的互連技術(shù)產(chǎn)生的電源線和信號(hào)線的互混,導(dǎo)致了布線效率低下的問(wèn)題,會(huì)影響性能和功耗。通過(guò)PowerVia技術(shù),英特爾把電源線置于晶體管層的下面,通過(guò)消除晶圓正面的電源布線需求,可騰出更多的資源用于優(yōu)化信號(hào)布線并減少時(shí)延。通過(guò)減少下垂和降低干擾,也有助于實(shí)現(xiàn)更好的電能傳輸。該技術(shù)降低了設(shè)計(jì)上的IR壓降,這在更先進(jìn)的工藝節(jié)點(diǎn)技術(shù)上越來(lái)越難以實(shí)現(xiàn)以提高性能。當(dāng)該技術(shù)在高性能處理器上大量使用時(shí),將會(huì)很有趣。

更加先進(jìn)的封裝路線圖

●EMIB:首個(gè)2.5D嵌入式橋接解決方案

自2017年以來(lái),英特爾一直在出貨EMIB產(chǎn)品,EMIB技術(shù)專為布局在2D平面上的芯片到芯片連接而設(shè)計(jì)。它將中介層和基板結(jié)合,使用小型硅片并將其直接嵌入基板中,英特爾將其稱為橋接器。橋?qū)嶋H上是兩半,每邊有數(shù)百或數(shù)千個(gè)連接,并且芯片被構(gòu)建為連接到橋的一半。現(xiàn)在,兩個(gè)芯片都連接到該橋接器,具有通過(guò)硅傳輸數(shù)據(jù)的好處,而不受大型中介層可能帶來(lái)的限制。如果需要更多帶寬,英特爾可以在兩個(gè)芯片之間嵌入多個(gè)橋接器,或者為使用兩個(gè)以上芯片的設(shè)計(jì)嵌入多個(gè)橋接器。此外,該橋的成本遠(yuǎn)低于大型中介層。在 EMIB 的路線圖方面,英特爾將在未來(lái)幾年減少凸點(diǎn)間距。當(dāng)芯片連接到嵌入在基板中的橋時(shí),它們通過(guò)凸塊連接,凸塊之間的距離稱為間距——凸塊間距越小,在同一區(qū)域內(nèi)可以建立的連接越多。這允許芯片增加帶寬或減小橋接尺寸。

●Foveros:首個(gè)3D堆疊解決方案

英特爾于2019年通過(guò)Lakefield推出了其芯片到芯片堆疊技術(shù),3D堆疊在很大程度上與 EMIB 部分中提到的中介層技術(shù)非常相似。通過(guò)將硅片放在彼此的頂部,完整的3D堆疊方式帶來(lái)的好處包括,數(shù)據(jù)路徑更短,功率損耗更少,時(shí)延更低。據(jù)介紹,Meteor Lake是在客戶端產(chǎn)品中實(shí)現(xiàn)Foveros技術(shù)的第二代部署。該產(chǎn)品具有36微米的凸點(diǎn)間距,不同晶片可基于多個(gè)制程節(jié)點(diǎn),熱設(shè)計(jì)功率范圍為5-125W。

●Foveros Omni:第三代Foveros技術(shù)

Foveros Omni允許頂部裸片從基礎(chǔ)裸片懸垂,銅柱從基板一直延伸到頂部裸片以提供電源,通過(guò)高性能3D堆疊技術(shù)為裸片到裸片的互連和模塊化設(shè)計(jì)提供了無(wú)限制的靈活性。Foveros Omni允許裸片分解,將基于不同晶圓制程節(jié)點(diǎn)的多個(gè)頂片與多個(gè)基片混合搭配,預(yù)計(jì)將于2023年用到量產(chǎn)的產(chǎn)品中。

● Foveros Direct:第四代 Foveros

Foveros Direct實(shí)現(xiàn)了向直接銅對(duì)銅鍵合的轉(zhuǎn)變,它可以實(shí)現(xiàn)低電阻互連,并使得從晶圓制成到封裝開始,兩者之間的界限不再那么截然。Foveros Direct實(shí)現(xiàn)了10微米以下的凸點(diǎn)間距,使3D堆疊的互連密度提高了一個(gè)數(shù)量級(jí),為功能性裸片分區(qū)提出了新的概念,這在以前是無(wú)法實(shí)現(xiàn)的。Foveros Direct是對(duì)Foveros Omni的補(bǔ)充,預(yù)計(jì)也將于2023年用到量產(chǎn)的產(chǎn)品中。

英特爾在極紫外光刻(EUV)工藝上的新規(guī)劃

在演講者,英特爾還提到了關(guān)于極紫外光刻(EUV)工藝上的新規(guī)劃,英特爾將成為光刻機(jī)龍頭ASML下一代EUV技術(shù)(High-NA EUV)的主要客戶。英特爾有望率先獲得業(yè)界第一臺(tái)High-NA EUV光刻機(jī),并計(jì)劃在2025年成為首家在生產(chǎn)中實(shí)際采用High-NA EUV的芯片制造商。

據(jù)悉,High-NA EUV光刻機(jī)的目標(biāo)是將制程推進(jìn)到1nm及以下。在ASML的規(guī)劃中,第二代EUV光刻機(jī)的型號(hào)將是NXE:5000系列,其物鏡的NA將提升到0.55,進(jìn)一步提高光刻精度,半導(dǎo)體工藝想要突破1nm制程,就必須靠下一代光刻機(jī)(High-NA EUV)。不過(guò)這也將更加昂貴,曾傳出其成本超過(guò)一架飛機(jī),約3億美元。

High-NA EUV光刻機(jī)的演進(jìn)也并非一帆風(fēng)順,未來(lái)工藝節(jié)點(diǎn)向高數(shù)值孔徑光刻的過(guò)渡不僅需要來(lái)自系統(tǒng)供應(yīng)商(例如 ASML)的巨大工程創(chuàng)新,還需要對(duì)合適的光刻膠材料進(jìn)行高級(jí)開發(fā)。EUV 光刻演化的一個(gè)經(jīng)常被低估的方面是相應(yīng)光刻膠材料的相應(yīng)開發(fā)工作,尋找合適的光刻膠必須與系統(tǒng)開發(fā)同時(shí)進(jìn)行。ASML預(yù)計(jì)將在2022年完成第一臺(tái)High-NA EUV光刻機(jī)系統(tǒng)的驗(yàn)證,并計(jì)劃在2023年交付給客戶。ASML宣布,它現(xiàn)在預(yù)計(jì)High-NA 設(shè)備將在 2025 年或 2026 年(由其客戶)進(jìn)入商業(yè)量產(chǎn)。如三星、臺(tái)積電和英特爾等的客戶們也一直呼吁開發(fā)High-NA 生態(tài)系統(tǒng)以避免延誤。

牽手高通AWS

在客戶方面,英特爾宣布,AWS亞馬遜云將成為首個(gè)采用英特爾代工服務(wù)(IFS)先進(jìn)封裝解決方案的客戶,而高通將成為采用Intel 20A先進(jìn)制程工藝的客戶,這還是開天辟地頭一次。

眾所周知,高通在手機(jī)芯片市場(chǎng)占據(jù)主導(dǎo),該公司將使用英特爾的20A芯片制造工藝,并借助新的晶體管技術(shù)來(lái)降低芯片能耗。不過(guò)這件事還有點(diǎn)遙遠(yuǎn),如果不跳票的話,也要在2024年以后才能看到高通采用英特爾的20A工藝,也就是說(shuō)咱們至少還得等待3年。