盡管大多數(shù)關(guān)于芯片制造的討論都集中在行業(yè)的前沿和極快且復(fù)雜的方面,但現(xiàn)在,對“傳統(tǒng)”工藝技術(shù)的需求比以往任何時候都高,而且數(shù)量也比最新和最好的要大得多。這些傳統(tǒng)工藝構(gòu)成了大多數(shù)現(xiàn)代電子產(chǎn)品的支柱,因此能夠以更低的成本/功耗提供同等技術(shù)對于制造商和芯片設(shè)計人員來說通常是雙贏的。

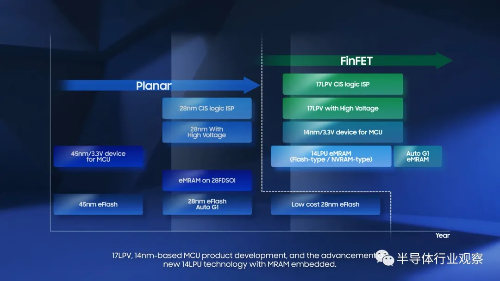

為此,三星宣布推出新的 17 納米工藝節(jié)點,專為仍在使用平面 28 納米工藝但希望利用 14 納米 FinFET 技術(shù)的客戶而設(shè)計。

在現(xiàn)代處理器設(shè)計中,制造工藝節(jié)點帶有一組設(shè)計規(guī)則。要在該節(jié)點上設(shè)計芯片,它必須遵循這些設(shè)計規(guī)則。通常這些規(guī)則會有絕對的最壞情況限制,但如果芯片設(shè)計人員可以利用這些限制來優(yōu)化他們的產(chǎn)品,那么熟悉什么可以做或不可以做是有好處的。

因此,像三星 28 納米這樣使用平面晶體管的工藝,將有一套不同于三星使用 3D FinFET 晶體管的 14 納米的設(shè)計規(guī)則。設(shè)計規(guī)則還考慮了將電源放置在何處、連接性、從晶體管到用于封裝的接觸焊盤的金屬堆疊。

在制造方面,從高層次上講,有兩三個主要部分需要考慮。生產(chǎn)線前端 (FEOL) 是電路制造、設(shè)計晶體管的起點。當(dāng)我們談?wù)撉把丶夹g(shù)時,它是內(nèi)在應(yīng)用的 FEOL 部分,因為我們需要越來越好的工具來在硅中制造越來越小的細(xì)節(jié),以獲得最好的晶體管。一旦 FEOL 用晶體管完成了許多層,晶圓就會移動到線路后端 (BEOL) 以用于其余電路——BEOL 負(fù)責(zé)放置連接線層、電源層和所有輔助連接。BEOL 之后,芯片將進(jìn)行測試、切割(劃片)和封裝。

有時,術(shù)語中間線或中間線末端 (MEOL) 用于具有專為多芯片堆疊設(shè)計的硅通孔 (TSV) 的芯片。

在整體層面上,任何工藝節(jié)點(例如 28nm)的 FEOL 和 BEOL 都有針對這兩個細(xì)分市場的 28nm 版本設(shè)計規(guī)則。有時,制造商會將 FEOL 上的一套設(shè)計規(guī)則與 BEOL 上的另一套設(shè)計規(guī)則結(jié)合起來,以生產(chǎn)具有兩者的某些功能的新產(chǎn)品線。這就是三星在三星代工論壇宣布的新 17nm / 17LPV(低功耗值)工藝正在做的事情。

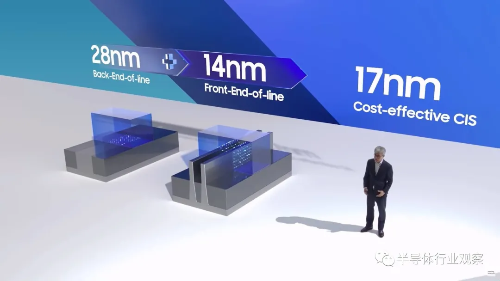

17LPV 將結(jié)合 14nm FEOL,有效地將 14nm FinFET 晶體管與 28nm BEOL 進(jìn)行連接。這意味著客戶可以以額外的成本獲得 FinFET 設(shè)計的性能/功率優(yōu)勢,而無需支付更高密度的 BEOL 的額外成本。最終,芯片尺寸可能仍由較大的節(jié)點 BEOL 決定,但似乎需要較低功率的晶體管。

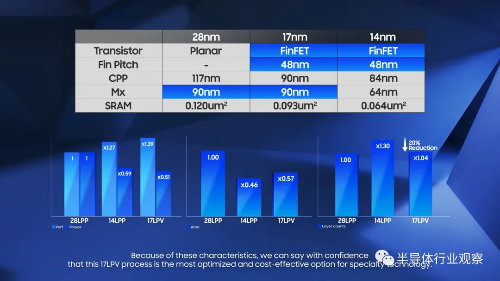

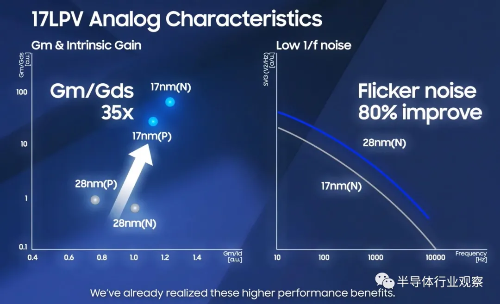

三星聲稱,與傳統(tǒng)的 28 納米工藝相比,17LPV 的芯片面積將減少 43% 以上,性能提高 39%,或功率效率提高 49%。

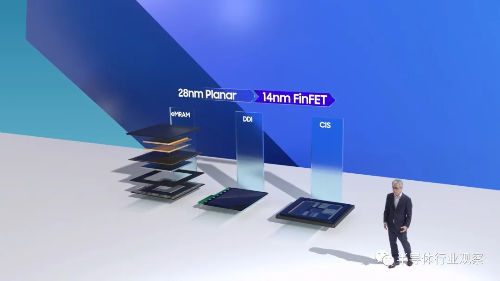

17LPV 的第一個應(yīng)用將是相機(jī)圖像信號處理器,作為三星 CMOS 圖像傳感器產(chǎn)品組合的一部分。這些芯片不一定需要密度,這使得 17LPV 非常適合,但優(yōu)化的功率和成本將使涉及堆疊的專業(yè)技術(shù)受益。

除此之外,三星正在將 17LPV 集成到其高壓產(chǎn)品中,針對需要后端高壓支持并結(jié)合邏輯改進(jìn)的 DDIC/顯示驅(qū)動器。

除了 17LPV,三星代工廠正在創(chuàng)造 14LPU(我們認(rèn)為這仍然是 28nm BEOL + 14nm FEOL)或 Low Power Ultimate,用于嵌入式 MRAM 和微控制器。

這個新節(jié)點的確切時間尺度目前尚未披露,盡管三星代工廠的代表在為這些市場開發(fā)新的專業(yè)工藝解決方案時稱該節(jié)點是公司內(nèi)部“范式轉(zhuǎn)變”的一部分。