世界上最早的全電子化存儲(chǔ)器是1947年在曼徹斯特大學(xué)誕生的威廉姆斯-基爾伯恩管 (Williams-Kilburn tube),其原理是用陰極射線管在屏幕表面上留下記錄數(shù)據(jù)的“點(diǎn)”。從那時(shí)起,計(jì)算機(jī)內(nèi)存開(kāi)始使用磁存儲(chǔ)技術(shù)并經(jīng)歷了數(shù)代演變,相關(guān)系統(tǒng)包括磁鼓存儲(chǔ)器、磁芯存儲(chǔ)器、磁帶驅(qū)動(dòng)器和磁泡存儲(chǔ)器。從1970年代開(kāi)始,主流的集成半導(dǎo)體存儲(chǔ)器則主要分為三類:動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器 (DRAM)、靜態(tài)隨機(jī)存取存儲(chǔ)器 (SRAM) 和閃存。

計(jì)算機(jī)內(nèi)存主要是DRAM和SRAM。二者相比,DRAM的存儲(chǔ)密度更高,而SRAM則具有最快的片上緩存。這兩類半導(dǎo)體存儲(chǔ)器都已經(jīng)歷了數(shù)十年的發(fā)展。DRAM需要周期性刷新才能保持住存儲(chǔ)的數(shù)據(jù),它的發(fā)展主要受存儲(chǔ)密度和成本的影響。SRAM不需要周期性刷新就能鎖存“0”和“1”信號(hào),影響其發(fā)展的主要因素則是單元面積和讀取速度。

DRAM技術(shù)衍生自早前的隨機(jī)存取存儲(chǔ)器 (RAM)。在DRAM出現(xiàn)之前,RAM是大家比較熟悉的存儲(chǔ)器形態(tài),其特點(diǎn)是只能保存正在讀/寫(xiě)的數(shù)據(jù),一旦關(guān)機(jī)斷電就會(huì)擦除所有內(nèi)存。最早的RAM系統(tǒng)由復(fù)雜的電線和磁鐵組成,體積龐大且耗電量大,基本不具備實(shí)用性。IBM的羅伯特·丹納德 (Robert Dennard) 改變了這一情況,他發(fā)明了使用單個(gè)晶體管和存儲(chǔ)電容器的RAM存儲(chǔ)單元。正是基于他的這項(xiàng)杰出發(fā)明,我們才逐漸發(fā)展出了在現(xiàn)代計(jì)算機(jī)中能容納十億個(gè)甚至更多RAM單元的單芯片。

半導(dǎo)體存儲(chǔ)器面臨的挑戰(zhàn)及應(yīng)對(duì)辦法

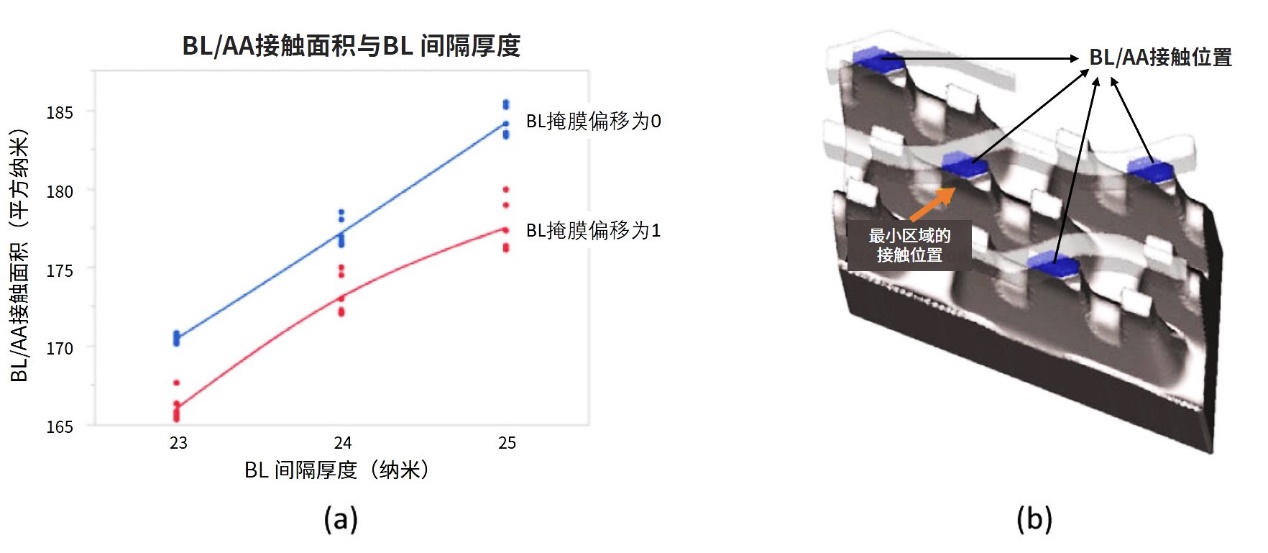

如今,DRAM技術(shù)的發(fā)展面臨很多和CPU相同的挑戰(zhàn),包括多重圖形化、鄰近效應(yīng)和存儲(chǔ)節(jié)點(diǎn)泄漏等。DRAM的開(kāi)發(fā)需要精確的建模才能預(yù)測(cè)前述問(wèn)題的影響并做相應(yīng)的優(yōu)化來(lái)避免良率受損。舉例來(lái)說(shuō),在確定位線 (BL) 到有源區(qū) (AA) 接觸面積時(shí)就必須特別注意位線芯軸間隔和掩膜偏移,稍有疏忽就可能導(dǎo)致良率問(wèn)題。

僅依靠基于晶圓的實(shí)驗(yàn)很難找出晶圓級(jí)失效的原因并確定與之相關(guān)的工藝參數(shù)。在工藝變化研究中制造測(cè)試晶圓并測(cè)量晶圓上的最終接觸面積,費(fèi)時(shí)且成本較高。先進(jìn)的工藝建模技術(shù)能幫我們解決前述問(wèn)題。通過(guò)對(duì)BL間隔層厚度變化和BL掩膜位移同時(shí)建模,基于DoE(實(shí)驗(yàn)設(shè)計(jì))統(tǒng)計(jì)變化研究,可以確定最小接觸區(qū)域。基于前述研究的結(jié)果,結(jié)合自帶的結(jié)構(gòu)搜索/DRC功能就可以確定具體芯片上的最小接觸位置和區(qū)域。SEMulator3D?就是一個(gè)能完成上述研究的工藝建模平臺(tái)。基于該平臺(tái)的工藝變化研究能夠幫助我們發(fā)現(xiàn)與BL芯軸間隔厚度和掩膜轉(zhuǎn)換相關(guān)的潛在問(wèn)題。圖1 (a) 展示的就是用SEMulator3D檢查BL間隔厚度和掩膜轉(zhuǎn)換對(duì)BL/AA接觸面積的影響,而圖1 (b) 則顯示了最小接觸區(qū)域在芯片上的位置。

圖1. (a) BL/AA接觸面積與BL間隔厚度和掩膜偏移的關(guān)系;(b) 最小接觸區(qū)域及其位置。

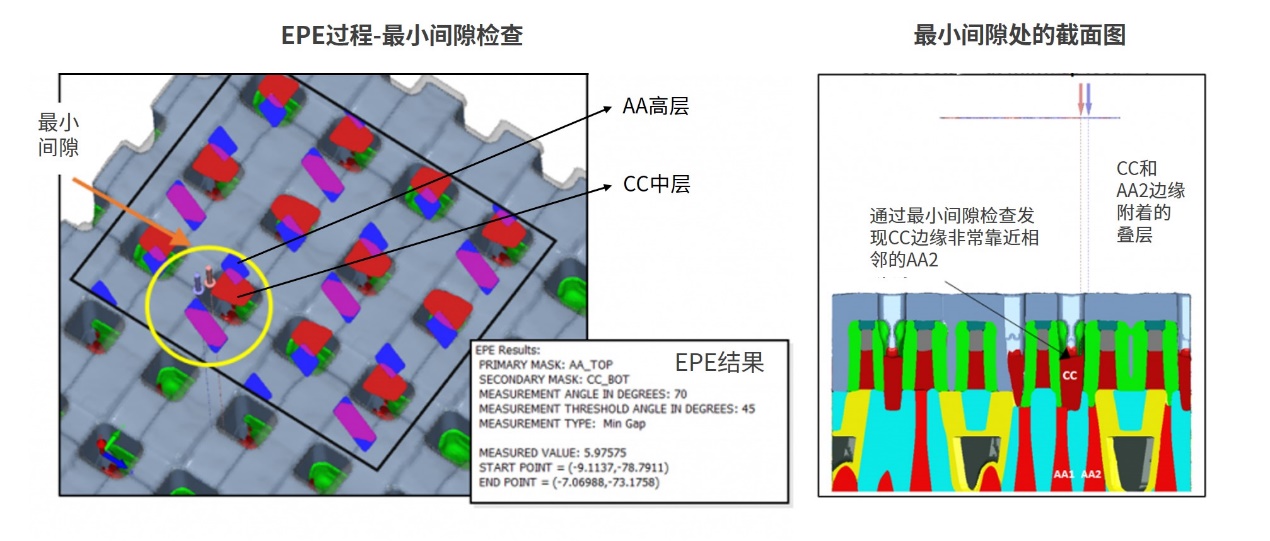

DRAM工藝開(kāi)發(fā)還要注意存儲(chǔ)節(jié)點(diǎn)與相鄰有源區(qū)的距離,因?yàn)檫^(guò)度接近會(huì)導(dǎo)致設(shè)備短路。一旦發(fā)生短路,其背后的根本原因很難確定。但不解決的話,這些問(wèn)題到了開(kāi)發(fā)后期可能導(dǎo)致嚴(yán)重的可靠性與良率問(wèn)題。若能在試產(chǎn)之前通過(guò)準(zhǔn)確地建模確定電容器觸點(diǎn)與AA在不同z位置的最小間隙,我們就有可能避免前述的嚴(yán)重后果。圖2展示的是在工藝建模過(guò)程中確定的BL到AA接觸區(qū)域,其中高亮部分就是需要通過(guò)工藝或設(shè)計(jì)變更解決的最小間隙問(wèn)題。通過(guò)圖中示例可以看出工藝步驟之間復(fù)雜的相互影響并最終影響到DRAM的可靠性和良率,因此通過(guò)準(zhǔn)確的建模來(lái)確定這些影響是很有意義的。

圖2. 晶圓制造工藝的虛擬建模 (SEMulator3D),圖中展示的存儲(chǔ)節(jié)點(diǎn)觸點(diǎn)與AA之間可能存在短路。

支持多次擦除和重復(fù)編程的閃存出現(xiàn)于1984年,目前它已被用于各種消費(fèi)類設(shè)備、企業(yè)系統(tǒng)和工業(yè)應(yīng)用的存儲(chǔ)和數(shù)據(jù)傳輸。閃存可以長(zhǎng)期保存數(shù)據(jù),即使關(guān)機(jī)斷電也不受影響,其制造技術(shù)目前已經(jīng)從2D轉(zhuǎn)向3D(即3D NAND),以增加存儲(chǔ)密度。

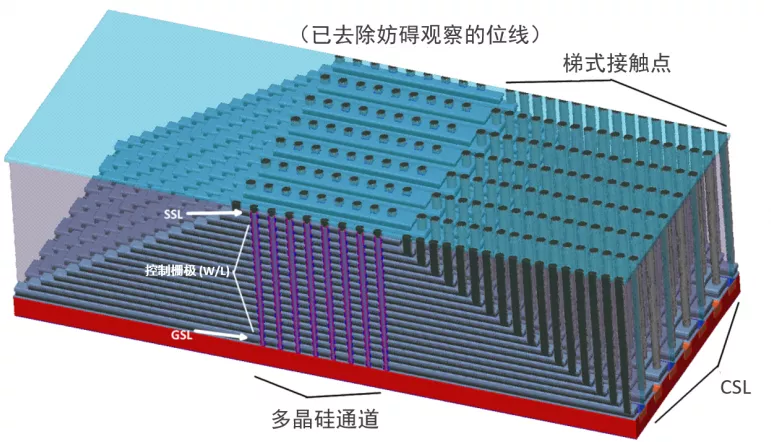

單層3D NAND結(jié)構(gòu)的刻蝕非常復(fù)雜,因?yàn)楦呱顚挶缺仨氃谝唤M交替的材料中刻蝕,同時(shí)還要避免刻蝕孔發(fā)生彎曲和傾斜,并且需要專門刻蝕出用來(lái)分離相鄰存儲(chǔ)單元的“狹縫”。完整3D NAND結(jié)構(gòu)的刻蝕甚至要更復(fù)雜一些,因?yàn)槠渲羞€包含了形成字線 (WL) 觸點(diǎn)所必需的“梯式”刻蝕。圖3展示的是用SEMulator3D建模的完整3D NAND陣列,可以看出最先進(jìn)的3D NAND存儲(chǔ)器結(jié)構(gòu)相當(dāng)復(fù)雜,而且這還只是單層結(jié)構(gòu)。

圖3. 使用SEMulator3D建模的單層3D NAND存儲(chǔ)單元。

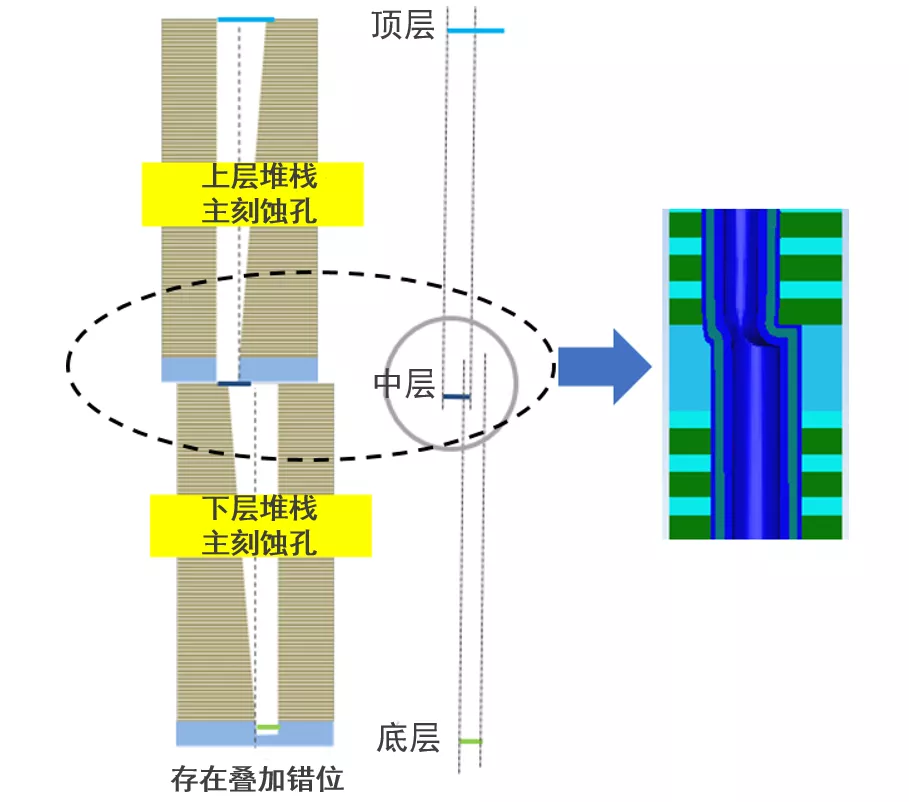

工藝的復(fù)雜性在2D向3D閃存結(jié)構(gòu)的過(guò)渡中急劇提升,原因在于3D結(jié)構(gòu)需要多層溝道的刻蝕。當(dāng)今的大多數(shù)3D NAND存儲(chǔ)器都有兩層,這就意味著可能出現(xiàn)頂層與底層錯(cuò)位問(wèn)題。圖4展示的就是多層3D NAND溝道刻蝕面臨的問(wèn)題和挑戰(zhàn)。

圖4. SEMulator3D輸出結(jié)果,其中展示的是層錯(cuò)位問(wèn)題和其導(dǎo)致的溝道刻蝕偏移。

這就是層錯(cuò)位和其導(dǎo)致的溝道刻蝕偏移。這種錯(cuò)位可能是工藝差異導(dǎo)致的,并且是任何3D NAND工藝開(kāi)發(fā)都繞不開(kāi)的問(wèn)題。從圖中示例可以看出,層與層之間的一致性對(duì)多層3D NAND存儲(chǔ)單元的結(jié)構(gòu)質(zhì)量有非常重大的影響。和DRAM的情況一樣,我們可以在SEMulator3D系統(tǒng)中針對(duì)3D NAND的層錯(cuò)位問(wèn)題做DoE統(tǒng)計(jì)變化研究,且只需要根據(jù)分析結(jié)果采取糾正措施即可,無(wú)需再花費(fèi)時(shí)間和金錢去進(jìn)行晶圓測(cè)試。