隨著各種各樣新的封裝類(lèi)型逐漸成為主流,先進(jìn)封裝互連技術(shù)正面臨發(fā)展的轉(zhuǎn)折點(diǎn)。一些供應(yīng)商選擇擴(kuò)展傳統(tǒng)凸塊封裝方法,而另一些則推出新的封裝技術(shù)取而代之。

在任何情況下,目標(biāo)都是在需處理的數(shù)據(jù)量增加時(shí)確保IC封裝組件之間的信號(hào)完整性。但隨著設(shè)備不斷縮小,而越來(lái)越多的組件被添加到先進(jìn)封裝中來(lái)處理、移動(dòng)和存儲(chǔ)更多數(shù)據(jù),將需要具有更多I/O的新技術(shù)。因此,盡管在可預(yù)見(jiàn)的未來(lái)中仍將使用傳統(tǒng)的焊球和/或銅微凸塊,但那些增強(qiáng)或取代傳統(tǒng)互連技術(shù)、增加I/O數(shù)量并提供更多微縮空間的新技術(shù)正在研發(fā)中。

一如既往,尺寸和成本是決定性因素。銅微凸塊比焊球/凸塊更小,可在封裝中實(shí)現(xiàn)更多 I/O。當(dāng)前,先進(jìn)封裝技術(shù)的微凸塊間距最小達(dá)40μm,這相當(dāng)于20μm至25μm的凸塊尺寸,裸晶上相鄰?fù)箟K之間的間距為15μm。

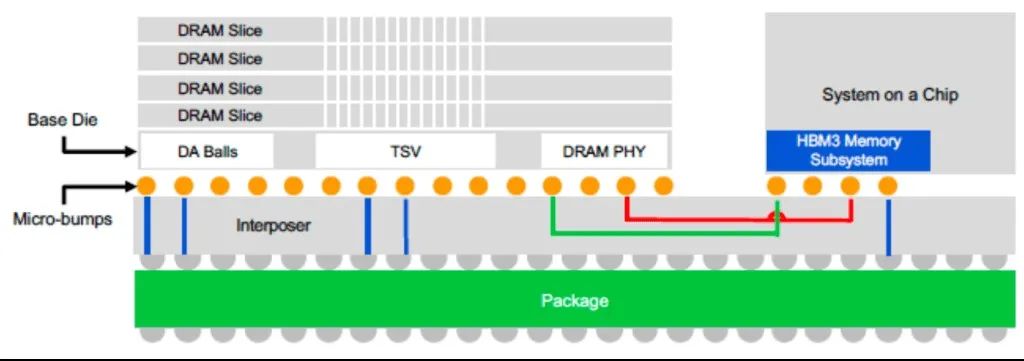

圖 1:具有HBM3內(nèi)存的2.5D/3D系統(tǒng)架構(gòu)。銅微凸塊連接中介層和基片。微凸塊也用于芯片到芯片的連接。圖源:Rambus

對(duì)于小于40μm的間距,客戶在封裝上有另外一些選擇。首先,他們可以使用現(xiàn)有的凸塊技術(shù)研發(fā)新的封裝技術(shù),以突破技術(shù)瓶頸,將當(dāng)前40μm間距向下微縮至10μm。另一種選擇是被稱(chēng)為銅混合鍵合的新技術(shù)。在混合鍵合技術(shù)中,裸晶的連接并非通過(guò)封裝中的凸塊。相反,該技術(shù)利用微小的銅對(duì)銅互連,實(shí)現(xiàn)比傳統(tǒng)封裝具有更多I/O的更窄間距封裝。對(duì)于封裝技術(shù)來(lái)說(shuō),混合鍵合的間距至少在10μm及以下。

AMD已經(jīng)計(jì)劃在未來(lái)的處理器產(chǎn)品中采用混合鍵合技術(shù)。該公司正在使用臺(tái)積電的混合鍵合技術(shù)。其他代工廠也在研究混合鍵合。但并非所有封裝都需要混合鍵合,且該技術(shù)針對(duì)的是高端產(chǎn)品。即便如此,混合鍵合仍然是一個(gè)昂貴且困難的工藝。

英特爾和其他公司并沒(méi)有轉(zhuǎn)向混合鍵合,而是希望擴(kuò)展現(xiàn)有的凸點(diǎn)互連技術(shù),并圍繞這些技術(shù)開(kāi)發(fā)間距小于40μm的封裝。“在保持與現(xiàn)有硅和封裝技術(shù)兼容的同時(shí),利用現(xiàn)有的基礎(chǔ)設(shè)施,將焊料微凸點(diǎn)互連微縮至更小的間距可能仍然是有利的,”英特爾封裝開(kāi)發(fā)工程師Zhaozhi Li在最近的ECTC大會(huì)上表示。

英特爾描述了一種將凸點(diǎn)間距縮小或減小到10μm的方法。一些OSAT也在研究更窄間距的銅凸點(diǎn)技術(shù)。但是,隨著焊料/銅凸點(diǎn)技術(shù)逐漸向更窄間距微縮,面臨的挑戰(zhàn)也隨之增多。對(duì)于新材料、新工藝和新工具的需求越來(lái)越多。盡管如此,下一代凸塊技術(shù)和混合鍵合都將在該行業(yè)中發(fā)揮重要作用,推動(dòng)著技術(shù)朝著更多先進(jìn)封裝和Chiplet模型發(fā)展。對(duì)于Chiplet,芯片制造商可能在庫(kù)中擁有模塊化裸晶菜單。然后,客戶可以將芯片混合搭配并集成到現(xiàn)有封裝類(lèi)型或新架構(gòu)中。

Chiplet正在成為推進(jìn)芯片設(shè)計(jì)的替代方案。傳統(tǒng)上,為了推進(jìn)設(shè)計(jì),供應(yīng)商會(huì)開(kāi)發(fā)片上系統(tǒng) (SoC) 并在每一代設(shè)備上集成更多功能。但隨著摩爾定律延緩,芯片集成變得越來(lái)越困難和昂貴。雖然這種方法仍然是新設(shè)計(jì)的一種選擇,但Chiplet有望成為下一代芯片設(shè)計(jì)趨勢(shì)。混合鍵合或縮放凸塊是Chiplet拼圖中的關(guān)鍵部分。

封裝技術(shù)概述

IC封裝將裸晶包裹在封閉式單元中,可保護(hù)器件免受損壞。封裝還可以提高裸晶的性能。

“業(yè)界正在加大對(duì)先進(jìn)封裝的投資,并致力于提高系統(tǒng)級(jí)互連密度、降低功耗、實(shí)現(xiàn)更小的外形尺寸,并通過(guò)縮小封裝級(jí)間距,以及將更多功能集成到單個(gè)封裝中來(lái)降低成本。” Brewer Science的高級(jí)項(xiàng)目經(jīng)理Xiao Liu表示。該行業(yè)已開(kāi)發(fā)出超過(guò)1000種不同的封裝技術(shù)。客戶可根據(jù)給定的應(yīng)用程序進(jìn)行選擇。

按照互連類(lèi)型來(lái)細(xì)分封裝市場(chǎng),包括引線鍵合、倒裝芯片、晶圓級(jí)封裝 (WLP) 和硅通孔 (TSV)。TSV提供最多的I/O,其次是WLP、倒裝芯片和引線鍵合。

據(jù)TechSearch稱(chēng),大約75%到80%的封裝基于引線鍵合。焊線機(jī)使用細(xì)線將一個(gè)芯片縫合到另一個(gè)芯片或基板上。引線鍵合機(jī)用于制造商品和中檔封裝以及內(nèi)存堆棧。

倒裝芯片在芯片頂部形成微小的焊料或銅凸點(diǎn)。然后將器件翻轉(zhuǎn)并安裝在單獨(dú)的裸晶或板上。凸塊落在銅焊盤(pán)上,形成電氣連接。

在此過(guò)程中,使用高速倒裝芯片鍵合機(jī)連接凸塊裸晶,然后進(jìn)行大規(guī)模回流工藝。“許多倒裝芯片設(shè)備不需要窄間距。它們可以通過(guò)大規(guī)模回流來(lái)完成,”Kulicke & Soffa (K&S) 的CTO Bob Chylak表示。“倒裝芯片鍵合機(jī)取出芯片,將焊球浸入助焊劑中,然后將它們放置在PCB 上。然后PCB通過(guò)回流烘箱,回流烘箱將焊料熔化,然后將其固化。”

倒裝芯片用于開(kāi)發(fā)許多封裝類(lèi)型,例如球柵陣列(BGA)。圖形芯片和處理器采用BGA封裝。在倒裝芯片中,芯片上的凸點(diǎn)間距范圍從300μm到50μm。

“我們?nèi)匀豢吹?40μm至150μm的寬間距封裝。該技術(shù)仍然是發(fā)展主流,并且不會(huì)很快改變,”QP Technologies的母公司Promex CTO Annette Teng認(rèn)為。“我們開(kāi)始看到一些 110μm到120μm的封裝技術(shù)。40μm以下仍處于研發(fā)階段。”

同時(shí),扇出封裝是一種晶圓級(jí)封裝。在扇出封裝的一個(gè)示例中,DRAM裸晶堆疊在邏輯芯片上。

TSV用于先進(jìn)2.5D/3D封裝,通常用于高端系統(tǒng)。在 2.5D/3D封裝中,裸晶堆疊或并排放置在中介層的頂部,中介層包含TSV。TSV提供了從裸晶到電路板的電氣連接。在2.5D的一個(gè)示例中,ASIC和高帶寬存儲(chǔ)器(HBM)并排放置在中介層上。(HBM是DRAM內(nèi)存堆棧。)

2.5D封裝的焊球位于基板底部,將封裝與電路板進(jìn)行電氣連接。C4凸點(diǎn)是較小的結(jié)構(gòu),將基板連接到中介層。較小的銅微凸塊將中介層連接到基片上。在HBM中,DRAM裸晶使用 40μm間距的微小微凸塊連接。

為了堆疊和連接這些封裝中的裸晶,熱壓鍵合機(jī)(TCB)系統(tǒng)拾取裸晶并將凸塊與另一個(gè)裸晶的凸塊對(duì)齊。該系統(tǒng)使用壓力和熱能來(lái)鍵合凸塊。

展望未來(lái),供應(yīng)商希望開(kāi)發(fā)凸點(diǎn)間距低于40μm的HBM模塊和3D封裝,從而實(shí)現(xiàn)更多的 I/O和帶寬。芯片客戶可以通過(guò)使用更精細(xì)的凸點(diǎn)或使用銅混合鍵合來(lái)開(kāi)發(fā)先進(jìn)封裝。有些客戶則可能對(duì)不同封裝同時(shí)使用這兩種方法。

預(yù)計(jì)銅凸點(diǎn)的間距將從40μm微縮至10μm。然后,封裝技術(shù)逐漸走向混合鍵合,從而實(shí)現(xiàn) 10μm及以下間距的互連。但并非所有封裝廠都可以開(kāi)發(fā)混合鍵合。對(duì)于大多數(shù)OSAT來(lái)說(shuō),這項(xiàng)技術(shù)成本過(guò)高,需要昂貴的半導(dǎo)體晶圓廠來(lái)實(shí)現(xiàn)這些工藝。

精選代工廠是供應(yīng)商僅有的能夠?qū)⒒旌湘I合投入生產(chǎn)的方法。即便如此,用于封裝的混合鍵合仍然具有挑戰(zhàn)性。“混合鍵合面臨的巨大挑戰(zhàn)是晶圓表面清潔度、晶圓翹曲以及芯片中銅和介電材料之間的梯度,”UMC技術(shù)總監(jiān)Tony Lin表示。

混合鍵合仍面臨很多問(wèn)題。“未來(lái)幾年肯定會(huì)推出具有非常窄間距(使用混合鍵合)的產(chǎn)品。” Amkor高級(jí)封裝開(kāi)發(fā)和集成副總裁Mike Kelly表示。“這是一個(gè)昂貴的工藝,并且未來(lái)幾年可能仍將是超高性能的領(lǐng)軍者。”

凸塊微縮

考慮到這一點(diǎn),英特爾和其他公司正在使用低于40μm的傳統(tǒng)微凸塊開(kāi)發(fā)新的先進(jìn)封裝技術(shù)。供應(yīng)商還在研究下一代HBM技術(shù)HBM3,其凸點(diǎn)密度是HBM2e的兩倍。HBM3支持 8.4Gbps的帶寬,而HBM2e的帶寬為3.6Gbps。

微縮微凸點(diǎn)具有以下幾點(diǎn)優(yōu)勢(shì)。首先,它利用了現(xiàn)有的焊料/銅凸點(diǎn)基礎(chǔ)設(shè)施。其次,幾家供應(yīng)商正在研究窄間距凸點(diǎn)技術(shù),例如Amkor、ASE、Intel、JCET、三星和臺(tái)積電。

開(kāi)發(fā)帶有凸塊的封裝技術(shù)并非新鮮事。在1960年,倒裝芯片封裝作為一種組裝技術(shù)出現(xiàn)。最初,倒裝芯片工藝涉及到C4(受控塌陷芯片連接)凸點(diǎn)的形成,其直徑范圍為75μm至200μm。

C4凸塊仍在封裝中使用,但它們是寬間距結(jié)構(gòu)。因此,從2006年的65nm節(jié)點(diǎn)開(kāi)始,英特爾和其他公司逐漸遷移到更小的C4凸點(diǎn)版本,稱(chēng)為銅微凸點(diǎn)/柱,有時(shí)也稱(chēng)為C2凸點(diǎn)。最初的銅微凸點(diǎn)直徑為25μm。

銅凸點(diǎn)由帶有薄鎳擴(kuò)散阻擋層的銅柱和錫銀焊帽組成。“C2凸點(diǎn)提供比C4凸點(diǎn)更好的熱性能和電氣性能。這是因?yàn)镃u的熱導(dǎo)率和電阻率優(yōu)于焊料,” Unimicron CTO John Lau在他的新書(shū)《半導(dǎo)體先進(jìn)封裝》(Springer,2021年)中表示。

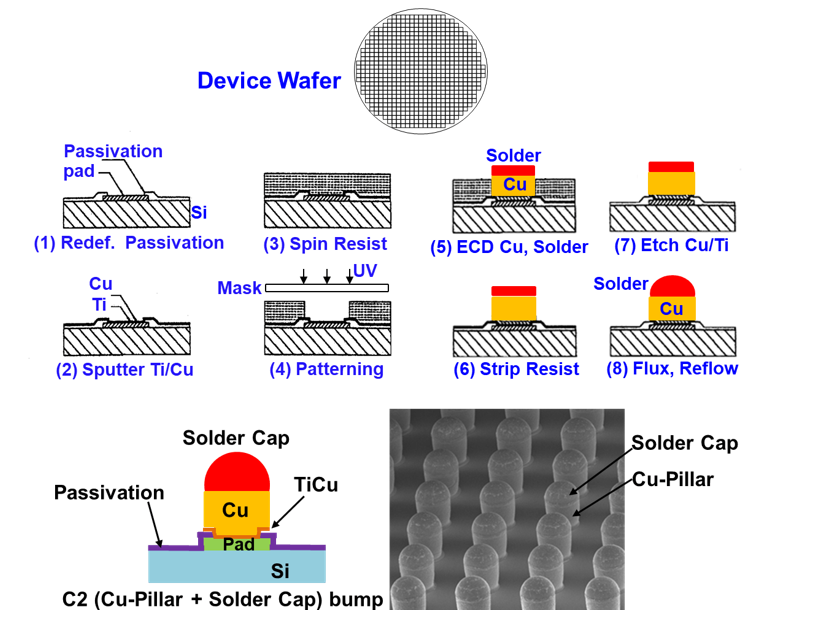

為了制造更小的銅微凸塊,該工藝類(lèi)似于C4流程。首先,芯片在晶圓廠的晶圓上加工。然后在晶片底部形成凸塊。

為此,使用沉積法通過(guò)凸點(diǎn)下金屬化層(UBM) 沉積表面。然后,在UBM上應(yīng)用一種稱(chēng)為光刻膠的光敏材料。使用光刻系統(tǒng)在抗蝕劑頂部圖案化預(yù)定凸塊尺寸。該圖案被蝕刻,形成一個(gè)小間隙。

使用電化學(xué)沉積(ECD)系統(tǒng),填充間隙或?qū)㈤g隙鍍銅。剝離抗蝕劑并蝕刻結(jié)構(gòu)。該結(jié)構(gòu)在烘箱中回流或加熱,形成凸塊。

圖 2:微凸點(diǎn)工藝流程。圖源:John Lau,Unimicron

當(dāng)今最先進(jìn)的微凸塊使用40μm間距和20μm至25μm之間的凸塊尺寸。據(jù)DuPont稱(chēng),凸塊尺寸約為凸塊間距的50%。

未來(lái)的封裝將轉(zhuǎn)向具有更窄間距的更小銅凸點(diǎn)。“我們看到柱狀凸塊尺寸已經(jīng)有18μm間距、9μm直徑和20μm高。300毫米晶圓上有大約2億個(gè)凸點(diǎn),間距為18微米。”O(jiān)nto Innovation產(chǎn)品營(yíng)銷(xiāo)經(jīng)理Woo Young Han表示。“我們聽(tīng)說(shuō)一位客戶聲稱(chēng)實(shí)現(xiàn)10μm間距、5μm直徑和10μm高。在10μm間距的300mm晶圓上大約有5億個(gè)凸點(diǎn)。5μm的凸點(diǎn)直徑是我們從客戶那里聽(tīng)到的最小的直徑。”

向更小的凸塊研究會(huì)帶來(lái)一些挑戰(zhàn)。“隨著焊料凸點(diǎn)間距的縮小,凸點(diǎn)高度變短,可用于鍵合的凸點(diǎn)表面減少,芯片級(jí)凸點(diǎn)數(shù)量增加,”Han表示。“隨著凸點(diǎn)數(shù)量的增加,凸點(diǎn)尺寸的減少轉(zhuǎn)化為更小的錯(cuò)誤余量,以建立可靠的電氣連接。隨著凸塊間距的縮小,芯片級(jí)凸塊共面性、凸塊表面粗糙度和凸塊硬度變得越來(lái)越重要。鍵合過(guò)程中使用的溫度、時(shí)間和壓力取決于芯片級(jí)凸塊共面性、凸塊表面粗糙度和凸塊硬度的質(zhì)量。在鍵合過(guò)程中使用更高的溫度、更長(zhǎng)的時(shí)間和更大的壓力會(huì)增加成本和損壞芯片的風(fēng)險(xiǎn)。”

所有這些都在整個(gè)制造流程中提出了幾個(gè)挑戰(zhàn)。以蝕刻為例。“銅柱和焊料凸點(diǎn)的直徑更小。由于蝕刻導(dǎo)致的下切變得越來(lái)越重要,” Unimicron的Lau表示。

ECD電鍍工藝也面臨挑戰(zhàn)。“隨著客戶瞄準(zhǔn)下一代微凸點(diǎn)解決方案,電鍍均勻性和共面性控制變得越來(lái)越重要,”Lam Research董事總經(jīng)理Manish Ranjan表示。“Lam的電鍍槽設(shè)計(jì)可提供超高均勻?qū)α?以實(shí)現(xiàn)快速且均勻的沉積速率。此外,專(zhuān)有技術(shù)解決方案,例如先進(jìn)的表面處理能力,可實(shí)現(xiàn)最低的缺陷性能。”

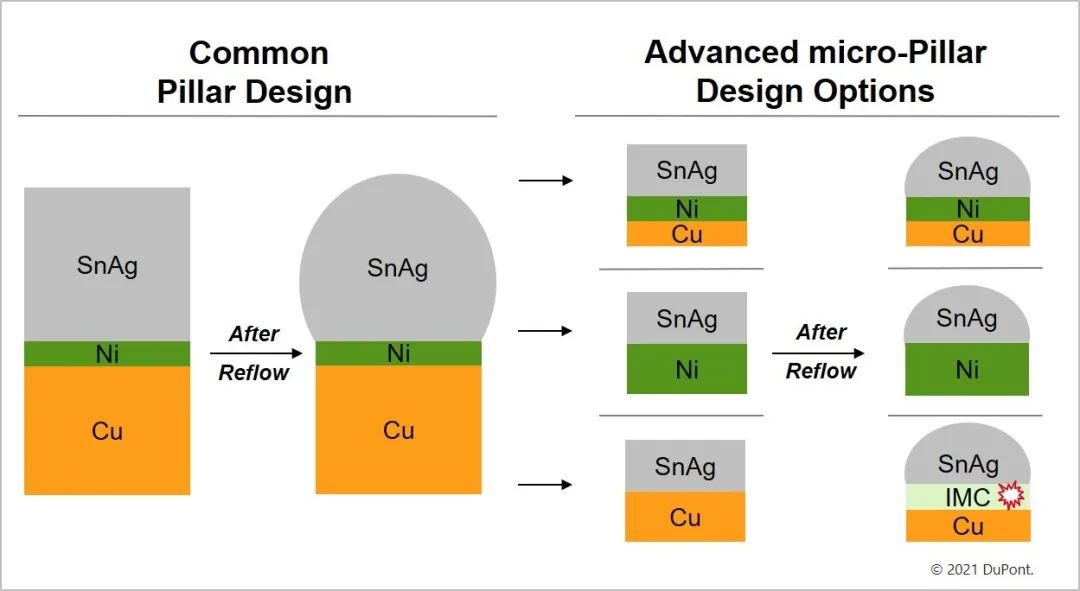

最重要的是,向更小凸塊的轉(zhuǎn)變也可能需要全新且差異性的凸塊結(jié)構(gòu)。考慮一個(gè)間距為40μm、凸塊高度為25μm 的微凸塊。在這個(gè)凸塊中,銅結(jié)構(gòu)的高度是15μm,而鎳是5μm。剩下的部分是焊帽。

“在這種結(jié)構(gòu)中,銅比鎳大,”DuPont先進(jìn)封裝技術(shù)全球營(yíng)銷(xiāo)負(fù)責(zé)人Shashi Gupta表示。“當(dāng)你采用更窄的間距時(shí),銅的高度將開(kāi)始縮小。在某些時(shí)候,銅的厚度和鎳的厚度或多或少相差不大。焊帽也在縮小。”

在一個(gè)假設(shè)示例中,未來(lái)的銅柱可能具有3μm的銅結(jié)構(gòu)、3μm的鎳阻擋層和5μm的焊帽。“關(guān)鍵是鎳和銅非常相似。在這種厚度下,要在整個(gè)晶圓上保持均勻性是一項(xiàng)挑戰(zhàn),”Gupta表示。“因此,您可能需要考慮在焊料在頂部的柱狀結(jié)構(gòu)中選擇一種金屬。”

換句話說(shuō),在更窄間距的封裝中,您可能有一個(gè)帶有焊帽的微小銅柱,或帶有焊帽的鎳柱。“出于成本、產(chǎn)量或性能方面的考慮,通常使用銅/錫-銀或鎳/錫-銀結(jié)構(gòu)而不是銅/鎳/錫-銀結(jié)構(gòu),”Gupta稱(chēng)。“這將有助于優(yōu)化成本結(jié)構(gòu),也更容易控制質(zhì)量。”

與鎳相比,銅是一種更佳的金屬,但銅也有一些缺點(diǎn)。鎳的導(dǎo)電性較低,但鎳凸點(diǎn)也可能起作用。這仍處于研發(fā)階段,尚不清楚鎳在生產(chǎn)中如何應(yīng)用。

盡管如此,在未來(lái)的工藝中,銅凸塊將只需要鍍銅工藝,而鎳凸塊將使用鍍鎳工藝。

這反過(guò)來(lái)又簡(jiǎn)化了電鍍過(guò)程。“與鍍兩層(先鍍銅,再鍍鎳)相比,鍍單層銅或鎳更容易。然后將相同的焊料以減少的體積量放在其上,”Gupta說(shuō)。

最終,兩種不同的凸塊金屬結(jié)合在一起,并擴(kuò)散到彼此的晶界中。這稱(chēng)為金屬間化合物 (IMC) 層。在某些情況下,IMC 很穩(wěn)固。另一些情況下,IMC較脆弱,導(dǎo)致連接失效。

IMC是可能出現(xiàn)問(wèn)題的地方。“對(duì)于銅/錫-銀凸點(diǎn)結(jié)構(gòu),焊料直接沉積在銅柱上而沒(méi)有鎳阻擋層,在回流期間可能會(huì)形成金屬間化合物 (IMC) 層,”Gupta表示。“IMC層可能會(huì)在老化或加熱過(guò)程中繼續(xù)生長(zhǎng),從而對(duì)焊點(diǎn)可靠性和導(dǎo)電性產(chǎn)生負(fù)面影響。相比之下,均勻鍍鎳代替銅柱可有效限制廣泛的 IMC生長(zhǎng),并提供出色的阻擋能力、可焊性和其他特性,這些特性對(duì)于一致的晶圓制造至關(guān)重要。從工藝角度來(lái)看,更新的鎳基電鍍選項(xiàng)也是可持續(xù)的。”

圖 3:通用支柱設(shè)計(jì)和先進(jìn)微支柱設(shè)計(jì)。圖源:DuPont

凸點(diǎn)鍵合

制造微小的凸塊極具挑戰(zhàn)性。在更窄的間距下將它們鍵合起來(lái)也很困難。

通過(guò)大規(guī)模回流的傳統(tǒng)倒裝芯片鍵合在更窄的間距上面臨挑戰(zhàn)。“標(biāo)準(zhǔn)回流工藝是在用于倒裝芯片和系統(tǒng)級(jí)封裝的烘箱中進(jìn)行的。該解決方案以數(shù)量與低價(jià)著稱(chēng),”JCET現(xiàn)場(chǎng)應(yīng)用工程高級(jí)總監(jiān)Nokibul Islam表示。“令人擔(dān)憂的是,可能會(huì)出現(xiàn)基板和芯片之間的整體熱膨脹系數(shù)不匹配,從而導(dǎo)致更高的翹曲和芯片移位。”

傳統(tǒng)的倒裝芯片工藝可以應(yīng)用到50μm或40μm的間距,但再往下走就可能會(huì)出現(xiàn)可靠性問(wèn)題。這就是TCB適用的地方。早在幾年前,TCB已經(jīng)推出,用于先進(jìn)的窄間距鍵合應(yīng)用。一些供應(yīng)商在銷(xiāo)售TCB工具。

TCB工具用于鍵合具有間距在40μm至50μm及以下微小凸塊的裸晶,適用于芯片到晶圓和芯片到基板的應(yīng)用。就目前情況而言,TCB微縮至10μm間距。

“熱壓鍵合是局部回流,”K&S的Chylak表示。“熱壓焊機(jī)不是加熱整個(gè)電路板及其上的所有芯片,而是像普通倒裝芯片一樣抓住芯片,并將其浸入助焊劑中,然后將其放置在PCB上。鍵合機(jī)頂部有一個(gè)加熱器。加熱至超過(guò)將芯片固定到位的焊料熔點(diǎn)。然后冷卻下來(lái),使焊料凝固。”

助焊劑是用來(lái)去除試圖鍵合的銅墊上的氧化物。在化學(xué)反應(yīng)中,助焊劑將會(huì)溶解氧化物。

然而,TCB是一個(gè)相對(duì)緩慢的過(guò)程,存在一些助焊劑清潔問(wèn)題。“倒裝芯片和熱壓鍵合都存在問(wèn)題。浸入凸塊的助焊劑必須是清潔的。”Chylak表示。

業(yè)界使用清潔系統(tǒng)來(lái)清除封裝中的助焊劑。這適用于寬間距應(yīng)用,但此過(guò)程需要時(shí)間來(lái)清潔窄間距封裝的助焊劑。

在另一個(gè)可能的解決方案中,業(yè)界開(kāi)發(fā)了“免清洗助焊劑”材料。這些材料并不總是有效。如果過(guò)程中出現(xiàn)助焊劑,則很難清潔。

因此,K&S正在開(kāi)發(fā)無(wú)助焊劑TCB技術(shù)。在TCB工具中,K&S 結(jié)合了原位甲酸蒸汽輸送系統(tǒng)和腔室。“我們可以放一層甲酸蒸汽,它可以在沒(méi)有助焊劑的情況下清潔表面,然后我們進(jìn)行鍵合。這是我們開(kāi)發(fā)的一項(xiàng)新技術(shù),無(wú)需助焊劑即可鍵合。這是對(duì)TCB的生產(chǎn)力和可靠性的改進(jìn),” Chylak表示。

還有其他解決方案。在ECTC上,作為ASE的一部分,Siliconware描述了一種開(kāi)發(fā)具有20μm 凸點(diǎn)間距的3D封裝的方法,旨在堆疊和鍵合兩個(gè)薄芯片。共有兩種測(cè)試方案。一種使用帶有毛細(xì)管底部填充 (TCCUF) 的TCB。另一個(gè)使用帶有非導(dǎo)電膏 (TCNCP) 的TCB。

“總而言之,我們已經(jīng)成功地表征和開(kāi)發(fā)了使用20?m凸點(diǎn)間距的3D封裝技術(shù)。這種封裝技術(shù)可以通過(guò)標(biāo)準(zhǔn)的裸晶貼裝和回流,以及使用NCF的熱壓焊來(lái)實(shí)現(xiàn),”Siliconware的技術(shù)經(jīng)理Mu Hsuan Chan表示。

與此同時(shí),英特爾找到了一種方法來(lái)微縮20μm和10μm間距的微凸塊。英特爾開(kāi)發(fā)了帶有微小凸塊的裸晶,并通過(guò)對(duì)準(zhǔn)精度優(yōu)于2.1μm 的TCB工具將它們鍵合起來(lái)。

“數(shù)據(jù)表明,使用功能強(qiáng)大的TCB工具和緊密的鍵合工藝控制,將Cu/SnAg微凸塊配置在20μm 間距下是可行的。然而,在10μm處,為了保留焊料以滿足TCB鍵合的需要,并獲得足夠的鍵合工藝余量,需要放置一定的焊料/Cu擴(kuò)散阻擋金屬。”英特爾的 Li 說(shuō)。

總結(jié)

最終,英特爾和其他公司將采用混合鍵合技術(shù)。臺(tái)積電希望在這項(xiàng)技術(shù)上早日取得突破性進(jìn)展。

但無(wú)論是窄間距封裝還是寬間距封裝,未來(lái)一段時(shí)間內(nèi),凸塊封裝技術(shù)仍將持續(xù)發(fā)展。盡管如此,先進(jìn)凸塊和混合鍵合都將為新的先進(jìn)封裝技術(shù)提供窄間距互連。不止一種封裝技術(shù)選擇對(duì)企業(yè)來(lái)說(shuō)非常利好。