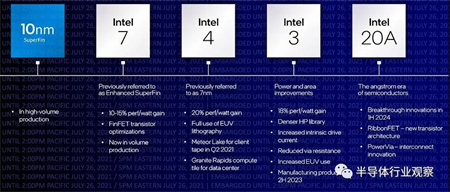

英特爾在 7 月下旬的英特爾加速活動期間宣布其面向未來的半導(dǎo)體工藝節(jié)點(diǎn)的新名稱時(shí)受到了很多抨擊,。按照英特爾的說法,,他們的新節(jié)點(diǎn)稱為 Intel 7、4,、3 和 20A,。但業(yè)內(nèi)權(quán)威人士抨擊該公司將 10 納米增強(qiáng)型 SuperFin 工藝節(jié)點(diǎn)命名為“Intel 7”的做法(英特爾上周在其英特爾創(chuàng)新開發(fā)者大會上宣布并展示了使用Intel 7 工藝節(jié)點(diǎn)構(gòu)建的第 12 代 i5、i7 和 i9 酷睿處理器,,因此該工藝技術(shù)顯然掌握得很好),。該公司現(xiàn)在把“Intel 4” 用于之前稱為 7nm 的節(jié)點(diǎn)。Intel 3 和 Intel 20A 是全新的節(jié)點(diǎn)名稱,。

在筆者看來此次節(jié)點(diǎn)重命名一部分源于營銷,,另一部分只是面對現(xiàn)實(shí)。

英特爾已重新命名其即將推出的工藝節(jié)點(diǎn),,以符合行業(yè)慣例而不是其自身對現(xiàn)實(shí)的看法

過去,,英特爾曾表示其 10nm 增強(qiáng)型 SuperFin 節(jié)點(diǎn)(現(xiàn)更名為Intel 7)在功率和性能上與臺積電的 7nm 節(jié)點(diǎn)大致相當(dāng)。這很令人困惑,,不是嗎,?該公司還表示,行業(yè)分析師已要求英特爾更新其工藝節(jié)點(diǎn)命名法,,以反映該公司在半導(dǎo)體工藝領(lǐng)域的真實(shí)競爭地位,。所有這些都是重命名節(jié)點(diǎn)的營銷部分。

而現(xiàn)實(shí)是這樣的:納米命名法在很長很長一段時(shí)間內(nèi)都不準(zhǔn)確,。不適用于英特爾,,當(dāng)然也不適用于任何其他硅代工廠。這種情況就像熱門喜劇電視節(jié)目“這到底是誰的臺詞,?”中的評分系統(tǒng),,分?jǐn)?shù)不重要。

多年前,,工藝節(jié)點(diǎn)命名是基于晶體管的最小特征尺寸,。該命名約定是專門為平面 MOS 晶體管開發(fā)的,最小晶體管特征總是晶體管的柵極長度,。當(dāng) FinFET 取代平面 MOS 晶體管時(shí),,這種命名約定就消失了,所有供應(yīng)商的工藝節(jié)點(diǎn)名稱都變成了您從等效平面 MOS 晶體管獲得的功率和速度的估計(jì)等效值,。除了他們實(shí)際上無法再制造那些平面 MOS 晶體管。平面晶體管技術(shù)放棄了。MOS 晶體管在目前的光刻水平上不能很好地工作,。這就是我們轉(zhuǎn)向 FinFET 的原因,。早在 2011 年,英特爾就在 22 納米節(jié)點(diǎn)上推出了其首個 FinFET 工藝,。

RibbonFET 和埃

十年后,,晶體管的基本結(jié)構(gòu)即將再次發(fā)生變化。

FinFET 柵極從三個側(cè)面驅(qū)動,。這比平面 MOS 晶體管中驅(qū)動的多了兩個側(cè)面,,它以更復(fù)雜的制造技術(shù)為代價(jià)帶來更好的晶體管性能。然而,,驅(qū)動 FinFET 晶體管柵極的三個側(cè)面不再達(dá)到所需的速度和漏電流,。我們現(xiàn)在必須驅(qū)動?xùn)艠O的所有四個側(cè)面。這些 4 邊柵極驅(qū)動結(jié)構(gòu)通常稱為“Gate all around”或 GAA,。

英特爾稱其 GAA 晶體管為“RibbonFET”,,目前他們計(jì)劃在Intel 20A 工藝中推出改技術(shù),該工藝將于 2024 年上半年出現(xiàn)(除非出現(xiàn)延遲),。注意進(jìn)程名稱中的“A”,。“A”代表“?!?。英特爾沒有像以前的工藝節(jié)點(diǎn)那樣稱這個工藝節(jié)點(diǎn)為“intel 2”,而是將單位從納米切換到埃,。一埃是 10 -10 m,,或十分之一納米。我認(rèn)為我們應(yīng)該簡單地忽略英特爾從更大的工藝節(jié)點(diǎn)中刪除了“nm”這一事實(shí),。

據(jù)推測,,這種對埃的命名更改允許分?jǐn)?shù)納米節(jié)點(diǎn)命名。這與我們之前使用的單位微米的情況類似,?;氐胶诎禃r(shí)代,我們有 3,、2.5,、2、1.5,、1.3,、1.2 和 1 微米的工藝步驟,然后是 0.8,、0.75,、0.7,、0.5,一直到 0.25 微米左右,。在那個點(diǎn)附近的某個地方,,我們從微米跳到了納米。根據(jù)我的記憶,,命名法的變化發(fā)生在 0.18 微米處,,通常稱為 180 納米。那是什么時(shí)候,?大約 1998 年,,這發(fā)生在二十多年前。

這意味著在納米工藝節(jié)點(diǎn)尺將被使用近四分之一個世紀(jì)以后,,埃時(shí)代正式到來,。Intel Angstrom 命名法允許公司擁有名為 Intel 18A、Intel 17A,、Intel 16A 等的工藝節(jié)點(diǎn),。這聽起來比 Intel 1.8、Intel 1.7,、Intel 1.6 等等好多了,,不是嗎?看起來他們也能通過這種方式取得了更大的進(jìn)步,,對嗎,?

然而,我們必須承認(rèn),,從一個節(jié)點(diǎn)到下一個節(jié)點(diǎn)的進(jìn)度不像以前那么大了,。從上圖中,您可以看到從一個英特爾工藝節(jié)點(diǎn)到下一個節(jié)點(diǎn)的性能/瓦特提高了 10% 到 20%,,并且該圖像甚至沒有討論密度改進(jìn),。

摩爾定律在墳?zāi)怪懈癄€了

基于以上所有內(nèi)容,我有一個非常悲傷的消息要告訴你,,摩爾定律已經(jīng)死了,。即使英特爾首席執(zhí)行官帕特·蓋辛格 (Pat Gelsinger) 上周在英特爾創(chuàng)新活動期間做出了在未來 10 年內(nèi)每年都滿足或擊敗摩爾定律的大膽而熱情的承諾。然而通過從一代到下一代削減幾埃來擴(kuò)展工藝節(jié)點(diǎn)并不能實(shí)現(xiàn)晶體管密度的兩倍,,而這正是摩爾定律的真正本質(zhì),。

從我的角度來看,圍繞摩爾定律存在很多困惑,。

首先,,摩爾定律長期以來一直與 Dennard Scaling 緊密交織和混淆,Dennard Scaling 表示平面 MOSFET 的速度和功率隨著晶體管密度的增加而按比例降低,。在半導(dǎo)體的早期,,當(dāng)一種新的工藝技術(shù)將晶體管面積縮小 50% 時(shí),,晶體管的速度會增加一倍,而功率則會減半,。每隔幾年,,我們就獲得了一半大小的晶體管,,其速度是每個新工藝節(jié)點(diǎn)的一半,,而運(yùn)行速度則是一半。那時(shí)確實(shí)是非常好的時(shí)代,,摩爾定律正在全面發(fā)揮作用,。然而,Dennard Scaling 是一個專門針對平面 MOS 晶體管的觀察結(jié)果,,我們已經(jīng)有十年沒有使用最先進(jìn)的新工藝節(jié)點(diǎn)制造這種晶體管了,。

摩爾定律不涉及晶體管功率或速度。摩爾定律說,,芯片上的晶體管數(shù)量大約每兩年翻一番,。這就是它所說的。喜歡的可以查一下,。Gordon Moore 于 1965 年 4 月 19 日在《電子》雜志上發(fā)表的原始文章,,文章標(biāo)題是“將更多元件塞進(jìn)集成電路上”。它方便地發(fā)布在英特爾的網(wǎng)站上供您閱讀,。這篇文章發(fā)表于摩爾和鮑勃諾伊斯創(chuàng)立英特爾的三年前,,當(dāng)時(shí)摩爾和諾伊斯都還在飛兆半導(dǎo)體工作。

摩爾在他開創(chuàng)性的文章中進(jìn)行了令人難以置信的預(yù)測壯舉,。半導(dǎo)體行業(yè)最終接受了他的預(yù)測并將其轉(zhuǎn)化為基于極少數(shù)數(shù)據(jù)點(diǎn)的自我實(shí)現(xiàn)預(yù)言,。第一個數(shù)據(jù)點(diǎn)是單個晶體管。第二個數(shù)據(jù)點(diǎn)是最早的商用集成電路之一,,稱為 Fairchild μLogic Type G RTL 芯片的 3 輸入 NOR 門,。

根據(jù)大衛(wèi)帕特森博士的說法,摩爾定律一直持續(xù)到 2015 年,,因?yàn)樗谋M了氣力,。帕特森怎么會說摩爾定律在 2015 年消亡,而英特爾的高管們一致讓您相信摩爾定律在今天仍然存在并且很好,?這是因?yàn)槟?1965 年論文第 2 頁上的一句話,。那句話是:“……在單個半導(dǎo)體襯底上生產(chǎn)越來越大的電路功能?!?(重點(diǎn)是我的,。)摩爾定律是關(guān)于單片集成電路的,而這不是半導(dǎo)體行業(yè)現(xiàn)在的發(fā)展方向,。

事實(shí)上,,在2003年舉辦的第50屆國際固態(tài)電路會議上,,在一個題為“No Exponential is Forever”的議題中,戈登·摩爾本人斷然指出:“沒有任何的物理事物可以持續(xù)成倍改變,?!?摩爾定律在將近 20 年前就已經(jīng)消亡,而摩爾親眼目睹了這一點(diǎn),。

目前標(biāo)志著摩爾定律終結(jié)的典型代表是英特爾自己的 Ponte Vecchio GPU,。英特爾正在使用 47 個有源“tiles”(英特爾對多芯片封裝中的小芯片或芯片的名稱)組裝這種集成設(shè)備,由來自五個不同半導(dǎo)體工藝節(jié)點(diǎn)的多家半導(dǎo)體供應(yīng)商制造,,所有這些都使用 2.5D 和 3D 組裝組合在一個封裝中技術(shù)來生產(chǎn)具有超過 1000 億個晶體管的集成產(chǎn)品,。

有人聲稱摩爾在他的文章中預(yù)見到了多芯片封裝。他們引用了這句話:

“事實(shí)證明,,用較小的功能構(gòu)建大型系統(tǒng)可能更經(jīng)濟(jì)……”

但他們似乎省略了這句話的后半部分:

“……它們是分開封裝和互連的,。”

在這里,,摩爾清楚地討論了在一塊板上使用多個單獨(dú)封裝的芯片,,這是自 1960 年代集成電路首次出現(xiàn)以來板級設(shè)計(jì)的主要內(nèi)容。

在我看來,,摩爾顯然不是在用這句話來預(yù)測今天的多芯片封裝,。事實(shí)上,他的文章討論了在 10 年內(nèi)(即 1975 年)出現(xiàn)每個 IC 具有 65,000 個元件的單片 IC 的可能性,,這比 1965 年摩爾的文章出現(xiàn)時(shí)任何單個印刷電路板所能容納的分立元件都要多,。

誰可能需要超過 65,000 個組件?如果摩爾當(dāng)時(shí)考慮過,,而且他可能確實(shí)考慮過,,那么他一定已經(jīng)看到,直到很遠(yuǎn)很遠(yuǎn)的將來才會需要多芯片封裝技術(shù),。嗯,,那個未來已經(jīng)到來。

英特爾的 Ponte Vecchio GPU 整合了來自五個不同工藝節(jié)點(diǎn)的 47 個tiles,,將 1000 億個晶體管塞進(jìn)一個封裝中,。(圖片來源:英特爾)

多芯片封裝之所以有意義,只是因?yàn)椴煌墓に嚬?jié)點(diǎn)提供不同的成本/性能/能力權(quán)衡,,因?yàn)槲覀兲幱诋?dāng)前芯片制造設(shè)備的光罩極限,,并且因?yàn)?2.5D 和 3D 封裝技術(shù)現(xiàn)在足夠?qū)嵱煤徒?jīng)濟(jì)這種方法在商業(yè)上有效。假設(shè)您擁有可靠且經(jīng)濟(jì)地組裝所有這些tile或小芯片所需的制造工藝,,為什么不應(yīng)該使用最高效的半導(dǎo)體工藝節(jié)點(diǎn)制造模塊和子系統(tǒng),?Ponte Vecchio無疑是一個工程奇跡,但它絕對不是單片芯片,,因此它不是原始摩爾定律實(shí)際應(yīng)用的例子,。

除了摩爾定律的大量神話基礎(chǔ)之外,,對于我們大多數(shù)人來說,英特爾如何將 1000 億個晶體管塞進(jìn) Ponte Vecchio 封裝實(shí)際上并不重要,。對于在設(shè)計(jì)中使用 Ponte Vecchio GPU 的系統(tǒng)工程師來說,,這并不重要。對于使用在 Ponte Vecchio GPU 上運(yùn)行的圖形軟件或計(jì)算機(jī)游戲的人來說,,這并不重要,。設(shè)備的性能、功率和價(jià)格(所有工程設(shè)計(jì)的三個基本“P”)對于我們這些不熟悉封裝的人來說非常重要,。

英特爾計(jì)劃以類似的方式構(gòu)建公司下一代至強(qiáng)處理器的代號 Sapphire Rapids,。英特爾將使用基于公司 EMIB(嵌入式多芯片互連橋接)技術(shù)的 4 個 CPU 塊和 2.5D 組件制造 Sapphire Rapids。Sapphire Rapids 處理器的多個版本還將在同一封裝中集成多個 HBM2(高帶寬內(nèi)存 2)DRAM 堆棧,。

英特爾的 Sapphire Rapids 是下一代至強(qiáng) CPU,將包含由四個 EMIB 橋連接的四個 CPU 塊,。(圖片來源:英特爾)

多芯片封裝并非英特爾獨(dú)有,。AMD、Nvidia 和 Xilinx 都生產(chǎn)集成芯片,,這些芯片在外部看起來像單片集成電路,,但在內(nèi)部是多芯片設(shè)備——相互連接的tile或小芯片的集合。

例如,,賽靈思在 2011 年推出了 Virtex-7 2000T FPGA,。它基于多芯片封裝,將四個 FPGA 管芯放在一個硅中介層之上,。臺積電為賽靈思制造該器件,。大約在同一時(shí)間,多芯片封裝使賽靈思能夠在其 Virtex-7 580T FPGA 中集成 28 Gbps 收發(fā)器,,然后才能將這些收發(fā)器直接構(gòu)建到 CMOS FPGA 芯片中,。賽靈思在每一代新 FPGA 中都擴(kuò)大了多芯片封裝的使用范圍。這很好地表明多芯片封裝運(yùn)作良好,,至少對于 IC 市場的高端而言是這樣,。

總而言之,歡迎來到埃時(shí)代,。這是一個“超越摩爾”的時(shí)代?,F(xiàn)在擺脫了將所有東西都放在一個芯片上的情感和經(jīng)濟(jì)需求,這個半導(dǎo)體制造的新時(shí)代已經(jīng)生產(chǎn)出比以往任何時(shí)候都更大,、更好的集成設(shè)備,。僅僅依靠單片 IC 和摩爾定律是無法提供這些好處的。

摩爾定律可能已死,,但摩爾定律的精神永存,。