近日,在2021 IEEE國際電子器件會(huì)議(IEDM)上,英特爾公布了在封裝、晶體管微縮、量子物理學(xué)方面的多項(xiàng)關(guān)鍵技術(shù)新突破,積極并布局非硅基半導(dǎo)體,可推動(dòng)摩爾定律繼續(xù)發(fā)展,超越未來十年。

業(yè)內(nèi)人士分析,從此次英特爾憑借高調(diào)宣布的多項(xiàng)新技術(shù)突破,有望在未來幾年在先進(jìn)工藝上領(lǐng)先于臺積電和三星。

日前,英特爾制造、供應(yīng)鏈和營運(yùn)集團(tuán)副總裁、戰(zhàn)略規(guī)劃部聯(lián)席總經(jīng)理盧東暉對媒體詳細(xì)解讀了此次的多項(xiàng)技術(shù)突破。他在會(huì)上感言,研究中最難的就是探路,就好比爬山的人一眼能夠看到山頂在哪里,但是不清楚路該怎么走,要帶多少補(bǔ)給。

盧東暉表示這些全新技術(shù)是有英特爾的組件研究團(tuán)隊(duì)所研制,眾多突破摩爾定律昔日壁壘并出現(xiàn)在當(dāng)前產(chǎn)品中的創(chuàng)新技術(shù),都源自于該組件研究團(tuán)隊(duì)的研究工作,比如:應(yīng)變硅、高K-金屬柵極技術(shù)、FinFET晶體管、RibbonFET,以及包括EMIB和FoverosDirect在內(nèi)的封裝技術(shù)創(chuàng)新。

盧東暉強(qiáng)調(diào),這次英特爾在IEDM上發(fā)的文章都有一個(gè)主要的基體,就是大部分的技術(shù)都是基于300毫米硅晶圓的傳統(tǒng)CMOS技術(shù),這是非常關(guān)鍵的。因?yàn)楫a(chǎn)生一個(gè)新的想法很簡單,很多大學(xué)都在做,而工業(yè)界最大的問題就是能不能大批量生產(chǎn),不能說重新起爐灶弄一個(gè)第四代半導(dǎo)體,最好的辦法就是用現(xiàn)有已經(jīng)投入的固定資產(chǎn),能夠盡快地把這些資產(chǎn)優(yōu)化,不然成本太高,成本太高還是沒人買。摩爾定律是一個(gè)經(jīng)濟(jì)定律,任何一個(gè)新技術(shù)如果不能達(dá)到讓你的用戶能夠負(fù)擔(dān)得起,那最后的應(yīng)用只能是一些非常有限的應(yīng)用。全世界現(xiàn)在大概有上萬億美元的投資都是在12寸晶圓設(shè)備、生態(tài)系統(tǒng),需要把這些利用起來,這樣制造成本才能下降。

在本次的IEDM 2021上英特爾重點(diǎn)介紹了這三個(gè)關(guān)鍵研究領(lǐng)域的最新突破及探索,披露的突破性進(jìn)展表明,英特爾正通過對這三個(gè)領(lǐng)域的探索,持續(xù)推進(jìn)摩爾定律,并將其延續(xù)至2025年及更遠(yuǎn)的未來。

領(lǐng)域一:微縮技術(shù)新突破

據(jù)盧東暉介紹,微縮技術(shù),傳統(tǒng)叫transistor scaling,就是把晶體管面積變小。微縮技術(shù)是很簡單的,有很多辦法可以采用,比如全新的晶體管設(shè)計(jì),或者是光刻技術(shù)的突破,或者用先進(jìn)封裝。以前二維的平面微縮,現(xiàn)在二維不能再縮,再縮就會(huì)有很多量子效應(yīng)出現(xiàn),所以現(xiàn)在就往上堆,早年3D NAND就是一直往上堆,這也是比較直觀的理解。此次IEDM 2021,英特爾介紹了微縮技術(shù)的三個(gè)主要突破:

突破一:互連密度提升10倍以上混合鍵合互連設(shè)計(jì)

英特爾的研究人員提出了混合鍵合互連中的設(shè)計(jì)、制程工藝和組裝難題的解決方案,期望能在封裝中將互連密度提升10倍以上。在今年7月的英特爾加速創(chuàng)新:制程工藝和封裝技術(shù)線上發(fā)布會(huì)中,英特爾宣布計(jì)劃推出Foveros Direct,以實(shí)現(xiàn)10微米以下的凸點(diǎn)間距,使3D堆疊的互連密度提高一個(gè)數(shù)量級。為了使生態(tài)系統(tǒng)能從先進(jìn)封裝中獲益,英特爾還呼吁建立新的行業(yè)標(biāo)準(zhǔn)和測試程序,讓混合鍵合芯粒(hybrid bonding chiplet)生態(tài)系統(tǒng)成為可能。

盧東暉解釋說,傳統(tǒng)技術(shù)(SolderAttach)是通過焊錫將兩個(gè)芯片進(jìn)行連接,英特爾在研究的混合鍵成技術(shù)是讓金屬墊直接接觸,這樣會(huì)產(chǎn)生分子鍵合。“它最大的好處是連接的密度會(huì)急劇提升,至少是10倍的。這會(huì)讓每平方毫米達(dá)到有10000個(gè)連接,這是非常緊密的。以后的芯片上會(huì)有幾十億的晶體管,或者幾百億的晶體管,最后都要連起來,所以這是非常關(guān)鍵的突破。”盧東暉說道。

盧東暉指出,這項(xiàng)技術(shù)的制程非常敏感,需要用機(jī)械拋光磨平表面,因此化學(xué)機(jī)械拋光(SNP)和沉積的優(yōu)化是非常關(guān)鍵的。此外,也需要行業(yè)統(tǒng)一的標(biāo)準(zhǔn)和測試程序。

突破二:GAA進(jìn)一步縮小3倍

晶體管剛開始是二維的形式,后來變成FinFET,就是變成三維封裝,再后來變成GAA,就是把NMOS疊在左邊,PMOS疊在右邊,往上疊了幾層,而3D就是直接把NMOS和PMOS直接疊在一起,這樣相當(dāng)于面積減少了一半,面積利用率提高,微縮技術(shù)達(dá)到了面積減少一半的要求。

展望其GAA RibbonFET(Gate-All-Around RibbonFET)技術(shù),英特爾正引領(lǐng)著即將到來的后FinFET時(shí)代,通過堆疊多個(gè)(CMOS)晶體管,實(shí)現(xiàn)高達(dá)30%至50%的邏輯微縮提升,通過在每平方毫米上容納更多晶體管,以繼續(xù)推進(jìn)摩爾定律的發(fā)展。

英特爾在論文中宣布了這項(xiàng)技術(shù)在3D CMOS堆疊上的新突破,共有兩種方法。方法一是依序,具體的工藝流程是將下面一層晶圓先做好,再將上面一層翻過來再做另外一層晶圓,這樣能夠有效提高性能;方法二是自對準(zhǔn),一種是通過光刻機(jī)對準(zhǔn),另一種叫做自我對準(zhǔn),要通過干蝕或者是沉積手段讓晶圓自動(dòng)對準(zhǔn)。英特爾的自對準(zhǔn)實(shí)現(xiàn)了55納米的柵極間距,盧東暉稱“這是非常了不起的突破”。

英特爾引入了金屬銻和釕來突破硅的限制。因?yàn)楝F(xiàn)在電流的通道是用硅的基礎(chǔ),而這個(gè)是用二維材料TMD(過渡金屬硫化物),它有一個(gè)非常好的特點(diǎn)是在Gate下面有一層非常薄的,單層的二硫化物原子層,可以作為更短的通道。因?yàn)楣璧膯栴}是無法繼續(xù)往下縮,因?yàn)樵偻驴s很多量子效應(yīng)出現(xiàn),但二維材料有自己本身的特質(zhì),所以可以做得非常小。最大的突破不光是這個(gè)做出來了,而是用兩種不同的金屬去做金屬接觸,在源極和漏極,NMOS用的是銻,PMOS用的是釕,這樣能讓電容比較小一點(diǎn)。

這些背后都是大量的研究,過渡金屬有幾十種,如何知道這兩種是比較好的,這是需要花很多時(shí)間、材料、精力去做,而把GAA一下子縮小3倍,從15納米變成5納米,這是非常了不起的。

突破三:進(jìn)入埃米時(shí)代

英特爾同時(shí)也在為摩爾定律進(jìn)入埃米時(shí)代鋪平道路,其前瞻性的研究展示了英特爾是如何克服傳統(tǒng)硅通道限制,用僅有數(shù)個(gè)原子厚度的新型材料制造晶體管,從而實(shí)現(xiàn)在每個(gè)芯片上增加數(shù)百萬晶體管數(shù)量。在接下來的十年,實(shí)現(xiàn)更強(qiáng)大的計(jì)算。

領(lǐng)域二:為傳統(tǒng)硅注入新功能

盧東暉告訴媒體,因?yàn)楣枳龉β势骷遣惶线m的,尤其是要硅基CMOS要應(yīng)用到汽車或者需要的高壓器件電子設(shè)備,這就得想辦法為硅注入一些新的功能。另外就是更最大的內(nèi)存資源,因?yàn)楫?dāng)下需要的數(shù)據(jù)量、產(chǎn)生的數(shù)據(jù)量越來越大,比如手機(jī)上拍個(gè)照片,現(xiàn)在文件的大小與十年前相比超過很多倍了,所以結(jié)果需要的存儲量越來越大,存儲量越來越大需要的處理能力越來越高,而新材料的突破是迫在眉睫的。

在該領(lǐng)域,英特爾本次披露了兩大技術(shù)突破

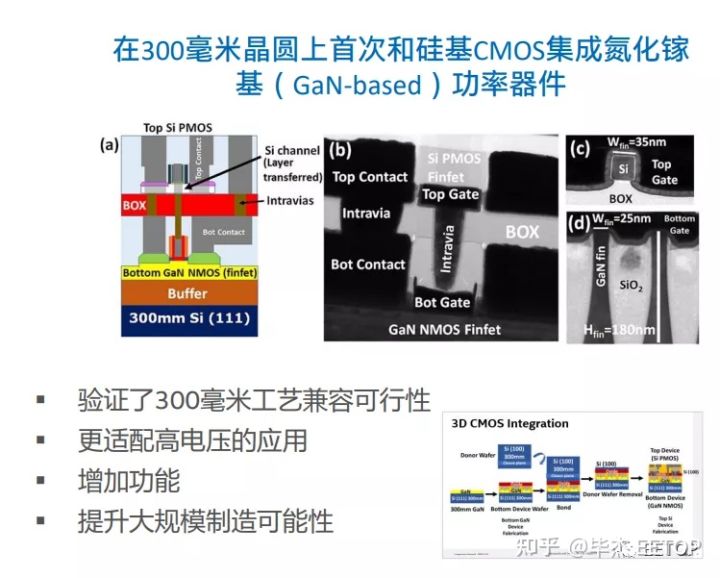

1. 首次將氮化鎵與硅集成在一起

通過在300毫米的晶圓上首次集成氮化鎵基(GaN-based)功率器件與硅基CMOS,實(shí)現(xiàn)了更高效的電源技術(shù)。這為CPU提供低損耗、高速電能傳輸創(chuàng)造了條件,同時(shí)也減少了主板組件和空間。

現(xiàn)在的功率器件GaN在國內(nèi)也比較熱,它可以直接做出70伏的晶體管,這是硅做不到的。英特爾這次也是首次集成,因?yàn)橐郧皼]有人在硅晶圓做過,很多人可能直接用GaN wafer,但這個(gè)成本很高。英特爾這次的GaN直接跟傳統(tǒng)的硅晶圓集成在一起,這在以前是沒有出現(xiàn)過的。

硅基CMOS集成有兩個(gè)突破:一個(gè)是用硅晶圓上面放一個(gè)buffer,buffer更外面就是用的氧化硅的。在這樣的情況下,它其實(shí)不需要硅晶圓,只要有載體就行。在硅片上,所有的基材不需要特制的基材。另外一個(gè)是驗(yàn)證了300毫米工藝兼容可行性。盧東暉特別強(qiáng)調(diào)半導(dǎo)體一定要從這個(gè)方面著手,因?yàn)楣I(yè)界在300毫米投入資金和生態(tài)鏈已經(jīng)太強(qiáng)大了,最好不要突破它,突破它成本會(huì)很高。

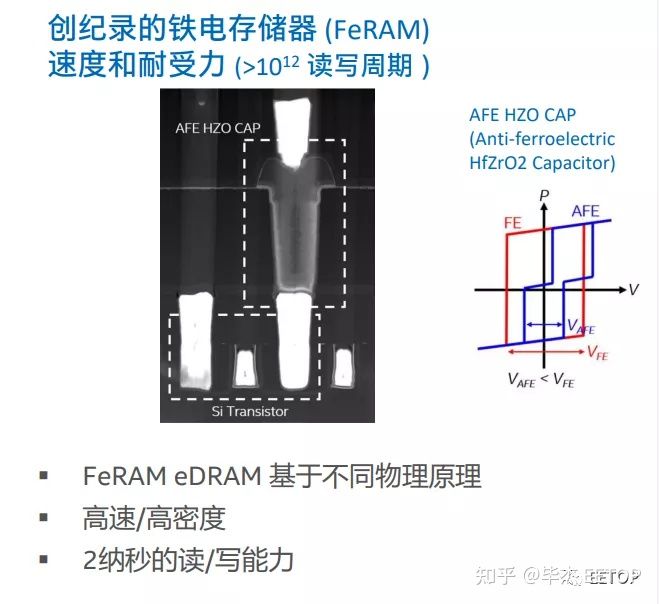

2. 新型鐵電體材料

另一項(xiàng)進(jìn)展是利用新型鐵電體材料作為下一代嵌入式DRAM技術(shù)的可行方案。該項(xiàng)業(yè)界領(lǐng)先技術(shù)可提供更大內(nèi)存資源和低時(shí)延讀寫能力,用于解決從游戲到人工智能等計(jì)算應(yīng)用所面臨的日益復(fù)雜的問題。

鐵電存儲它是用了一個(gè)新的存儲器,用了一個(gè)新的技術(shù)實(shí)現(xiàn)了2納秒的讀寫速度和超過1012次方的讀寫周期,這個(gè)是非常了不起的技術(shù)成就。

鐵電存儲器國內(nèi)也有很多公司在關(guān)注,這完全是跟傳統(tǒng)的CMOS工藝結(jié)合的。英特爾做這個(gè)東西有非常大的優(yōu)勢,因?yàn)橛⑻貭栍凶约旱腦86架構(gòu),由于具有2納秒的高速讀/寫能力,鐵電存儲器可以用來作為從L1 Cache到DRMA之間的中間層。

領(lǐng)域三:量子芯片走向室溫

英特爾正致力于大幅提升硅基半導(dǎo)體的量子計(jì)算性能,同時(shí)也在開發(fā)能在室溫下進(jìn)行高效、低功耗計(jì)算的新型器件。未來,基于全新物理學(xué)概念衍生出的技術(shù)將逐步取代傳統(tǒng)的MOSFET晶體管:

在IEDM 2021上,英特爾展示了全球首例常溫磁電自旋軌道(MESO)邏輯器件,這表明未來有可能基于納米尺度的磁體器件制造出新型晶體管。英特爾和比利時(shí)微電子研究中心(IMEC)在自旋電子材料研究方面取得進(jìn)展,使器件集成研究接近實(shí)現(xiàn)自旋電子器件的全面實(shí)用化。英特爾還展示了完整的300毫米量子比特制程工藝流程。該量子計(jì)算工藝不僅可持續(xù)微縮,且與CMOS制造兼容,這確定了未來研究的方向。