IBIS建模——第1部分:為何IBIS建模對(duì)設(shè)計(jì)成功至關(guān)重要

2022-04-19

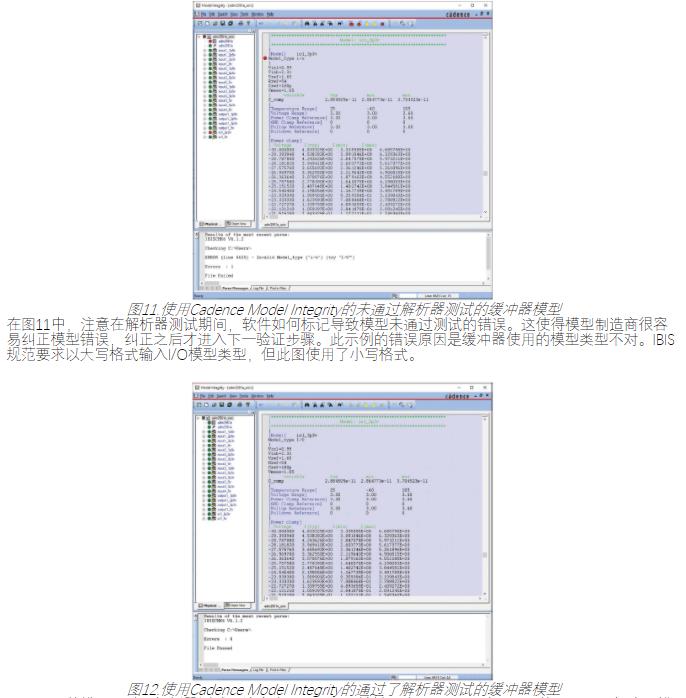

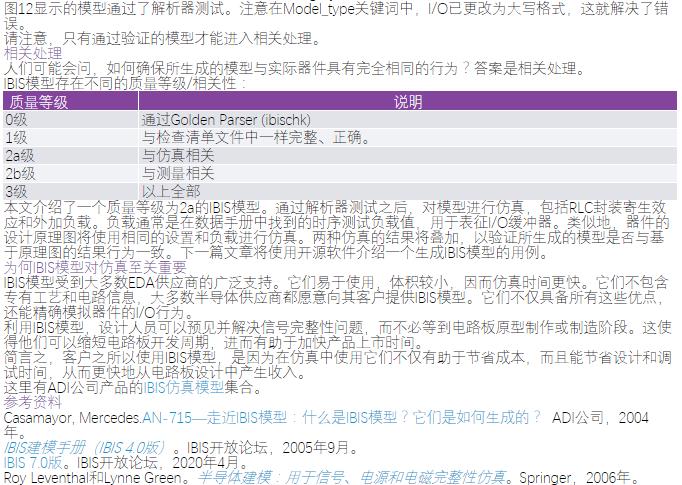

作者:ADI產(chǎn)品應(yīng)用工程師 Jermaine Lim,ADI設(shè)計(jì)驗(yàn)證工程師 Keith Francisco-Tapan

來(lái)源:ADI公司

什么是IBIS模型?

IBIS表示輸入/輸出緩沖器信息規(guī)格,它代表了IC供應(yīng)商提供給客戶進(jìn)行高速設(shè)計(jì)仿真的器件的數(shù)字引腳的特性或行為。這些模型使用IBIS開(kāi)放論壇——負(fù)責(zé)管理和更新IBIS模型規(guī)范與標(biāo)準(zhǔn)的行業(yè)組織——所規(guī)定的參數(shù)模仿器件的I/O行為。IBIS模型使用ASCII文本文件格式,提供表格化的電壓-電流和電壓-時(shí)間信息。它們不包含專(zhuān)有數(shù)據(jù),因?yàn)槟P椭袥](méi)有披露IC原理圖設(shè)計(jì)信息,如晶體管尺寸、緩沖器原理圖設(shè)計(jì)中使用的器件模型參數(shù)和電路等。此外,IBIS模型獲得了大部分EDA供應(yīng)商的支持,可以在大多數(shù)行業(yè)級(jí)平臺(tái)中運(yùn)行。

為何使用IBIS模型?

想象一款I(lǐng)C通過(guò)了測(cè)試。然后,使用該IC設(shè)計(jì)電路板,并且立即獲批進(jìn)行制造。電路板制造出來(lái)后,發(fā)現(xiàn)其性能不達(dá)標(biāo),原因是一些信號(hào)完整性問(wèn)題,其導(dǎo)致了串?dāng)_、信號(hào)過(guò)沖/欠沖或不匹配阻抗引起的反射。您認(rèn)為接下來(lái)會(huì)發(fā)生什么?當(dāng)然,電路板必須重新設(shè)計(jì)和制造。此時(shí),增加了時(shí)間和成本。所有這一切都是因?yàn)橛幸粋€(gè)重要階段沒(méi)有進(jìn)行:預(yù)仿真。在此階段中,系統(tǒng)設(shè)計(jì)人員使用仿真模型驗(yàn)證設(shè)計(jì)的信號(hào)完整性,然后才會(huì)設(shè)計(jì)電路板。SPICE和IBIS等仿真模型現(xiàn)已廣泛開(kāi)發(fā)用于仿真當(dāng)中,幫助系統(tǒng)設(shè)計(jì)人員在預(yù)仿真階段預(yù)見(jiàn)到信號(hào)完整性問(wèn)題,從而在制造之前予以解決。此階段有助于減少測(cè)試期間電路板失敗的可能。

歷史

20世紀(jì)90年代,隨著個(gè)人計(jì)算機(jī)日漸流行,Intel?開(kāi)始為其工作頻率約為33 MHz的低功耗ASIC開(kāi)發(fā)一種新的I/O總線。為此需要確保信號(hào)完整性沒(méi)有受到損害,IBIS因此而誕生。Donald Telian所領(lǐng)導(dǎo)的團(tuán)隊(duì)提出了一個(gè)想法:為I/O緩沖器創(chuàng)建一個(gè)信息表,并使用此信息測(cè)試Intel的電路板。很快,Intel與其客戶共享這些信息表以幫助后者進(jìn)行電路板設(shè)計(jì),但不提供任何專(zhuān)有信息。為了能夠可靠地將紙張形式的表格中的信息傳送到客戶的仿真器,Intel決定與EDA供應(yīng)商和其他計(jì)算機(jī)制造商合作。他們創(chuàng)建了IBIS開(kāi)放論壇,以幫助標(biāo)準(zhǔn)化計(jì)算機(jī)可讀格式的緩沖器信息。IBIS最初稱為Intel緩沖器信息表,后來(lái)更改為I/O緩沖器信息規(guī)范。IBIS 1.0版于1993年發(fā)布。從那時(shí)起,IBIS開(kāi)放論壇持續(xù)推廣IBIS,提供工具和文檔,并改進(jìn)標(biāo)準(zhǔn)以增加專(zhuān)業(yè)領(lǐng)域的能力。2019年,IBIS 7.0版被批準(zhǔn)。這表明,IBIS在不斷發(fā)展以滿足新技術(shù)要求。

如何生成IBIS模型?

IBIS模型一般模擬器件的接收器和驅(qū)動(dòng)緩沖器行為,而不透露專(zhuān)有工藝信息。為此需要提取標(biāo)準(zhǔn)IBIS緩沖器元件的行為,并通過(guò)表格形式的V-I和V-t數(shù)據(jù)來(lái)表示它。

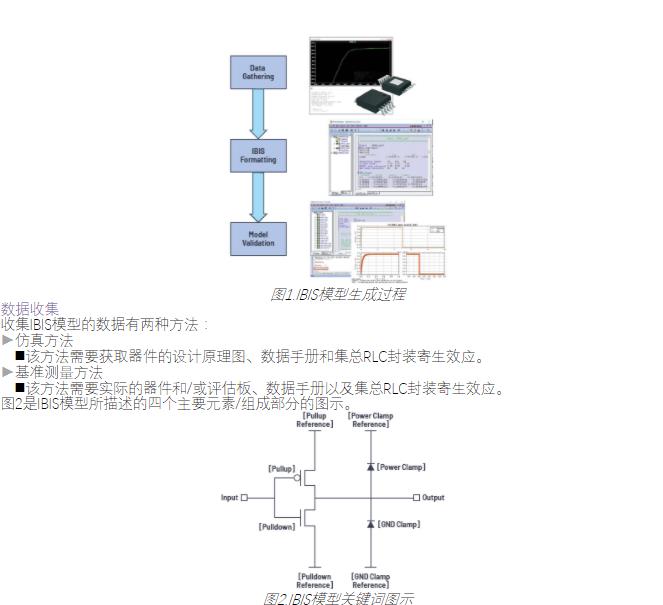

為了生成IBIS模型,數(shù)據(jù)收集通常是開(kāi)發(fā)過(guò)程中的第一步。圖1顯示了生成IBIS模型的三個(gè)主要階段。

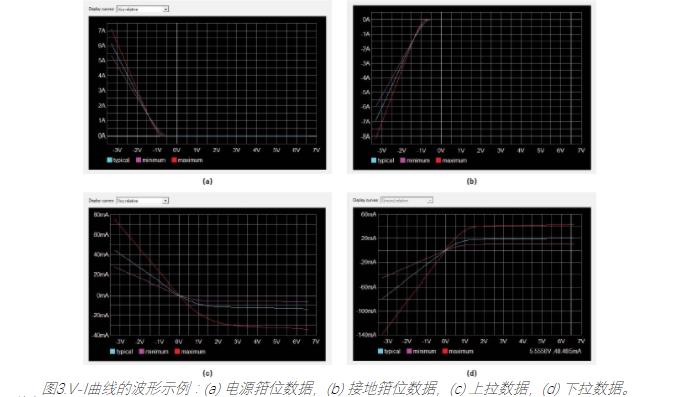

連接到引腳的兩個(gè)二極管負(fù)責(zé)在輸入超過(guò)工作范圍或緩沖器限值時(shí)保護(hù)緩沖器。根據(jù)設(shè)計(jì)工作方式,緩沖器限值可以是功率箝位基準(zhǔn)值,通常為VDD,或是地箝位基準(zhǔn)值,通常為地或-VDD。這些二極管用作ESD箝位保護(hù),在需要時(shí)導(dǎo)通,而上拉和下拉元件負(fù)責(zé)高電平和低電平狀態(tài)期間的緩沖器驅(qū)動(dòng)行為。因此,上拉和下拉數(shù)據(jù)是在緩沖器處于工作模式時(shí)獲得。

在模型中,這四個(gè)主要元素以電壓-電流(V-I)數(shù)據(jù)的形式表示,分別列在關(guān)鍵詞[Power Clamp]、[GND Clamp]、[Pullup]、[Pulldown]之下。I/O緩沖器的切換行為也以電壓-時(shí)間(V-t)的形式在模型中表示。

電壓-電流行為關(guān)鍵詞

?[Power Clamp]表示數(shù)字I/O引腳的功率箝位ESD保護(hù)二極管在高阻抗?fàn)顟B(tài)期間的V-I行為,其相對(duì)于功率箝位基準(zhǔn)電壓。

?[GND Clamp]表示數(shù)字I/O引腳的地箝位ESD保護(hù)二極管在高阻抗?fàn)顟B(tài)期間的V-I行為,其相對(duì)于地箝位基準(zhǔn)電壓。

?[Pullup]表示I/O緩沖器的上拉元件驅(qū)動(dòng)高電平時(shí)的V-I行為,其相對(duì)于上拉基準(zhǔn)電壓。

?[Pulldown]表示I/O緩沖器的下拉元件驅(qū)動(dòng)低電平時(shí)的V-I行為,其相對(duì)于下拉基準(zhǔn)電壓。

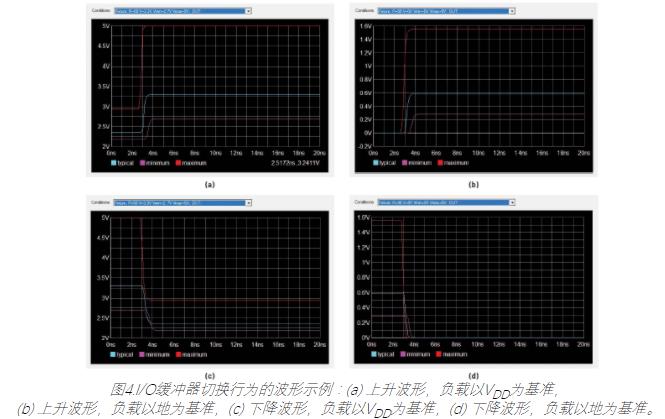

這些關(guān)鍵詞的數(shù)據(jù)是在-VDD至2×VDD的推薦電壓范圍內(nèi)和三個(gè)不同拐角(典型值、最小值和最大值)中獲得。典型值拐角表示緩沖器在標(biāo)稱電壓、標(biāo)稱工藝和標(biāo)稱溫度下工作時(shí)的行為。最小值拐角表示緩沖器在最小電壓、最差工藝和最高工作結(jié)溫(CMOS)/最低工作結(jié)溫(BJT)下工作時(shí)的行為。最大值拐角表示緩沖器在最大電壓、最佳工藝和最低工作結(jié)溫(CMOS)/最高工作結(jié)溫(BJT)下工作時(shí)的行為。

對(duì)于引腳中掃過(guò)的每個(gè)電壓,測(cè)量其相應(yīng)的電流,從而獲得根據(jù)IBIS規(guī)范對(duì)緩沖器進(jìn)行建模所需的電壓-電流行為。圖3顯示了三個(gè)拐角中獲得的這四個(gè)V-I曲線的波形例子。

切換行為

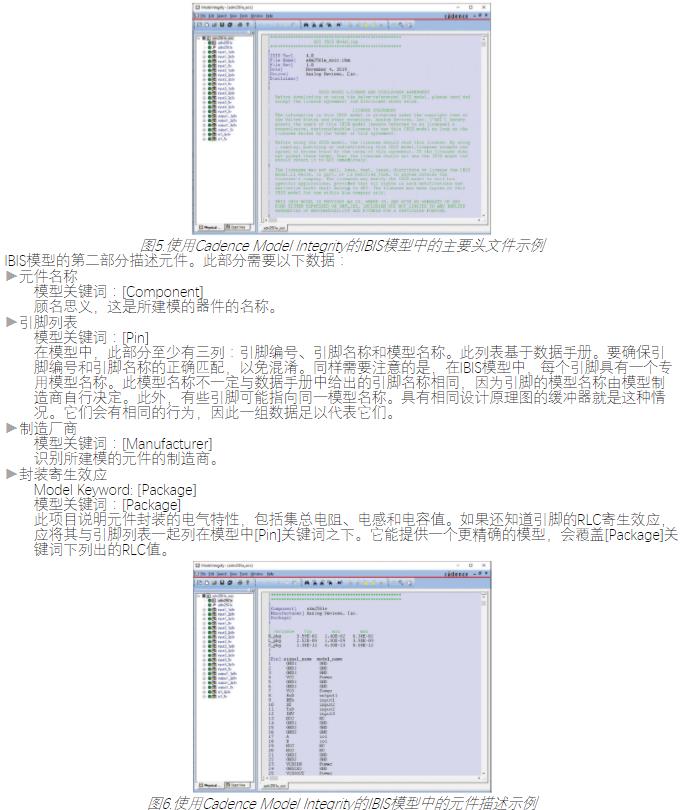

除了V-I數(shù)據(jù)之外,V-t數(shù)據(jù)表中還包括上升(低至高輸出轉(zhuǎn)換)和下降(高至低輸出轉(zhuǎn)換)波形形式的I/O緩沖器切換行為。此數(shù)據(jù)在輸出連接測(cè)得。使用的負(fù)載通常為50Ω,代表典型的傳輸線路特性阻抗。此外,使用輸出緩沖器實(shí)際驅(qū)動(dòng)的負(fù)載仍然是最好的。該負(fù)載與系統(tǒng)中使用的傳輸線路阻抗相關(guān)。例如,如果系統(tǒng)將使用75Ω走線或傳輸線,則獲得V-t數(shù)據(jù)所使用的推薦負(fù)載為75Ω。

對(duì)于標(biāo)準(zhǔn)推挽式CMOS,建議在IBIS模型中包含四類(lèi)V-t數(shù)據(jù):

?上升波形,負(fù)載以VDD為基準(zhǔn)

?上升波形,負(fù)載以地為基準(zhǔn)

?下降波形,負(fù)載以VDD為基準(zhǔn)

?下降波形,負(fù)載以地為基準(zhǔn)

兩個(gè)上升波形包含在模型關(guān)鍵詞[Rising Waveform]之下。它描述當(dāng)負(fù)載分別連接到VDD和地時(shí)I/O緩沖器的低到高輸出轉(zhuǎn)換。另一方面,模型關(guān)鍵詞[Falling Waveform]之下的兩個(gè)下降波形描述當(dāng)負(fù)載同樣分別連接到VDD和地時(shí)I/O緩沖器的高到低轉(zhuǎn)換。應(yīng)當(dāng)注意,由于輸出端連接有負(fù)載,輸出擺幅不會(huì)完全轉(zhuǎn)換。與電壓-電流行為一樣,電壓-時(shí)間數(shù)據(jù)也是在三個(gè)不同的拐角中獲得。這些轉(zhuǎn)換的例子如圖4所示。

在得到V-t表的同時(shí),提取斜坡速率值。斜坡速率是電壓從一個(gè)狀態(tài)切換到另一個(gè)狀態(tài)的速率,取上升或下降轉(zhuǎn)換沿的20%至80%這一段。在IBIS模型中,斜坡速率以dV/dt比率的形式列在[Ramp]關(guān)鍵詞之下,通常顯示在V-t表之后。此值不包括封裝寄生效應(yīng)的影響,因?yàn)樗鼉H代表內(nèi)在輸出緩沖器的上升時(shí)間和下降時(shí)間特性。

IBIS模型還包括一些數(shù)據(jù)手冊(cè)規(guī)格,仿真以此為基礎(chǔ)進(jìn)行,例如工作電壓和溫度范圍、輸入邏輯電壓閾值、時(shí)序測(cè)試負(fù)載值、緩沖器電容和引腳配置。模型中還有集總RLC封裝寄生效應(yīng),這在數(shù)據(jù)手冊(cè)中是找不到的,但對(duì)高速設(shè)計(jì)系統(tǒng)的走線仿真非常重要,因?yàn)檫@些寄生效應(yīng)會(huì)給仿真帶來(lái)負(fù)載效應(yīng),從而影響通過(guò)傳輸線路的信號(hào)的完整性。

IBIS格式化

本節(jié)介紹第二階段,即構(gòu)建模型,也稱為IBIS格式化。收集所有必要的數(shù)據(jù)之后,現(xiàn)在可以創(chuàng)建模型。IBIS模型主要包括三部分:主要頭文件、元件描述和緩沖器模型。

主要頭文件包含有關(guān)該模型的一般信息。它指定以下內(nèi)容:

?IBIS版本

模型關(guān)鍵詞:[IBIS Ver]

這是模型所基于的版本。它告訴仿真器的解析器檢查程序,文件中會(huì)出現(xiàn)什么類(lèi)型的數(shù)據(jù);因此,它對(duì)判斷模型能否通過(guò)解析器檢查發(fā)揮著重要作用。

?文件名

模型關(guān)鍵詞:[File Name]

文件的實(shí)際名稱,應(yīng)為小寫(xiě)形式,并使用正確的文件擴(kuò)展名 .ibs。

?版本號(hào)

模型關(guān)鍵詞:[File Rev]

幫助跟蹤文件的修訂情況。

?日期

模型關(guān)鍵詞:[Date]

顯示模型的創(chuàng)建時(shí)間。

?注釋

模型關(guān)鍵詞:[Notes]

向客戶提供關(guān)于模型的參考信息,即數(shù)據(jù)是從仿真中獲得,還是從基準(zhǔn)測(cè)量中獲得。

?來(lái)源

模型關(guān)鍵詞:[Source]

模型來(lái)自何處,或模型提供商是誰(shuí)。

?免責(zé)聲明

模型關(guān)鍵詞:[Disclaimer]

?版權(quán)

模型關(guān)鍵詞:[Copyright]

請(qǐng)注意,主要頭文件下列出的前三項(xiàng)必須提供。其他項(xiàng)目不是必需的,但最好包括,以便提供有關(guān)該文件的其他細(xì)節(jié)。

作者簡(jiǎn)介

Jermaine Lim于2014年10月加入ADI公司,擔(dān)任產(chǎn)品應(yīng)用工程師。從那時(shí)起,她對(duì)ADI公司的貢獻(xiàn)都集中在為各種ADI產(chǎn)品開(kāi)發(fā)IBIS模型上。Jermaine畢業(yè)于Pamantasan ng Lungsod ng Maynila,獲電子工程學(xué)士學(xué)位。

Keith Francisco-Tapan于2012年3月加入ADI公司,擔(dān)任模擬設(shè)計(jì)工程師。她最初為各種ADI產(chǎn)品開(kāi)發(fā)IBIS模型,并在ADGT掌握了模型開(kāi)發(fā)能力。她現(xiàn)在有一個(gè)新的角色,擔(dān)任AMS設(shè)計(jì)驗(yàn)證工程師。她畢業(yè)于Mindanao State University-Iligan Institute of Technology,獲電子工程學(xué)士學(xué)位。