動態(tài)截取固定長度數(shù)據(jù)語法,即+:和-:的使用,這兩個叫什么符號呢,?運算符嗎,?

Verilog比較方便的一個特點就是數(shù)據(jù)的截取和拼接功能了,截取使用方括號[],拼接使用大括號{},例如

reg [7:0] vect;

wire a;

wire [3:0] b,

wire [5:0] c;

assign a = vect[1]; //取其中1Bit

assign b[3:0] = vect[7:4];//截取4Bit

assing c[5:0] = {a, b[3:0], 1'b1}; //拼接

于是舉一反三(zi zuo cong ming),為了實現(xiàn)動態(tài)截取固定長度數(shù)據(jù)的功能,,使用軟件編程的思維寫了如下語句,功能很好理解,,根據(jù)cnt的值,,每次截取vect的5Bit數(shù)據(jù)。:

reg [7:0] vect;

reg [1:0] cnt;

wire [4:0] out;

assign out = vect[cnt+4:cnt];

一頓操作猛如虎,,編譯一看傻如狗,。使用ModelSim編譯之后,提示有如下語法錯誤:

** Error: test.v(10): Range must be bounded by constant expressions.

提示vect的范圍必須為常量表達式,。也就是必須為,,vect[6:2]或vect[7:4],不能是vect[a:0],,vect[4:b],,或vect[a:b]。額,,這該怎么辦呢,?

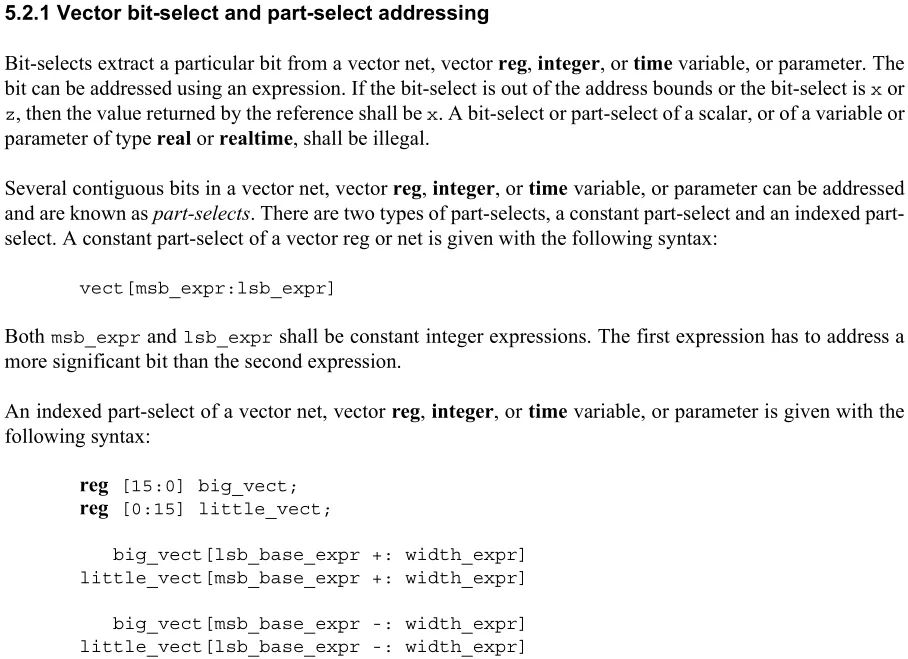

既然有這個使用場景,那Verilog在設(shè)計之初就應(yīng)該會考慮到這個應(yīng)用吧,!于是就去翻IEEE的Verilog標準文檔,,在5.2.1章節(jié)發(fā)現(xiàn)了一個用法可以實現(xiàn)我這個需求,那就是+:和-:符號,,這個用法很少,,在大部分關(guān)于FPGA和Verilog書籍中都沒有提到。

?。ǐ@取IEEE官方Verilog標準文檔IEEE_Verilog_1364_2005.pdf下載,,公眾號(ID:電子電路開發(fā)學(xué)習(xí))后臺回復(fù)【Verilog標準】)

大致意思就是,可以實現(xiàn)動態(tài)截取固定長度的數(shù)據(jù),,基本語法為:

vect[base+:width]或[base-:width]

其中base可以為變量,,width必須為常量。

下面來舉幾個例子來理解這個符號。

有如下定義:

reg [7:0] vect_1;

reg [0:7] vect_2;

wire [2:0] out;

以下寫法分別表示什么呢,?

vect_1[4+:3];

vect_1[4-:3];

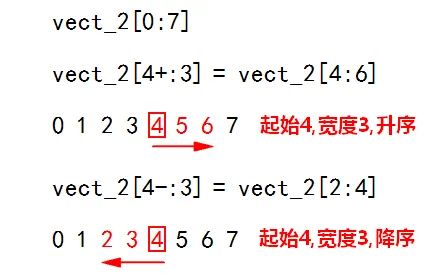

vect_2[4+:3];

vect_2[4-:3];

分為三步:

1.先看定義,。

vect_1[7:0]定義是大端模式,則vect_1[4+:3]和vect_1[4-:3]轉(zhuǎn)換后也一定為大端模式,;vect_2[0:7]定義是小端模式,,則vect_2[4+:3]和vect_2[4-:3]轉(zhuǎn)換后也一定為小端模式。

2.再看升降序,。

其中+:表示升序,-:表示降序

3.看寬度轉(zhuǎn)換,。

vect_1[4+:3]表示,,起始位為4,寬度為3,,**升序**,,則vect_1[4+:3] = vect_1[6:4]

vect_1[4-:3]表示,起始位為4,,寬度為3,,**降序**,則vect_1[4-:3] = vect_1[4:2]

同理,,

vect_2[4+:3]表示,,起始位為4,寬度為3,,升序,,則vect_2[4+:3] = vect_2[4:6]

vect_2[4-:3]表示,起始位為4,,寬度為3,,降序,則vect_2[4-:3] = vect_2[2:4]

ModelSim仿真驗證,,新建test.v文件:

module test;

reg [7:0] vect_1;

reg [0:7] vect_2;

initial

begin

vect_1 = 'b0101_1010;

vect_2 = 'b0101_1010;

$display("vect_1[7:0] = %b, vect_2[0:7] = %b", vect_1, vect_2);

$display("vect_1[4+:3] = %b, vect_1[4-:3] = %b", vect_1[4+:3], vect_1[4-:3]);

$display("vect_2[4+:3] = %b, vect_2[4-:3] = %b", vect_2[4+:3], vect_2[4-:3]);

$stop;

end

endmodule

在ModelSim命令窗口輸入:

//進入到源文件所在文件夾

cd c:/users/whik/desktop/verilog

//編譯

vlog test.v

//仿真

vsim work.test

//運行

run -all

//運行結(jié)果

# vect_1[7:0] = 01011010, vect_2[0:7] = 01011010

# vect_1[4+:3] = 101, vect_1[4-:3] = 110

# vect_2[4+:3] = 101, vect_2[4-:3] = 011

# ** Note: $stop : test.v(15)

# Time: 0 ps Iteration: 0 Instance: /test

# Break in Module test at test.v line 15

這種語法表示需要注意,,前者起始位可以是變量,后者的寬度必須是常量,,即vect[idx+:cnt]不符合語法標準,,vect[idx+:4]或vect[idx-:4]才符合。

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<