版圖驗證工具的作用是檢查版圖是否滿足設(shè)計規(guī)則、電氣規(guī)則、版圖與電路圖是否一致等,對于降低設(shè)計失敗的風(fēng)險具有重要作用。

版圖驗證工具不僅要支持扁平化驗證,而且要支持層次化驗證。扁平化驗證是版圖驗證工具的基礎(chǔ);層次化驗證充分利用版圖層次,可以有效避免重復(fù)報錯和提高處理版圖的速度。對于大規(guī)模版圖,通常還采用并行技術(shù)以加速版圖驗證效率。

版圖驗證工具主要包括設(shè)計規(guī)則檢查(Design Rule Check,DRC)、版圖電路圖一致性檢查(Layout Versus SchemaTIc,LVS)、電氣規(guī)則檢查(Electronic Rule Check,ERC)、版圖比對檢查(Layout Versus Layout,LVL)等。

1.設(shè)計規(guī)則檢查(DRC)

版圖設(shè)計必須遵循制造工藝的設(shè)計規(guī)則要求,因此設(shè)計檢查主要包括連線寬度、連線間距、圖形包含關(guān)系、金屬密度、天線效應(yīng)檢查等。如果版圖設(shè)計中違反了這些規(guī)則將導(dǎo)致制造失敗,例如線條寬度過小可能導(dǎo)致斷路。

DRC涉及的關(guān)鍵技術(shù)有層次處理和掃描線算法等。

層次處理技術(shù)是對版圖原始層次進(jìn)行調(diào)整,根據(jù)需要對版圖圖形進(jìn)行投影或提升以提高DRC工具的性能。

掃描線算法包括基于梯形的掃描線算法和基于邊的掃描線算法。DRC技術(shù)通常采用基于邊的掃描線算法。

邊,即一條線段,用它的兩個端點(diǎn)的坐標(biāo)表示。基于邊的掃描線算法的本質(zhì)是將平面的二維幾何問題轉(zhuǎn)化成兩個一維問題,包含以下幾個步驟:

(1)確定當(dāng)前掃描線的位置;

(2)加入當(dāng)前掃描線上的新進(jìn)邊,與原有的邊構(gòu)成當(dāng)前掃描線邊集合;

(3)對當(dāng)前掃描線邊集合進(jìn)行排序;

(4)遍歷當(dāng)前掃描線邊集合,根據(jù)不同的命令進(jìn)行相應(yīng)的邏輯處理;

(5)刪除當(dāng)前掃描線上的離開邊,并重新回到步驟(1)。

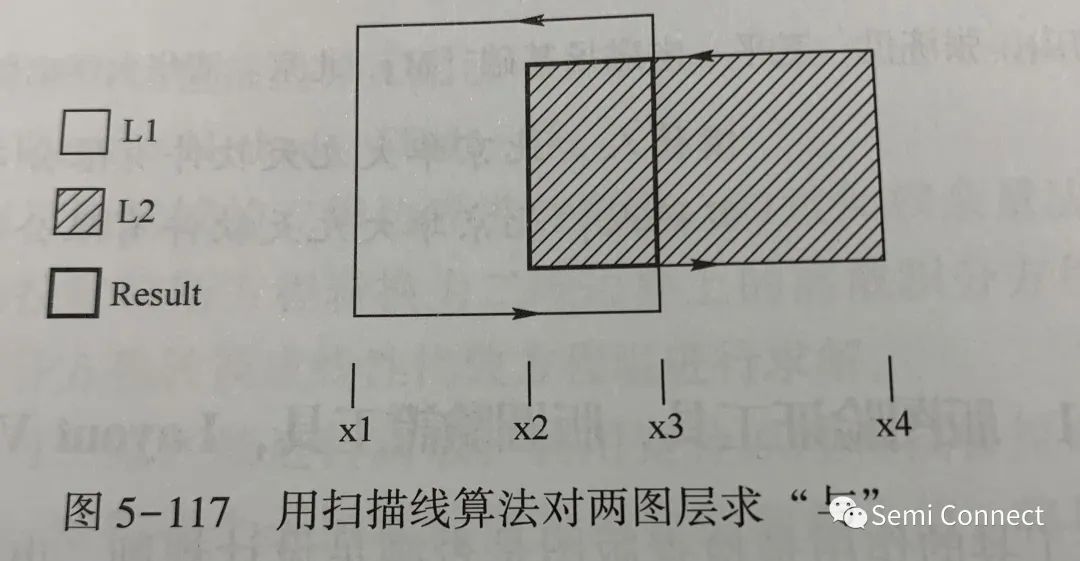

在圖5-117中,L1和L2圖層為輸入圖層,x1、x2、x3、x4為掃描線需要計算的位置,Result圖層為結(jié)果圖層。

2.版圖電路圖一致性檢查(LVS)

LVS工具的主要功能是檢查從版圖中提取的網(wǎng)表和從電路圖中導(dǎo)出的網(wǎng)表的一致性,涉及的主要技術(shù)有網(wǎng)表提取(Netlist ExtracTIon)技術(shù)和網(wǎng)表比較(Netlist Comparison)技術(shù)。網(wǎng)表提取的主要工作是提取電路的線網(wǎng)(Net)、器件(Device)和器件屬性。網(wǎng)表比較本質(zhì)上是圖論中的圖同構(gòu)問題。

LVS的基本原理:在有初始匹配對的情況下通過跟蹤匹配更多的器件或線網(wǎng);在沒有初始匹配對的情況下使用簽名劃分等方法獲得初始匹配對,然后再從初識匹配對出發(fā)繼續(xù)跟蹤。如此循環(huán),直至版圖與電路圖全部匹配或無新的匹配對產(chǎn)生為止。對于未能匹配的器件和線網(wǎng),嘗試根據(jù)其周圍環(huán)境進(jìn)行修復(fù)并進(jìn)行匹配;如果修復(fù)失敗,則作為錯誤寫出至報告中。

其中,簽名劃分方法是根據(jù)器件給每種器件賦予相應(yīng)簽名值,根據(jù)簽名值的不同將器件劃分成不同集合;根據(jù)線網(wǎng)與器件的連接關(guān)系,線網(wǎng)也會被賦予簽名值,劃分為不同集合。

圖5-118(a)為版圖提取網(wǎng)表,圖5-118(b)為由電路圖導(dǎo)出網(wǎng)表,LVS報告版圖存在一個開路錯誤。

3.電氣規(guī)則檢查(ERC)

ERC用于檢查版圖的電氣規(guī)則,如開路、短路、路徑檢查等。ERC基于版圖進(jìn)行建成區(qū),不需要電路圖,可以快速檢查并直觀定位設(shè)計中存在的常見問題。通常ERC功能包含于LVS工具中。

4.版圖比對檢查(LVL)

LVL工具主要應(yīng)用在兩個方面:1)版圖改版時設(shè)計者需要借助LVL工具查看修改前后的差異;2)制版時版圖數(shù)據(jù)通常被扁平化,LVL工具用于比對版圖扁平化前后的差異。

LVL檢查涉及的關(guān)鍵技術(shù)有層次處理、掃描線算法、數(shù)據(jù)壓縮、并行計算等。另外,由于涉及的規(guī)則比較少,可以針對不同類型的版圖采用一些特殊的加速技巧。

工藝發(fā)展到40nm和更先進(jìn)的工藝后,因線距變小,層厚度也變小,線與周圍的環(huán)境以及線間耦合的影響變大,光學(xué)效應(yīng)的影響也凸顯出來。傳統(tǒng)的版圖驗證工具所采用的二維檢查技術(shù)已經(jīng)不能滿足檢查需求,需要利用三維和光學(xué)分析技術(shù)以處理各種效應(yīng)的影響,開發(fā)新的檢查功能,例如模式匹配(Pattern Match)、雙重/多重曝光(Double/MulTI- pattern)、智能啞元填充(Smart Fill)等。

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<