在高速或高頻電路板中,PCB中的寄生效應(yīng)非常明顯,這些寄生電容和寄生電感會引起串?dāng)_、EMI、信號完整性等問題。在處理高頻、高速和混合信號PCB時,需要做一些特殊處理,以減小寄生效應(yīng)對信號的影響。

為了減小寄生電容和電感的影響,我們需要知道它們是怎么產(chǎn)生的,才能對癥下藥。本節(jié)我們先來了解如何計算PCB的寄生電容和寄生電感,然后討論如何減小它們的影響。

PCB上的導(dǎo)體一般有走線和過孔(焊盤、覆銅等都可以等效為走線),二者的結(jié)構(gòu)完全不同,所以我們在討論寄生效應(yīng)時,需要把這兩種結(jié)構(gòu)分別分析。

1)寄生電容

信號線/焊盤的寄生電容:

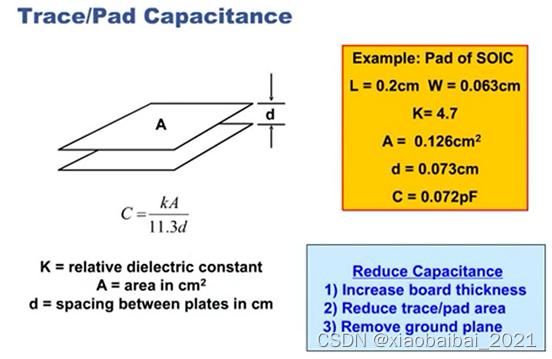

我們知道,平板電容器的電容計算公式為:C=ε0*S/d;其中ε0是介電常數(shù),S是相對的兩個平板的面積,d是兩個平板的距離。可以知道,在介電常數(shù)一定的情況下,正對的面積S越大、距離d越小,則電容越大。

由于在PCB的同一層上,信號線與信號線之間等效的正對面積很小,距離相對于相鄰層之間的間距也很大,所以,同一層內(nèi)的走線之間的寄生電容認(rèn)為很小可以忽略;把走線覆蓋的面積當(dāng)作平板電容器的面積,相鄰層的間距作為平板電容器的間距,忽略掉其他因素引起的小電容,寄生電容的產(chǎn)生就可以簡化為平板電容器的電容。

可以如下圖計算:(A為面積、d為與相鄰參考層的間距,例子中K=4.7是把PCB板材的介電常數(shù)考慮進(jìn)去了)

從這個計算公式可以看出,如果想要減小信號線、焊盤的寄生電容,在設(shè)計PCB時,一是要減小銅皮覆蓋的總面積;二是要增加層間距(在實際操作時,可以選用層間距大的PCB層疊結(jié)構(gòu),或者挖空相鄰層的參考面)

過孔的寄生電容:

過孔的寄生電容,不能等效成平板電容器,一般用以下公式計算:

(其中D1為過孔的外徑、D2為過孔周圍銅皮挖空部分的圓直徑、T為PCB厚度、εr為板材的相對磁導(dǎo)率)

從以上計算公式可以看出,要想減小過孔的寄生電容,需要使用小孔徑的過孔、加大過孔和銅皮的間距、選用更薄的PCB板材。

2)寄生電感

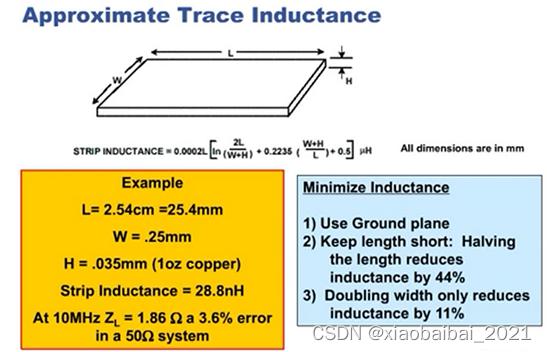

信號線/焊盤的寄生電感

計算方法如下:(W是線寬、L是線長,H是銅厚)

這個公式看起來比較復(fù)雜,實際上,對寄生電感影響最大的是線長L,將L的長度縮短是減小信號線寄生電感的最有效方法。

過孔的寄生電感:

計算方法如下:(h是板厚、D是過孔直徑)

從公式上可以看出,要減小過孔的寄生電感,需要減小板厚、增大過孔直徑。

好了,本節(jié)的內(nèi)容就分享到這了。

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<