隨著晶體管按比例縮小,它們需要更薄的溝道來實現(xiàn)足夠的溝道控制。然而,在硅中,表面粗糙度散射會降低遷移率,從而將最終溝道厚度限制在 3 納米左右。

二維過渡金屬二硫族化物 (TMD:Two-dimensional transition metal dichalcogenides),例如 MoS2和 WSe2,在一定程度上具有吸引力,因為它們避免了這種限制。由于沒有平面外懸空鍵和原子光滑的界面(With no out-of-plane dangling bonds and atomically smooth interfaces),TMD 即使在亞埃厚度下也能避免散射引起的遷移率下降。

盡管如此,TMD 仍代表著硅甚至硅鍺現(xiàn)狀的根本改變。材料生長、觸點形成和器件制造都不同于相應(yīng)的硅工藝。目前,基礎(chǔ)材料研究和器件開發(fā)并行進行。在實驗室設(shè)備中獲得良好結(jié)果的材料和工藝可能不適合批量生產(chǎn)。

例如,迄今為止大多數(shù) TMD 設(shè)備演示都依賴于層轉(zhuǎn)移(layer transfer )技術(shù)。這種方法從一個獨立的薄膜開始,它可以生長在藍寶石等兼容基板上,也可以從大塊材料上剝離下來。可以使用幾種方法中的任何一種將膜轉(zhuǎn)移到可能已經(jīng)包括底柵結(jié)構(gòu)的準備好的目標襯底。

層轉(zhuǎn)移帶來了明顯的成本和產(chǎn)量挑戰(zhàn)。在 12 月的 IEEE 國際電子器件會議 (IEDM) 上展示的工作中,英特爾的 CJ Dorow 及其同事表明,單柵極 MoS2器件的性能因轉(zhuǎn)移過程而下降。他們在源極和漏極區(qū)域觀察到 TMD 分層。去掉的低 k 電介質(zhì)層也在 TMD/氧化物界面留下殘留物。半導(dǎo)體晶圓廠更喜歡更“類硅”工藝的靈活性和成本效益,TMD 直接沉積在目標基板上。

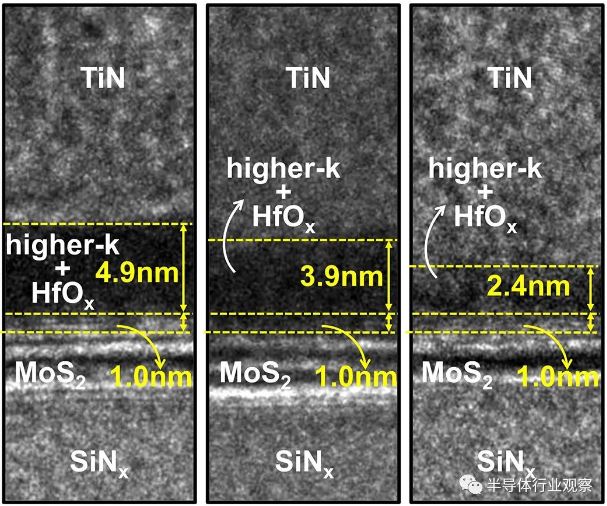

一般而言,TMD 生長需要在薄膜質(zhì)量和最小化溝道厚度的需求之間進行權(quán)衡。原子級沉積 (ALD) 電介質(zhì)和通過化學(xué)氣相沉積 (CVD) 生長的 TMD 都容易出現(xiàn)針孔和其他缺陷。盡管如此,在 12 月的 IEEE IEDM 上發(fā)表的幾篇論文表明,該行業(yè)正在朝著直接沉積 TMD 的方向取得進展。例如,北京大學(xué)的 Xinhang Shi 及其同事使用低壓 CVD直接在 SiO2上生長 WSe2雙層。非常高的溫度過程 (890°C) 使器件具有425 μA/μm 的創(chuàng)紀錄高 Ids。薄膜特性與氧化物厚度無關(guān)。或者,臺積電的 Yun-Yan Chung 及其同事使用鎢墊作為 WS2生長的種子層,構(gòu)建具有兩個和三個堆疊溝道的設(shè)備

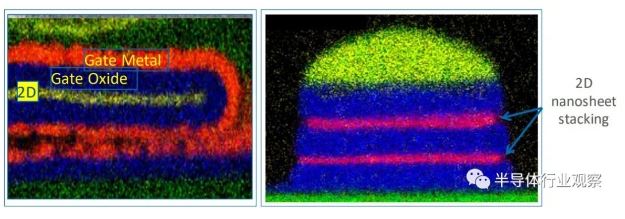

圖 1:完全被柵極堆疊包圍的單層 MoS2 納米片的 TEM 橫截面。較小的圖像顯示 EDX 元素映射。

用于摻雜和閾值電壓控制的電介質(zhì)

完整的 CMOS 工藝不僅僅是簡單地沉積溝道材料。該過程還必須促進空穴和電子傳導(dǎo)。在 TMD 中,摻雜、電介質(zhì)沉積和 Vth Tuning彼此密不可分。由于目前不可能對半導(dǎo)體本身進行摻雜,因此器件依靠覆蓋層來調(diào)節(jié)傳導(dǎo)并提供 nFET 或 pFET 行為。即使確定了合適的材料,TMD 表面的二維特征也會使覆蓋層沉積復(fù)雜化。除了晶界和其他缺陷外,沉積氧化物的潛在成核位置非常少。

WSe2是一種雙極性材料,這意味著費米能級在施加電場的情況下在價帶和導(dǎo)帶之間移動。因此,相同的材料可以傳導(dǎo)電子或空穴

臺積電的幾個不同小組一直在從不同角度研究WSe2傳導(dǎo)和摻雜。一組使用氧等離子體將WSe2半導(dǎo)體單層轉(zhuǎn)化為Ox。該過程是自限性的,不影響底層的WSe2材料,最終的摻雜水平取決于起始材料中的層間耦合。較厚的起始材料具有較高的價帶邊緣,從而在轉(zhuǎn)化為氧化物后導(dǎo)致更高的摻雜。在 Ang-Sheng Chou 介紹的工作中,另一個 TSMC 小組將 MoO x蓋層用于 pFET 器件和 SiON x對于 nFET 器件。連同下面討論的新穎接觸技術(shù),這些覆蓋層提供了一些迄今為止最好的 TMD 晶體管結(jié)果。

在普渡大學(xué),研究人員使用六方氮化硼 (hBN:hexagonal boron nitride) 作為界面層以促進電介質(zhì)沉積。他們的工作強調(diào)了“缺陷”(defects)和“陷阱”(traps)之間的區(qū)別。正如他們所解釋的那樣,缺陷既可能發(fā)生在電介質(zhì)體內(nèi)部,也可能發(fā)生在電介質(zhì)——半導(dǎo)體界面處。然而,只有當(dāng)費米能級穿過缺陷能帶時,缺陷才會變成陷阱。在 hBN 中封裝單層 MoS2降低了亞閾值擺動并增加了V th,這意味著界面陷阱被消除或停用。hBN 層似乎可以阻擋 TMD 薄膜上的吸收物,這是電荷陷阱的潛在來源。

不幸的是,hBN 本身并不是一種合適的電介質(zhì)。它也是一種類石墨材料,具有弱的面外鍵合,使得直接在 hBN 上生長電介質(zhì)具有挑戰(zhàn)性。Purdue 小組使用鉭種子層進行電介質(zhì)沉積。相對于更常見的鋁種子,他們發(fā)現(xiàn)亞閾值擺幅退化較少,V th偏移也減少。

圖 2:通過系統(tǒng)地分析關(guān)鍵工藝參數(shù),TSMC 的研究人員將鉿基電介質(zhì)與CVD生長的 MoS2集成在一起,構(gòu)建了EOT ~1nm和近乎理想的亞閾值擺動的頂柵 nFET。這項工作特別值得注意,因為在 TMD 上沉積無針孔電介質(zhì)是出了名的困難。

堆疊溝道和接觸

由于需要堆疊溝道,實際設(shè)備可能會看到更復(fù)雜的工藝。單個 TMD 單層不能承載與硅納米片一樣多的電流,因此設(shè)備將需要多個堆疊的 TMD 片。與堆疊的硅納米片一樣,最小化片之間的間距可以減少寄生電容。

圖3:二維MoS2堆疊納米帶結(jié)構(gòu)。

由于 TMD 層非常薄,Yun-Yan Chung 的團隊指出機械穩(wěn)定性也是一個問題。他們使用犧牲電介質(zhì)來提高剛度并防止制造過程中下垂。內(nèi)部墊片和金屬觸點有助于將溝道固定在成品設(shè)備中。

自從這些器件被提出以來,TMD 晶體管構(gòu)造的最后一步,即與電路的其余部分接觸,就受到了廣泛的研究關(guān)注。盡管如此,接觸電阻和間隔電阻仍占二維晶體管總器件電阻的 80%,比硅接觸電阻和間隔電阻的貢獻要大得多。最近使用鉍和銻等半金屬的研究為 nFET 提供了良好的結(jié)果,但 pFET 觸點仍然是一個未解決的問題。

正如 Ang-Sheng Chou 的團隊所解釋的那樣,大多數(shù)提議的接觸都有一個不幸的空穴傳導(dǎo)能帶排列。他們的工作利用了 WSe2的雙極性特性,將單一的銻/鉑堆棧用于 nFET 和 pFET 器件。銻(Sb,功函數(shù) 4.4 eV)提供緩沖層,最大限度地減少對底層半導(dǎo)體的損壞。鉑(Pt,功函數(shù) 5.6 eV)調(diào)節(jié)功函數(shù)。兩種材料的比例可調(diào),以實現(xiàn) nFET 和 pFET 所需的功函數(shù)。最后,他們報告了電子和空穴的低勢壘高度、低接觸電阻和約 150 μA/μm 的導(dǎo)通電流。

二維半導(dǎo)體的下一步是什么?

與結(jié)果本身相比,來自英特爾和臺積電等公司的大量報告表明,基于 TMD 的晶體管是接替硅的重要候選者。雖然在過去幾年中,該行業(yè)已經(jīng)開始闡明此類設(shè)備的潛在設(shè)計——MoS 2或 WSe 2溝道,具有半金屬接觸——穩(wěn)健的、可制造的制造工藝尚未出現(xiàn)。

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<