1947年12月,人類第一代半導(dǎo)體放大器件在貝爾實(shí)驗(yàn)室誕生,其發(fā)明者肖克利及其研究小組成員將這一器件命名為晶體管。

今年是晶體管誕生的第75年,其發(fā)展已經(jīng)陷入了瓶頸,我們是否還能找到新方法延續(xù)摩爾定律?

2022年,我們依然需要新的晶體管

為了紀(jì)念晶體管被發(fā)明75周年,IEEE(電氣與電子工程師協(xié)會)電子器件分會(E lectron Device Society )組織了一場活動,在此活動上有Fin-FET的發(fā)明者胡正明教授對晶體管的過去進(jìn)行回顧。

我們的世界是否還需要更好的晶體管?

胡正明在演講中給出了肯定的回答,并給出了三個理由:

第一,隨著晶體管的改進(jìn),人類掌握了從未想象到的新能力,例如計(jì)算和高速通信、互聯(lián)網(wǎng)、智能手機(jī)、內(nèi)存和存儲、計(jì)算機(jī)技術(shù)、人工智能,可以想象的是,未來還會有其他新技術(shù)涌現(xiàn)出來;

第二,晶體管廣泛的應(yīng)用正在改變所有技術(shù)、工業(yè)和科學(xué),同時半導(dǎo)體技術(shù)的演進(jìn)不想其他技術(shù)一樣受到其材料和能源使用的限制,IC使用相對較少的材料就可以生產(chǎn),并且正在變得越來越小,使用的材料也越來越少,IC本身也在變得更快更高效;

第三,理論而言,信息處理所需的能量依然可以減少到今天所需能量的千分之一以下,雖然我們可能還不知道如何達(dá)到這種理論效率,但我們知道這在理論上可行,而其他大部分技術(shù)的能源效率已經(jīng)達(dá)到理論極限。

2030年,單顆芯片可容納1萬億個晶體管

需要新的晶體管是事實(shí),但研發(fā)制造出新的晶體管已經(jīng)舉步維艱,無論是在經(jīng)濟(jì)上還是在技術(shù)上,都遇到了新的困難。

近期,F(xiàn)in-FET的進(jìn)步能夠帶來的性能提升和功耗降低變得越來越有限,業(yè)界正在采用一種新的3D CMOS結(jié)構(gòu)的環(huán)柵(GAA)制造新的晶體管。

英特爾為了進(jìn)一步縮小晶體管的三維尺寸,用RibbonFET的結(jié)構(gòu)實(shí)現(xiàn)了GAA,但是發(fā)現(xiàn)源極和漏極之間的距離進(jìn)一步縮小的同時,會產(chǎn)生比較明顯的短溝道效應(yīng)而漏電。

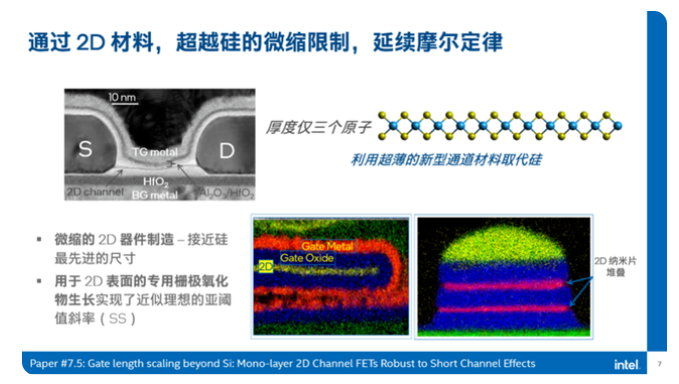

如果將傳統(tǒng)的通道材料硅材料換成非硅的新材料,就能改善這種情況。學(xué)術(shù)界也有了一些相關(guān)的研究,使用一種名為過渡金屬硫化物的材料作為通道材料,這種材料只有三個原子的厚度,電子流動性好,作為通道材料有天然優(yōu)勢。

在這種2D材料方面,針對這種材料,英特爾也做了很多研究和分析,并在會議上展示了一種全環(huán)繞柵極堆疊式納米片結(jié)構(gòu),使用了厚度僅三個原子的2D通道材料,同時在室溫下實(shí)現(xiàn)了近似理想的低漏電流雙柵極結(jié)構(gòu)晶體管開關(guān)。

除此之外,3D封裝技術(shù)也能進(jìn)一步提升單個設(shè)備中晶體管的數(shù)目。

英特爾在3D封裝方面也取得了新進(jìn)展,與IEDM 2021上公布的成果相比,英特爾IEDM 2022上展示的最新混合鍵合研究將功率密度和性能又提升了10倍。

另外,通過混合鍵合技術(shù)將互連間距繼續(xù)微縮到3微米,英特爾實(shí)現(xiàn)了與單片式系統(tǒng)級芯片(system-on-chip)連接相似的互連密度和帶寬。加上將多芯片互連的工藝?yán)镄枰牟牧蠐Q成無機(jī)材料,以便于與封裝廠多種工藝要求兼容。

雖然進(jìn)一步實(shí)現(xiàn)晶體管的微縮是一件需要耗費(fèi)巨大財(cái)力和人力的事情,但依然有像英特爾這樣的企業(yè)在持續(xù)投入研發(fā),并對晶體管的未來抱有期望。

英特爾認(rèn)為,從2023年到2030年,單個設(shè)備中晶體管的數(shù)目將翻10倍,即從1千億個晶體管到1萬億個晶體管。

要實(shí)現(xiàn)這個目標(biāo),需要整個行業(yè)持續(xù)投入研發(fā),嘗試更多可行的技術(shù)。

中國科學(xué)家設(shè)計(jì)1nm晶體管驚艷全世界

在不久之前,我們曾披露,復(fù)旦大學(xué)微電子學(xué)院的周鵬教授,包文中研究員及信息科學(xué)與工程學(xué)院的萬景研究員,創(chuàng)新地提出了硅基二維異質(zhì)集成疊層晶體管技術(shù)。

該技術(shù)利用成熟的后端工藝將新型二維材料集成在硅基芯片上,并利用兩者高度匹配的物理特性,成功實(shí)現(xiàn) 4 英寸大規(guī)模三維異質(zhì)集成互補(bǔ)場效應(yīng)晶體管。

該技術(shù)成果的文章發(fā)表在 nature electronics,并受到大家廣泛關(guān)注,以下為引言部分——

大規(guī)模集成電路的特征尺寸縮小依賴于新型材料、器件架構(gòu)和工藝流程的持續(xù)創(chuàng)新,大數(shù)據(jù)和即時數(shù)據(jù)的傳輸逐漸成為信息技術(shù)發(fā)展的主要趨勢。目前已經(jīng)提出了諸如鰭型場效應(yīng)晶體管(FinFET)、全柵(GAA)以及垂直堆疊的叉片和CFET器件等巧妙的器件架構(gòu),縮小晶體管的尺寸可增加集成密度并提高性能。其中,CFET架構(gòu)(PMOS和NMOS器件垂直堆疊并由同一公共柵極控制)已被證明可以減少42-50%的面積,性能提高7%,與傳統(tǒng)的互補(bǔ)金屬氧化物半導(dǎo)體(CMOS)器件相比,成本降低了12%10。因此,它提供了將摩爾定律進(jìn)一步擴(kuò)展到1nm節(jié)點(diǎn)以下的巨大應(yīng)用前景。

最近,Intel公司報(bào)道的3D堆疊GAA n/p-Si納米帶CMOS展示了最先進(jìn)的Si工藝技術(shù),其顯示出高集成密度和優(yōu)異的短溝道控制能力。這種3D/3D堆疊CFET架構(gòu)是硅器件中的一個了不起的突破。然而,硅基的CFET面臨許多制造挑戰(zhàn),例如復(fù)雜的工藝流程、對熱預(yù)算的額外要求、源極和漏極外延生長的困難以及電子/空穴遷移率失配和閾值電壓(VTH)調(diào)諧的補(bǔ)償。為了通過雙金屬柵極調(diào)整閾值電壓,不可避免地需要額外的光刻、蝕刻和沉積工藝,這使得工藝相當(dāng)復(fù)雜。在電子器件中使用二維半導(dǎo)體的研究已經(jīng)開始從單一器件的工作過渡到IC的開發(fā)。然而,在將二維系統(tǒng)引入IC行業(yè)之前,仍有許多挑戰(zhàn)需要解決,包括晶圓級制造、性能匹配、,將2D半導(dǎo)體并入硅互補(bǔ)金屬氧化物半導(dǎo)體基IC是一種替代方法,可用于彌合新興材料與工業(yè)應(yīng)用之間的差距。然而,這需要與傳統(tǒng)硅技術(shù)兼容的2D材料的器件架構(gòu)和集成方法。

在本文中,我們提出了一種異質(zhì)CFET架構(gòu),它結(jié)合了晶圓級絕緣體上硅(SOI)pFET和二硫化鉬(MoS2)nFET。SOI技術(shù)自然能夠抑制短溝道效應(yīng)(SCE),降低寄生電容,并具有優(yōu)異的亞閾值特性和與現(xiàn)代硅工藝的完全兼容性,全耗盡SOI(FD-SOI)技術(shù)已經(jīng)用于先進(jìn)的VLSI電路,低至22 nm和14 nm技術(shù)節(jié)點(diǎn)。另一方面,2D半導(dǎo)體在超大規(guī)模CMOS、光電子和傳感器中顯示出良好的潛力由于其原子厚度、豐富的帶結(jié)構(gòu)和高的表面與體積比。MoS2中的電子遷移率與硅中的空穴遷移率相似,可以使用化學(xué)氣相沉積(CVD)在晶片規(guī)模上合成高質(zhì)量的MoS2,并在低溫下轉(zhuǎn)移。我們通過遷移率匹配(具體地,通過選擇MoS2層的厚度)緩解nFET/pFET中電子和空穴之間的遷移率失配問題,堆疊的n/p金屬柵極,并引入額外的控制柵極。我們使用該方法創(chuàng)建了一個SOI–MoS2 CFET反相器,在電源電壓(VDD)為3V時電壓增益高達(dá)142.3,在100 mV的低VDD時電壓增益為1.2,功耗為64 pW。我們還通過開發(fā)SOI–MoS2 CFETs的4英寸制造工藝來驗(yàn)證該方法的制造潛力。

如果對具體內(nèi)容感興趣,可前往全文閱讀。

1nm的晶體管候選,復(fù)旦大學(xué)團(tuán)隊(duì)CFET研究全披露

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<