TechInsights發(fā)布臺(tái)積電2nm和Intel 18A工藝細(xì)節(jié)對(duì)比

2025-02-14

來(lái)源:芯智訊

2月14日消息,近日,半導(dǎo)體研究機(jī)構(gòu)TechInsights 和 SemiWiki 發(fā)布了英特爾和臺(tái)積電此前在“國(guó)際電子設(shè)備會(huì)議”(IEDM) 上披露的有關(guān)即將推出的Intel 18A(1.8nm級(jí))和 臺(tái)積電N2(2nm級(jí))工藝技術(shù)的關(guān)鍵細(xì)節(jié)。根據(jù) TechInsights 的分析,Intel 18A 可以提供更高的性能,而臺(tái)積電N2可能會(huì)提供更高的晶體管密度。

能效的提升

在三星14nm / 臺(tái)積電16nm 節(jié)點(diǎn)上,三星和臺(tái)積電都生產(chǎn)了蘋果A9 處理器。經(jīng)過(guò)當(dāng)時(shí)Tom's hardware的測(cè)試發(fā)現(xiàn),與臺(tái)積電16nm相比,三星14nm版本的功耗性能略好。TechInsights認(rèn)為 A9 首先是基于三星14nm制程設(shè)計(jì)的,因此這可能只是反映了移植到臺(tái)積電導(dǎo)致的能效(Power Efficiency)損失。然而,實(shí)際上兩者之間的能效非常接近。從 14nm/16nm 到 10nm、7nm、5nm、3nm,再到現(xiàn)在的 2nm,三星和臺(tái)積電都為每個(gè)節(jié)點(diǎn)提供了相對(duì)于前一個(gè)節(jié)點(diǎn)的相對(duì)功耗的改進(jìn)。

在 10nm 時(shí),臺(tái)積電提供了比三星更大的功耗降低,并保持了這一領(lǐng)先地位,直到 3nm 時(shí),三星率先采用了全環(huán)繞柵極(Gate All Around ,GAA)晶體管幾乎是,提供了足夠大的改進(jìn),在很大程度上縮小了與臺(tái)積電 3nm FinFET 工藝在能效方面的差距(GAA 與 FinFET 相比有望提供更大的能效改進(jìn))。

根據(jù)臺(tái)積電論文公布數(shù)據(jù)顯示,與上一代的 3nm(N3E)節(jié)點(diǎn)相比,臺(tái)積電N2制程在相同電壓下可以將功耗降低 24% 至 35%,或?qū)⑿阅芴岣?5%,晶體管密度是上一代 3nm 工藝高 1.15 倍。而這些指標(biāo)的提升主要得益于臺(tái)積電的新型全環(huán)繞柵極(GAA)納米片晶體管,以及 N2 NanoFlex 設(shè)計(jì)技術(shù)協(xié)同優(yōu)化和其他一些增強(qiáng)功能實(shí)現(xiàn)的。

作為對(duì)比,三星SF2(2nm)相比上一代SF3(3nm)功耗降低了約25%,而臺(tái)積電則降低了平均約30%左右,再次保持了領(lǐng)先優(yōu)勢(shì)。

其中,臺(tái)積電 N2 的功耗系數(shù)預(yù)計(jì)為 0.14,而三星的 SF2 為 0.17。不幸的是,沒(méi)有足夠的數(shù)據(jù)將 Intel 18A 添加到這部分的對(duì)比分析中。

臺(tái)積電在其論文中展示了不同工藝節(jié)點(diǎn)下每瓦特功率效率和性能的關(guān)系圖。以下這張功率效率(即能效)“圖1”出現(xiàn)在臺(tái)積電論文的一個(gè)版本中,盡管它并不在論文集中最終發(fā)表的論文的版本中。

△圖1:臺(tái)積電各工藝節(jié)點(diǎn)的電源效率(圖片來(lái)源:臺(tái)積電論文)

TechInsights根據(jù)該圖形進(jìn)行分析,將N28(28nm)的柱狀圖的高度定義為“1”,然后再將其他柱狀圖與之進(jìn)行匹配,最終得到了如“圖2”,N28到N2總體能效改進(jìn)約不到9倍,遠(yuǎn)低于官方宣稱的超過(guò)15倍。

△圖2:TechInsights制作的臺(tái)積電各工藝節(jié)點(diǎn)的電源效率(圖片來(lái)源:TechInsights)

可以看到,從 N28 到 N10 的節(jié)點(diǎn)匹配良好,但從 N7 開(kāi)始,圖表上的條形顯示每個(gè)節(jié)點(diǎn)的能效改進(jìn)都要比臺(tái)積電宣布的少的多。臺(tái)積電的示意圖上N3 到 N2 條形顯示能效有 55% 的改進(jìn),但實(shí)際宣布的改進(jìn)僅為30%左右。

目前尚不清楚是什么導(dǎo)致了這種差異,但這是一個(gè)很大的脫節(jié)。這可能就是臺(tái)積電從最終論文中刪除了能效改進(jìn)圖表的原因。

性能

與上面的能效分析類似,在三星14nm/臺(tái)積電16nm 上,蘋果A9處理器在 這2個(gè)工藝上具有相同的性能。將兩個(gè)制程標(biāo)準(zhǔn)化為“1”,并應(yīng)用兩家公司宣布的節(jié)點(diǎn)到節(jié)點(diǎn)性能改進(jìn),可以比較每個(gè)節(jié)點(diǎn)的性能。還可以將英特爾添加到分析中,并根據(jù)英特爾逐個(gè)節(jié)點(diǎn)性能公告進(jìn)行正向計(jì)算。

據(jù)此計(jì)算,TechInsights得出的 Intel 18A 的性能值為2.53,臺(tái)積電N2的性能值為2.27,三星SF2的性能值為2.19。也就是說(shuō),Intel 18A 在 2nm 級(jí)工藝中具有最高性能,臺(tái)積電N2位居第二,三星SF2位居第三。

面積

TechInsights還分析了兩個(gè)與制程工藝當(dāng)中“面積”相關(guān)的因素,一個(gè)是高密度邏輯單元晶體管密度,第二個(gè)是 SRAM 單元尺寸。

TechInsights 已經(jīng)對(duì)臺(tái)積電N3E 工藝進(jìn)行了詳細(xì)的逆向工程工作,擁有計(jì)算標(biāo)準(zhǔn)高密度邏輯單元晶體管密度所需的所有資料。

同樣,TechInsights分析了三星SF3(3nm)和 SF3E 制程。臺(tái)積電和 三星在公開(kāi)聲明中都提供了其 2nm 的密度改進(jìn)值。就英特爾而言,TechInsights 也有保密協(xié)議下Intel 18A 的所有間距數(shù)據(jù),雖然TechInsights不能透露具體的間距數(shù)值,但可以進(jìn)行密度比較。

對(duì)于高密度邏輯單元,臺(tái)積電在密度上遙遙領(lǐng)先于三星和英特爾,英特爾排名第二,三星排名第三。其中,臺(tái)積電的高密度邏輯單元晶體管密度為 313 MTx/mm2、英特爾為238 MTx/mm2,三星則為231 Mtx/mm2。

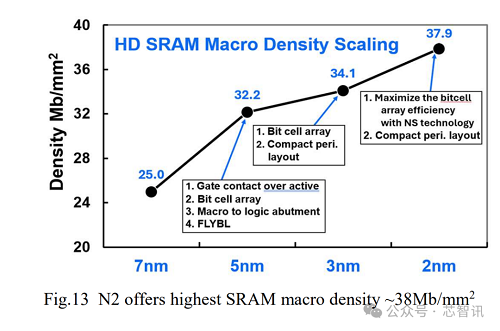

如前所述,臺(tái)積電論文當(dāng)中雖然不包括 SRAM 單元大小,但有一張 SRAM 密度與節(jié)點(diǎn)的關(guān)系圖,參見(jiàn)“圖3”。

△SRAM 陣列密度與節(jié)點(diǎn)的關(guān)系(圖片來(lái)源:臺(tái)積電論文)

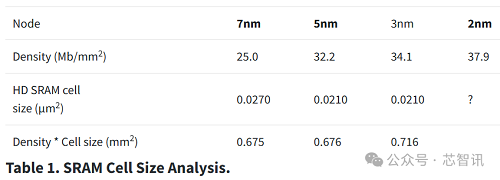

SRAM 陣列不僅包括 SRAM 單元,還包括開(kāi)銷,例如 7nm 有 25.0 Mb/mm2,7nm 的 SRAM 單元尺寸為 0.0270um2。如果將 25.0Mb 乘以 SRAM 單元大小,則得到 0.675mm2。1.000 和 0.675mm2 之間的差異是開(kāi)銷,并且每個(gè)節(jié)點(diǎn)之間不是恒定的,見(jiàn)表 1。

△表1:SRAM Cell尺寸分析(圖片來(lái)源:TechInsights)

從“表1”中可以看出,陣列中的 SRAM 單元面積從 ~68% 到 ~72% 不等。此外,從“表1”中還可以看出,即使陣列密度從 32.2 Mb/mm2 增加到 34.1 Mb/mm2,5nm 和 3nm 處的 HD SRAM 單元尺寸也是相同的。

如果假設(shè)單元占陣列的 ~68%,則 2nm SRAM 單元大小可能為 ~0.0178um2,但如果假設(shè) ~72%,則為 ~0.0189um2。

此前,英特爾在論文中已經(jīng)公布其Inel 18A的HD SRAM 單元大小為 0.0210um2(實(shí)現(xiàn)了大約 31.8 Mb/mm2 的 SRAM 密度),因此在任何一種情況下,臺(tái)積電的SRAM單元將更小,預(yù)計(jì)它也將小于三星的 SRAM 單元大小。

良率

對(duì)于尖端制程來(lái)說(shuō),良率是極為重要的議題。有很多報(bào)道稱三星第二代3nm正因?yàn)榱悸蕟?wèn)題而苦苦掙扎(據(jù)稱僅20%),并因良率低而失去客戶。此前也有一些報(bào)道稱Intel 18A 良率為10%,不過(guò)該消息隨后遭到了官方否認(rèn)。

在論文中,臺(tái)積電報(bào)告說(shuō),其256Mb SRAM 陣列的平均良率為 >80%,峰值良率為 >90%。在開(kāi)發(fā)階段的這些良率數(shù)據(jù)表明具有出色的低缺陷密度。除了在 SRAM 陣列中測(cè)試的那些之外,還有其他因素,但這些都是令人印象深刻的結(jié)果。

對(duì)于Intel 18A良率只有10%的傳聞,TechInsights也強(qiáng)調(diào),其有兩個(gè)獨(dú)立的可靠消息來(lái)稱,該傳聞根本不是真的,實(shí)際的良比這要好得多。

硅片價(jià)格

對(duì)于2nm晶圓代工的價(jià)格,一個(gè)廣為流傳的數(shù)字是,臺(tái)積電將對(duì)其每片2nm晶圓將收取約30,000美元的費(fèi)用。

此前,在 3nm 投入生產(chǎn)之前,TechInsights曾根據(jù)其預(yù)測(cè)模型分析認(rèn)為每片3nm晶圓的價(jià)格為 < 20,000 美元,3nm 投入生產(chǎn)后,確定了該預(yù)測(cè)是正確的,批量?jī)r(jià)格確實(shí)為 <20,000 美元。而對(duì)于2nm晶圓價(jià)格,預(yù)計(jì)為<30,000美元。

如果2nm晶圓價(jià)格為30,000美元,達(dá)到了3nm晶圓的1.5 倍,但是密度僅是3nm晶圓的1.15 倍,這也意味著晶體管成本的急劇增加,這將使得客戶難以接受。因此,還有報(bào)道稱,通常是臺(tái)積電每個(gè)最新節(jié)點(diǎn)的主要客戶的蘋果公司,可能會(huì)因?yàn)?nm高昂的價(jià)格原因,進(jìn)而放棄率先采用2nm。

這里討論價(jià)格的另一個(gè)主要影響因素是大批量晶圓價(jià)格的定價(jià)遠(yuǎn)低于小批量晶圓價(jià)格,因此在任何討論中都需要考慮訂單數(shù)量。

如果臺(tái)積電將 2nm 晶圓定價(jià)為 30,000 美元/晶圓,他們將給客戶帶來(lái)很大的壓力,可能會(huì)迫使他們轉(zhuǎn)向英特爾的Intel 18A和三星2nm。

背面供電

臺(tái)積電關(guān)于2nm制程的論文沒(méi)有涉及背面供電技術(shù),但英特爾的Intel 18A以及三星2nm工藝都將實(shí)現(xiàn)背面供電。

根據(jù)進(jìn)展來(lái)看,Intel 18A有望成為2025年首個(gè)實(shí)施背面供電技術(shù)的工藝制程。2026年,三星的SF2P工藝也將實(shí)施背面供電。最后,預(yù)計(jì)臺(tái)積電不會(huì)在其 2nm 工藝變體上實(shí)現(xiàn)背面供電技術(shù),可能需要等到 2026年或2027年才能在其 A16 工藝上實(shí)施。預(yù)計(jì) A16 背面供電將是一種直接的背面連接,可以提供比英特爾和三星的實(shí)現(xiàn)更小的軌道高度。

由于英特爾是三家公司中最注重性能的公司,因此他們首先實(shí)施背面供電是有道理的。

TechInsights稱,HPC客戶想要背面供電技術(shù)來(lái)支持其芯片,但是由于成本原因,移動(dòng)客戶并不想要它。

對(duì)于多個(gè)節(jié)點(diǎn),我們可能會(huì)看到有背面供電和沒(méi)有背面供電的版本,并且考慮到它對(duì)Metal 0 的影響,設(shè)計(jì)規(guī)則可能會(huì)有所不同。

除此之外,為了實(shí)現(xiàn)最高性能,預(yù)計(jì)鉬將首先引入通孔,然后引入關(guān)鍵互連。這可能導(dǎo)致 HPC 的節(jié)點(diǎn)在背面電力輸送和鉬金屬化之間分裂,而對(duì)于移動(dòng)設(shè)備,則沒(méi)有背面電力和銅金屬化。

其他

論文中最后一個(gè)有趣的項(xiàng)目是關(guān)于 “flat passivation” 的評(píng)論。許多工藝都有頂部鋁金屬層,鈍化遵循金屬輪廓,如果需要混合鍵合之類的東西,晶圓表面必須是平坦的。平鈍化可能是平坦化的頂層,以實(shí)現(xiàn)鍵合。

量產(chǎn)時(shí)間

根據(jù)計(jì)劃,Intel 18A 將于 2025 年年中進(jìn)入量產(chǎn),屆時(shí)英特爾將開(kāi)始生產(chǎn)其酷睿 Ultra 3 系列“Panther Lake”處理器,該處理器將于今年晚些時(shí)候上市。

相比之下,臺(tái)積電的 N2 計(jì)劃于 2025 年底進(jìn)行大批量生產(chǎn),該節(jié)點(diǎn)生產(chǎn)的第一批產(chǎn)品最早要到 2026 年年中才能上市,相關(guān)產(chǎn)品預(yù)計(jì)將于 2026 年秋季上市。

三星沒(méi)有透露其 SF2 進(jìn)入 HVM 的確切時(shí)間,只表示“2025 年”,有可能會(huì)是在2025年下半年。

小結(jié)

臺(tái)積電披露了一種 2nm 工藝,這可能是可用的密度最高的 2nm 級(jí)工藝。與三星相比,它似乎也是最節(jié)能的。在性能方面,Intel 18A則可能更強(qiáng)。早期的良率方面,臺(tái)積電2nm更具優(yōu)勢(shì),但是 30,000 美元/晶圓的定價(jià)客戶將難以接受,并且可能為英特爾和三星帶來(lái)?yè)屨际袌?chǎng)份額的機(jī)會(huì)。