第一部分 設計概述 /Design Introduction

目前主流的目標檢測算法都是用CNN來提取數據特征,而CNN的計算復雜度比傳統算 法高出很多。同時隨著CNN不斷提高的精度,其網絡深度與參數的數量也在飛快地增長, 其所需要的計算資源和內存資源也在不斷增加。目前通用CPU已經無法滿足CNN的計算需 求,如今主要研究大多通過專用集成電路(ASIC),圖形處理器(GPU)或者現場可編程門 陣列(FPGA)來構建硬件加速電路,來提升計算CNN的性能。

其中 ASIC 具備高性能、低功耗等特點,但 ASIC 的設計周期長,制造成本高,而 GPU 的并行度高,計算速度快,具有深度流水線結構,非常適合加速卷積神經網絡,但與之對 應的是 GPU 有著功耗高,空間占用大等缺點,很多場合對功耗有嚴格的限制,而 GPU 難 以應用于這類需求。近些年來 FPGA 性能的不斷提升,同時 FPGA 具有流水線結構和很強 的并行處理能力,還擁有低功耗、配置方便靈活的特性,可以根據應用需要來編程定制硬 件,已成為研究實現 CNN 硬件加速的熱門平臺。

綜上所述,使用功耗低、并行度高的 FPGA 平臺加速 CNN 更容易滿足實際應用場景中 的低功耗、實時性要求。而且目標檢測算法發(fā)展迅速,針對 CNN 的硬件加速研究也大有可 為。所以本項目計劃使用 PYNQ-Z2 開發(fā)板設計一個硬件電路來加速目標檢測算法。

本項目設計的目標檢測算法硬件加速電路可以應用在智能導航、視頻監(jiān)測、手機拍照、 門禁識別等諸多方面,比如無人汽車駕駛技術,高鐵站為方便乘客進站而普遍采用的人臉 識別系統,以及警察抓捕潛逃罪犯而使用的天網系統等都可以應用本項目的設計,加速目 標檢測算法的運算速度以及降低系統的功耗。

在本次項目的設計開發(fā)過程中,我們參考 DAC 2019 低功耗目標檢測系統設計挑戰(zhàn)賽

GPU、FPGA 組雙冠軍方案,學習到了基于 SkyNet 和 iSmart2 設計一個輕量級神經網絡的 技巧,尤其是他們采用的自底向上的硬件電路設計思路給我們帶來了巨大的啟發(fā)。我們在將訓練好的神經網絡部署在硬件平臺的過程中,加深了對 HLS 的理解,開始初步掌握使用 HLS 進行并行性編程的方法。我們學習了 PYNQ 框架,在 PYNQ-Z2 上實現神經網絡加速 電路,有了軟硬件協同開發(fā)的經歷。除此之外,我們還學習了 Vitis AI,雖然在項目中并沒 有使用到 Vitis Ai,但是對它的學習擴寬的我們的視野。

第二部分 系統組成及功能說明 /System Construction & Function Description

本項目針對DAC2019 System Design Contest測試集,計劃采用PYNQ-Z2開發(fā)板加速目標 檢測網絡,綜合考慮數據訪問、存儲、并行計算等問題進行優(yōu)化處理,設計出高速高精度 且低功耗的加速方案,并完成相關仿真和FPGA平臺的驗證,實現一個可以框選出圖像中行 人或其他物體位置的硬件電路。

本項目的系統框圖如圖2-1所示,首先PS端從SD卡讀取圖片并壓縮,之后將圖片和參 數權重一起傳輸到 DRAM中,PL端再從DRAM中讀取數據并歸一化,經過卷積和池化將輸 出特征圖傳回到DRAM中,再進行下一層卷積運算;直到網絡最后一層輸出送入到邊界框 輸出模塊中選擇置信度最高的邊界框傳輸到DRAM中,供PS端讀取。

2.1 神經網絡模型的設計方案

針對 DAC-SDC 數據集并結合 SkyNet 和 iSmart2 網絡設計原理,挑選出的基本單元Bundle 由 3×3 逐通道卷積(Depthwise Convolution),1×1 逐點卷積(Pointwise Convolution)和 激活函數 ReLU6 組成。

其中 3×3 逐通道卷積和 1×1 逐點卷積的參數量和計算量遠遠少于傳統的卷積。如圖 2-2 和 2-3 所示,首先每個 3×3 逐通道卷積核與各自對應的輸入通道數據進行卷積運算,所以 輸出通道數等于輸入通道數;然后上一步運算得到的特征圖繼續(xù)進行 1×1 逐點卷積,每個 1×1 逐點卷積核對輸入的所有通道進行卷積運算,并將結果相加得到一個輸出特征圖,所以輸出通道數等于逐點卷積核的數量。

ReLU6 激活函數與傳統的 Relu 激活函數相比,當 ReLU6 函數的輸入值大于等于 6 時 輸出值恒為 6,可以使模型更快地收斂。同時網絡采用大小為 2×2,步長也為 2 的最大池化 層(Max pooling)來降低運算量并防止過擬合,特征圖每經過一次最大池化層其寬和高都減小一半。

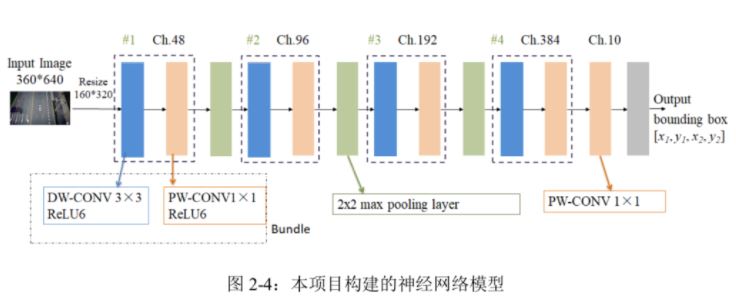

綜上所述本項目構建的神經網絡模型如圖 2-4 所示:

本項目構建的網絡模型主要由四個 Bundle 基本單元和三個 Max pooling 層組成,其中每個 Bundle 由 3×3 逐通道卷積,ReLU6 激活函數,1×1 逐點卷積,ReLU6 激活函數依次排 列組成。通過每個 Bundle 中的 1×1 逐點卷積實現輸出特征圖通道數翻倍,通過 Bundle 其 后緊接著的 Max pooling 層實現輸出特征圖的尺寸減半。因為數據集內的樣本圖片分辨率均 為 3×360×640,為了降低計算量就選擇將圖片壓縮到 3×160×320,這個尺寸既可以盡量保 留圖片的信息以防止目標檢測準確率下降,又可以在神經網絡運算過程中很方便地通過 Max pooling 進行降采樣。經過三層 Max pooling 后特征圖的大小為 20×40,再經過最后一 層 1×1 逐點卷積后輸出為 10×20×40,是將輸入圖片分為 20×40 個分塊,又因為輸出通道數 為 10,即每個分塊將會得到兩個邊界框和對應的置信度,本項目設計的算法會遍歷所有分 塊的邊界框,選擇置信度最大的邊界框輸出。

2.2 FPGA加速電路設計方案

本項目設計的硬件電路主要有兩個模塊模塊:數據讀取與傳輸模塊。首先需要讀取圖片和模型參數的數據,并對輸入的圖片數據進行歸一化處理,然后送入到卷積運算模塊中 進行計算,接著將計算結果送入到邊界框輸出模塊,最后將得到的邊界框結果傳輸到DDR3內存中。

2.2.1 數據讀取與傳輸模塊

優(yōu)化設計一個高效的數據讀取與傳輸模塊是完成目標檢測任務的前提。首先考慮到FPGA 自身 BRAM 資源有限,所以在數據讀取模塊中會將每一層的特征圖切分成多個數據 塊逐次送入到運算模塊中進行運算。每個數據塊的大小為 20×40,例如將大小為 3×160×320 的輸入圖片分成 64 個 3×20×40 的數據塊。

數據讀取時每次讀取 3×3 逐通道卷積核參數的大小為 16×3×3,讀取 1×1 逐點卷積核參 數的大小則為 16×16,兩者均為 16 通道,是因為卷積運算模塊為提升運算速度采用了 16 通道并行計算的結構。數據傳輸過程中將特征圖,網絡參數通過指針連續(xù)地存儲在 DDR3 內存中,方便數據存取,提高傳輸效率。

PYNQ-Z2 的 PS 端通過 AXI4 總線與 PL 端進行通信,AXI4 總線協議具有高性能,高 頻率等優(yōu)勢。在 Vivado HLS 中編寫硬件代碼時需要將輸入圖片,模型參數和邊界框等 PS 端與 PL 端傳遞數據的接口定義為主或從接口,之后在 Vivado 中自動連線時軟件會添加 AXI Interconnect 用于管理總線,并自動為接口分配地址。

在硬件代碼編寫完成后,需要進行 C 仿真和 C 綜合等步驟,最后導出 RTL,可以在導 出的 IP 核驅動的頭文件中找到接口的地址,然后在 PS 端開發(fā)時將圖片和網絡參數數據寫 入對應地址即可,并從相應的接口地址讀取輸出數據。

2.2.2 卷積運算模塊

設計卷積運算模塊來加速卷積運算是 FPGA 加速電路的關鍵,卷積運算模塊由 3×3 逐 通道卷積運算模塊和 1×1 逐點卷積運算模塊組成。

首先為了讓設計的 3×3 逐通道卷積運算模塊能夠在不同的卷積層間復用,需要保持 3×3 逐通道卷積前后數據塊大小不變,這需要對輸入和輸出數據塊進行填充(padding)。輸入數 據塊原始大小為 20×40,本項目選擇 padding=1,則輸入數據塊大小變?yōu)?22×42,經過 3×3 逐通道卷積后高和寬分別為 20 和 40,即輸出數據塊大小依舊為 20×40。如果接下來還需要 進行 3×3 逐通道卷積,則再對輸出進行填充使輸出數據塊大小也為 22×42,以保持運算過 程中數據塊大小不變,這樣就能很方便地復用 3×3 逐通道卷積運算模塊來節(jié)約硬件資源。

因為卷積運算過程中特征圖的通道數逐步變?yōu)?48,96,192,384,均為 16 的倍數, 所以綜合考慮 FPGA 的并行性優(yōu)點和 PYNQ-Z2 自身資源情況,設計卷積運算模塊為 16 個 通道并行計算來提升運算速度。16 通道 3×3 逐通道卷積的輸入數據塊為 16×22×42,卷積核 為 16×3×3,輸出數據塊經填充后也為 16×22×42。

因為 3×3 逐通道卷積由乘法和加法運算構成,所以其運算模塊需要乘法器,加法器和 寄存器。針對 3×3 逐通道卷積運算模塊,以第一個通道為例,首先把偏置??11 放入寄存器 中,接著在第一個時鐘周期內,送入數據塊的輸入??11和卷積核參數??11并相乘,將結果與寄 存器內的??11相加并送入寄存器中。第二個時鐘周期內送入??12和參數??12重復上述操作,經 過九個時鐘周期后輸出??11,所以需要 9 個時鐘周期來完成一次 3×3 逐通道卷積,期間共進行了 9 次相乘并累加操作。則 16 通道并行計算共需要 16 個乘法器和 16 個加法器,即需要 16 個 DSP 資源。

同理可以設計 16 通道 1×1 逐點卷積運算模塊,以第一個通道為例, 1×1 逐點卷積運 算時可以不需要計算 padding 部分,直接從原始輸入數據塊開始計算,輸入數據塊第一個 通道的??11與卷積核參數??11相乘并將結果保存在寄存器mul1中,則 16 個通道得到 mul1~mul16共 16 個乘積值,接著乘積值兩兩相加得到add1~add8共 8 個累加值,再將得到 的結果不斷兩兩相加直到僅有一個累加值add15,最后再加上偏置得到輸出O11,所以完成 一次 16 通道 1×1 逐點卷積共需要 16 次乘法和加法運算。

本項目設計的硬件電路針對 1×1 逐點卷積運算模塊提供了最大 16 通道并行的計算方 式。考慮到 PYNQ-Z2 的 DSP 資源共 220 個,且 3×3 逐通道卷積運算模塊和邊界框輸出模 塊均占用 DSP 資源,所以最多可以例化 9 個 16 通道 1×1 逐點卷積運算模塊,需要乘法器 和加法器的數量均為 144 個,即需要 144 個 DSP 資源。

2.3 PS 端編程開發(fā)

本項目使用的 PYNQ-Z2 的 PS 端安裝了 Linux 操作系統,配置好了 Python 開發(fā)環(huán)境,

并預裝了 Numpy 等常用庫和專用于 PYNQ 架構的 PYNQ 開發(fā)庫。本項目通過 Micro SD 卡 啟動 PYNQ-Z2,借助網線將路由器與 PYNQ-Z2 相連,登陸路由器管理界面可以查看分配 給 PYNQ-Z2 的 IP 地址,讓電腦也連接路由器,使兩者的網絡段相同,就可以通過瀏覽器 登陸這個 IP 地址來訪問 PS 端自帶的 Jupyter Notebook 并進行 Python 編程開發(fā)。

PS 端首先通過 PYNQ 庫中的 Xlnk 類來為輸入圖片,卷積核參數,偏置,池化層輸出 和預測框等分配連續(xù)內存,接著使用圖像庫 PIL 中的 Image 類從 Micro SD 卡中讀取 3×360×640 大小的輸入圖片,并將圖片壓縮為 3×160×320,再將壓縮后的圖片轉化為 numpy 數組后傳入 DDR3 內存中。之前訓練好的兩種卷積核參數和偏置數據都保存在了二進制文件中,也需要從 SD 卡中分別讀取這些數據并按照卷積運算模塊數據塊的大小和運算順序 重新排列后送入 DDR3 內存中。

數據傳輸完成后 PS 端通過 PYNQ 庫中的 Overlay 類燒寫比特流文件和 tcl 文件來配置 PYNQ-Z2,然后當輸入圖片和網絡參數寫入到對應地址時硬件電路就開始工作,全部運算 完成后 PS 端從相應的地址讀取邊界框的值并在圖片上畫出邊界框。

第三部分 完成情況及性能參數/Final Design & Performance Parameters

3.1 實驗設計

3.1.1 神經網絡模型訓練

為了提升神經網絡的訓練效率,本次實驗把本地編寫好的 PyTorch 代碼和數據集一起 傳輸到云服務器中重復進行訓練直到滿足精度要求,接著在測試集上測試網絡的識別精度, 如果能夠滿足要求就將訓練好的網絡參數保存下來,并將格式轉化為二進制文件。

3.1.2 硬件代碼仿真與綜合

本項目首先隨機選出幾張數據集中的圖片通過編程轉換成二進制 bin 文件,進行 C 仿 真時 Test bench 先是讀取二進制圖片文件和訓練好的網絡模型參數,然后送入編寫好的 Test bench 網絡模型中計算并輸出結果,為了對比 Test bench 和硬件代碼的輸出結果,還需要將 網絡參數重排序后和圖片一起送入硬件代碼中計算并輸出結果,同時將重新排序后的網絡 參數保存成新的二進制文件供給之后在 PS 端調用。對比 Test bench 和硬件代碼的輸出來判 斷硬件代碼邏輯功能的正確性。

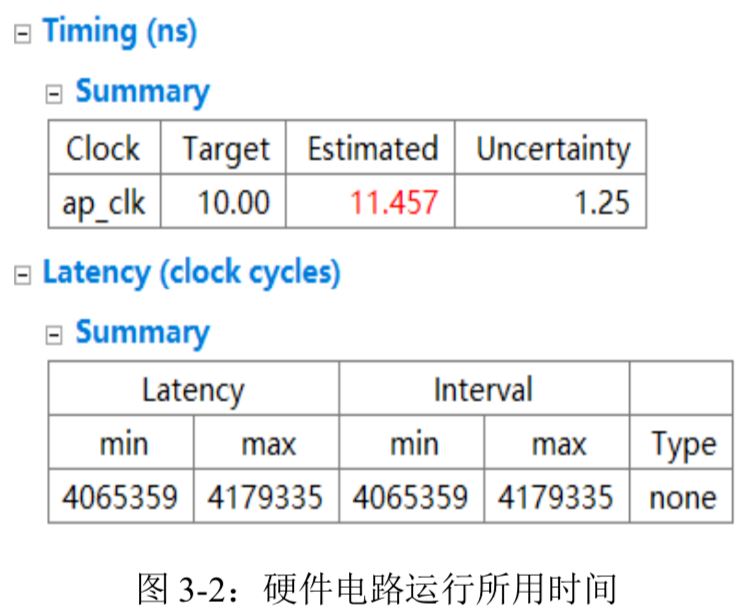

實驗 C 仿真結果的報告如圖 3-1 所示,第 6 行顯示本次輸入圖片的編號為 0,第 9 行顯示輸入圖片第 10 行第 21 列這個數據塊的第二個邊界框的置信度最大,第 14 行顯示其值 近似為 0.897,第 10 至 13 行顯示了 Test bench 輸出邊界框歸一化后的坐標和寬高,將這四 個值與數據塊的寬高 40 和 20 對應相乘后得 21.24,10.34,3.99,6.04,與第 20 行顯示的 硬件代碼輸出邊界框的預測結果十分相近,同時硬件代碼輸出邊界框的置信度近似為 0.891, 與 Test bench 的結果也十分接近。可以看到 Test bench 和硬件代碼兩者輸出的邊界框和置信 度都非常相近,且經過與真實輸入圖片中目標的位置對比發(fā)現三者的結果基本一致,可以認為硬件代碼的邏輯功能正確,能夠完成目標檢測任務。C 仿真通過后接著進行 C 綜合,C 綜合可以根據實驗一開始選擇的 PYNQ-Z2 的芯片型號,編寫的硬件代碼和 directives 指令自動為硬件電路分配資源,并生成 Verilog 代碼。如 圖 3-2 所示,C 綜合結果的報告給出了硬件電路運行所用的時間。

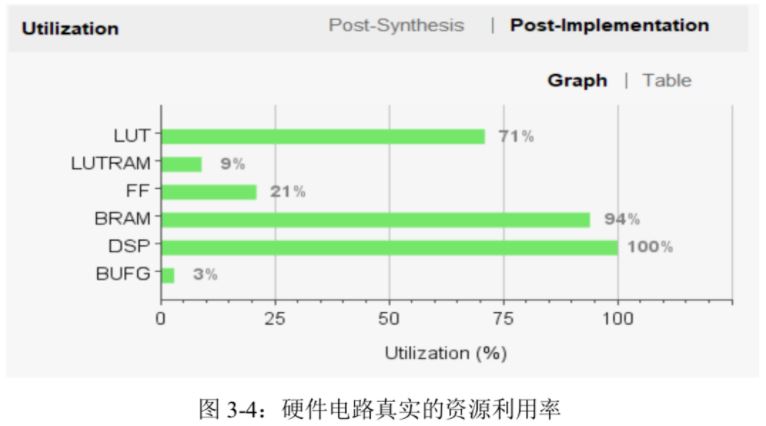

表 3-1 則給出了整個硬件電路所需要的 BRAM,DSP 等資源情況,可以根據 C 綜合報告修改各個模塊的硬件代碼或者 directives 指令來調整資源利用率,直到滿足要求。可以看到本項目設計的硬件代碼已經幾乎利用了全部 DSP 和 BRAM 資源。又因為 C 綜合時往往對所需 LUT 的資源預測值遠超實際值,所以報告顯示 LUT 資源超出總額,更加真實的資源利用情況需要在 Vivado 中生成比特流文件后的報告中查看。

硬件代碼 C 綜合通過之后就可以開始進行 C/RTL 協同仿真,協同仿真主要是從時序角 度檢測硬件代碼是否正確,仿真結果會得到一個波形文件,可通過觀察波形來判斷硬件代 碼的執(zhí)行時序是否正確。通過觀察仿真波形可以確認本項目設計的硬件代碼時序正確,仿真可以通過。

3.1.3 生成比特流文件

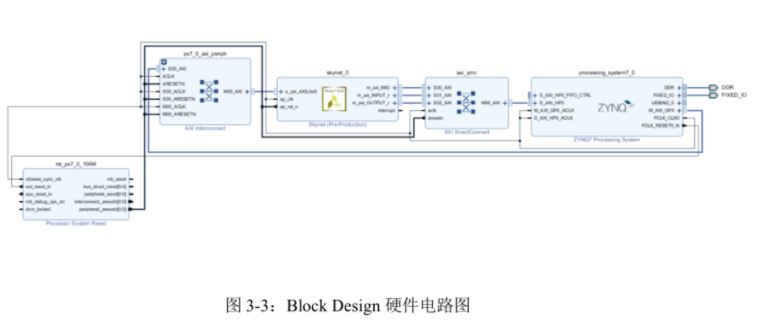

硬件代碼的仿真與綜合都通過之后就可以將硬件代碼封裝成 IP 導出,打開 Vivado 并選擇 PYNQ-Z2 開發(fā)板新建工程,調用封裝好的 IP 和開發(fā)板上的 RAM 芯片 ZYNQ7000。

因為 ZYNQ7000 的從 AXI_HP 接口默認不使用,所以需要手動配置好這個端口。PS 端還需 要引出一個時鐘信號提供給 PL 端,其他參數在添加 PYNQ-Z2 開發(fā)板時已經基本設置妥當, 通過自動連線生成的電路如圖 3-3 所示。

電路連接完成后即可開始生成比特流 bit 文件,接著導出 Block Design 來生成 tcl 文件,之后的 PS 端調試需要調用這兩個文件來配置 PYNQ-Z2。圖 3-4 是生成比特流后的報告, 可以得到比 C 綜合報告更為真實的資源利用情況,此時 LUT 資源利用率從 157%降至 71%, 所以 PYNQ-Z2 能夠滿足本論文設計的硬件電路的要求。

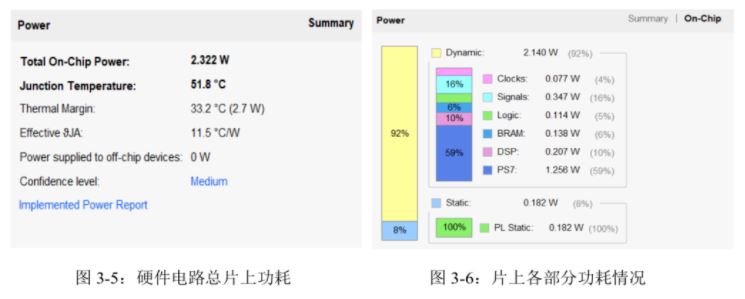

圖 3-5 顯示硬件電路的總片上功耗為 2.322W,功耗表現滿足預設目標。圖 3-6 則具體顯示了片上各部分的功耗情況,其中總功耗中動態(tài)功耗占了絕大部分,而 RAM 芯片功耗 則占據了 60%左右的動態(tài)功耗。

3.1.4 PS 端開發(fā)驗證

在生成比特流文件和導出 Block Design 之后,即可開始本次實驗的最后一步,在 PS 端 編程來驗證硬件代碼在 PYNQ-Z2 上能否完成目標檢測任務。首先用網線將 PYNQ-Z2 與路 由器相連并通過 USB 線供電,這樣 PYNQ-Z2 能夠聯網,可以隨時從網上下載各種開發(fā)包 和環(huán)境。由于 PYNQ-Z2 可以通過 Samba 服務來共享文件夾,所以可以很方便地將比特流 文件,tcl 文件,輸入圖片和重新排序的網絡參數二進制文件直接傳到 SD 卡上的 Jupyter Notebook 文件夾內。

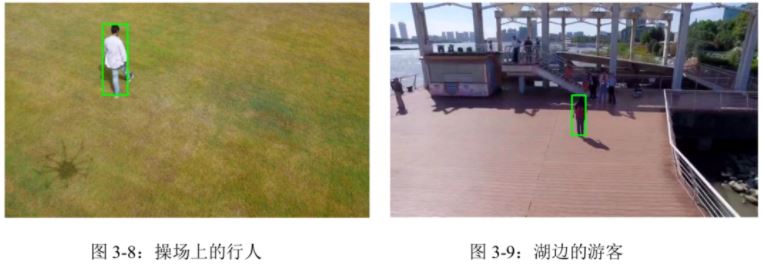

實驗可以準確地識別出圖 3-8 中的行人和圖 3-9 中的游客,證明本項目設計的硬件電路能夠完成目標檢測任務。

3.2 實現功能與性能指標

本項目 PYNQ-Z2 開發(fā)板加速目標檢測網絡,可以在輸入圖片上標出邊界框。又因為 PYNQ-Z2 的資源有限,本項目設計的硬件電路運算速度還不到 200MFLOPS。但是該電路 可以根據所選開發(fā)板的資源情況來例化適合的 1×1 逐點卷積運算模塊數量,以此來提升運 算速度。

從生成比特流的報告中可知硬件電路的總片上功耗為 2.322W,遠小于預設的功耗 8W, 所以本論文優(yōu)化設計的 FPGA 加速電路在功耗方面滿足預期目標。

接著需要考察另一個指標 IoU,也稱為交并比,需要通過“預估的邊界框”與“實際 的邊界框”之間交集和并集的比值來計算。又因其要求嚴格,所以一般認為目標檢測結果IoU 大于 0.5 即可滿足精度要求。本次實驗利用 DAC-SDC 訓練集來訓練網絡參數,接著用 準備的測試集圖片對訓練好的網絡進行測試,得到 IoU 約等于 0.573,所以本項目構建的網 絡模型的準確率也滿足預設目標。

第四部分 總結

項目總結

本項目依據 SkyNet 和 iSmart 網絡的設計原理,合理地構建了一個主要由 3×3 逐通道卷積和 1×1 逐點卷積組成的輕量級卷積神經網絡用來完成目標檢測任務,并專門為這兩類卷積優(yōu)化設計了 FPGA 硬件加速電路模塊來提升卷積運算速度,同時通過對卷積運算模塊 的充分復用較好地節(jié)約了開發(fā)板資源。

本項目在 PYNQ-Z2 開發(fā)板上設計的硬件加速電路可以很好地完成目標檢測任務,輸出 的邊界框能夠準確地框選出圖片中的行人或者物體。硬件電路總片上功耗只有 2.322W,而 IoU 可以達到 0.573,基本滿足了設計目標。

更多信息可以來這里獲取==>>電子技術應用-AET<<