本文來源:半導體行業(yè)觀察

原文鏈接:https://mp.weixin.qq.com/s/yrxZiPGHVuMSLl0Jzk1mSA

在芯片制造領(lǐng)域,3nm方興未艾,圍繞著2nm的競爭已經(jīng)全面打響。

根據(jù)臺灣經(jīng)濟日報日前的新聞報道,臺積電已經(jīng)在本月初已經(jīng)開始了 2 納米工藝的預(yù)生產(chǎn),而英偉達和蘋果將有望成為晶圓代工龍頭的首批客戶,這將給三星等競爭對手帶來巨大壓力。在回應(yīng)該報道時,臺積電沒有評論具體細節(jié),但表示2nm技術(shù)的開發(fā)進展順利,目標是在2025年實現(xiàn)量產(chǎn)。

英特爾中國區(qū)總裁兼董事長王銳在今年三月的一次活動中表示,公司已完成intel 18A(1.8nm)和intel 20A(2nm) 制造工藝的開發(fā)。其中,intel 20A計劃于 2024 年上半年投入使用,進展良好的intel 18A制造技術(shù)也將提前到2024年下半年進入大批量制造(HVM)。

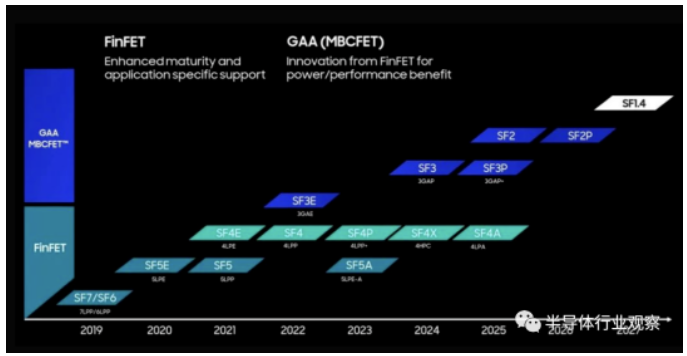

與此同時,晶圓代工老二三星在今日舉辦的代工論壇論壇上也重申了公司將在2025年實現(xiàn)2nm生產(chǎn)。再加上日本新成立的 Rapidus也想在2025年量產(chǎn)2nm。一場在2025年將進入白熱化的戰(zhàn)爭已經(jīng)全面打響。

三星密謀已久

這不是三星首次披露其2nm的計劃,其實針對這個被廣泛看好的“大節(jié)點”,這家韓國巨頭密謀已久,他們在這次代工論壇上也帶來了更多的消息。

據(jù)semiwiki報道,與英特爾一樣,三星自己的芯片也是自己的代工客戶,因此他們在2nm上首先生產(chǎn)的是內(nèi)部產(chǎn)品,而不是外部代工客戶。這當然是 IDM 代工廠的優(yōu)勢,可以結(jié)合工藝技術(shù)開發(fā)自己的芯片。三星擁有開發(fā)領(lǐng)先內(nèi)存的額外優(yōu)勢。

報道指出,三星將于 2025 年開始量產(chǎn)用于移動應(yīng)用的 2nm 工藝,然后于 2026 年擴展到具有背面供電的 HPC,并于 2027 年擴展到汽車領(lǐng)域。與 3nm 工藝 (SF3) 相比,三星的 2nm (SF2) 工藝已顯示出性能提升 12%,功率效率提高提升 25%,面積減少 5%。

按照三星的規(guī)劃,其GAA MBCFET無疑是2nm工藝的最大競爭優(yōu)勢所在,在上個月的時候,他們就公布了公司在3nm GAA MBCFET技術(shù)的最新進展,這將給他們的2nm提供參考。

三星表示,與 FinFET 相比,MBCFET 提供了卓越的設(shè)計靈活性。晶體管被設(shè)計成有不同量的電流流過它們。在使用許多晶體管的半導體中,必須調(diào)節(jié)電流量,以便在所需的時序和控制邏輯下打開和關(guān)閉晶體管,這需要增加或減少溝道的寬度。

而在傳統(tǒng)的FinFET結(jié)構(gòu)中,柵極所包裹的鰭片(Fin)的高度是不可調(diào)節(jié)的,因此為了增加整體溝道寬度,需要水平地增加鰭片的數(shù)量。但這種方法只能調(diào)節(jié)不連續(xù)的溝道寬度,因為當柵包圍文件的溝道寬度為α時,也只能減小或增大α的倍數(shù)。這是一個嚴重的限制。

另一方面,MBCFET 彼此堆疊在一起,鰭片側(cè)向放置,納米片的寬度可以調(diào)整,以提供比 FinFET 更多的溝道寬度選項,這是一個對整個設(shè)計有用的功能,這在模擬 SRAM 中具有顯著的優(yōu)勢設(shè)計。

”MBCFET 具有這些優(yōu)勢,因為它們的設(shè)計允許獨立微調(diào)晶體管的溝道寬度,以便在 P 型金屬氧化物半導體晶體管 (PMOS) 和 N 型金屬氧化物半導體晶體管(NMOS)之間找到最佳平衡”,三星強調(diào)。

而在MBCFET 通過調(diào)整納米片寬度,為 SRAM 單元設(shè)計提供了更大的靈活性。左上圖顯示了具有六個晶體管的基本 SRAM 位單元。中間圖像顯示了該位單元的圖形設(shè)計系統(tǒng) (GDS) 視圖。

在圖(a)中,在GAA結(jié)構(gòu)中,NMOS下拉(PD)和傳輸門(PG)具有相同的溝道寬度,而PMOS上拉(PU)具有較小的溝道寬度。(WPD = WPG > WPU ) 在這種情況下,從右圖可以看出,MBCFET 可以比 FinFET 獲得更好的裕度。

在圖(b)中,當PD和PG之間的溝道寬度變化時,它們是NMOS(W PD > WPG > WPU ),裕度高于(a)。通過根據(jù)晶體管的作用和特性調(diào)整溝道寬度,實現(xiàn)最佳平衡,并確保裕度。由于 GAA SRAM 位單元比 FinFET 需要更少的功率,并且由于每個晶體管的 GAA 寬度可以獨立調(diào)整,因此 PPA 和 SRAM 之間的平衡得到改善,從而大大提高了 SRAM 的設(shè)計穩(wěn)定性。

除了晶體管外,背面供電技術(shù)也是三星2nm的一個殺手锏。

三星研究員Park Byung-jae表示,在代工市場,技術(shù)正在從高 k 金屬柵極平面 FET 發(fā)展到 FinFET、MBCFET,以及現(xiàn)在的 BSPDN。

據(jù)介紹,BSPDN與前端供電網(wǎng)絡(luò)不同,它主要使用后端;正面將具有邏輯功能,而背面將用于供電或信號路由。據(jù)他們在一篇論文中披露,將供電網(wǎng)絡(luò)等功能移至芯片背面,以解決使用2nm工藝造成的布線擁塞問題。據(jù)稱,與 FSPDN 相比,BSPDN 的性能提高了 44%,能效提高了 30%。

在公布2nm規(guī)劃的同時,三星強調(diào),公司的1.4nm工藝預(yù)計于 2027 年實現(xiàn)量產(chǎn)。與此同時,三星代工廠繼續(xù)致力于投資和建設(shè)產(chǎn)能,在韓國平澤和德克薩斯州泰勒增設(shè)新生產(chǎn)線。目前的擴張計劃將使公司的潔凈室產(chǎn)能到 2027 年比 2021 年增加 7.3 倍。

臺積電不甘人后

在大家都在圍繞著2nm傾囊而出的時候,臺積電也不甘人后。

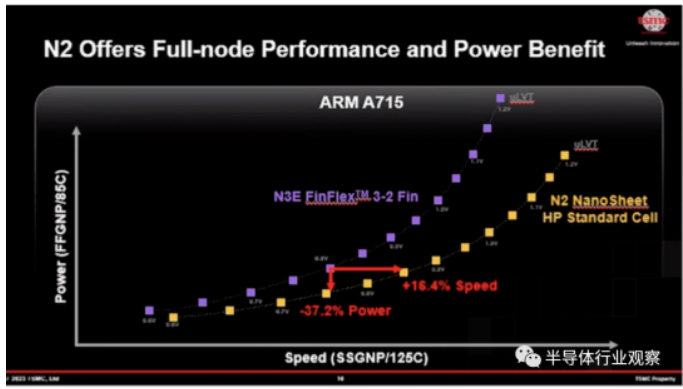

臺積電在去年的代工技術(shù)研討會上就披露了其下一代 N2 2nm 節(jié)點的早期細節(jié),包括將改用納米片晶體管架構(gòu),其中幾個堆疊的硅層完全被晶體管柵極材料包圍,而不是當前的 FinFET 設(shè)計,與當前 FinFET 晶體管相比,GAAFET 的優(yōu)勢包括降低漏電流(因為柵極位于溝道的所有四個側(cè)面),以及調(diào)整溝道寬度以獲得更高性能或更低功耗的能力。

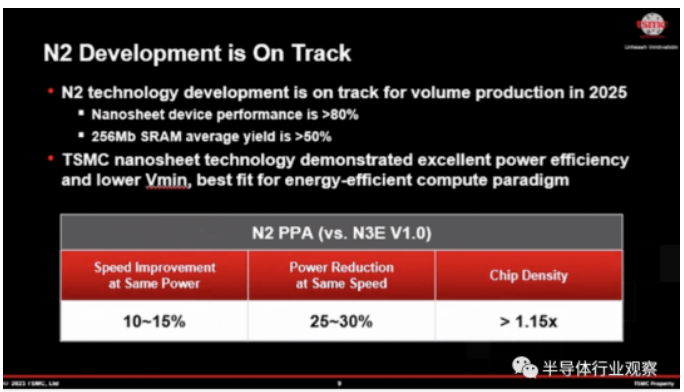

早前舉辦的研討會上,臺積電進一步公布了2nm的更多消息。

他們表示,公司在 N2 硅的良率和性能方面都取得了“扎實的進展”,預(yù)計其密度將比今年進入量產(chǎn)的增強型 N3E 節(jié)點提高 1.15 倍以上。預(yù)計 2025 年投入生產(chǎn)時,在相同功率下,它的速度將比 N3E 提高 15%,或者在相同速度下,功耗最多可降低 30%。

臺積電還表示,在進入 HVM 兩年前,其 Nanosheet GAA 晶體管性能已達到目標規(guī)格的 80% 以上,256Mb SRAM 測試 IC 的平均良率超過 50%。臺積電更是在一份聲明中寫道:“臺積電納米片技術(shù)展示了出色的功效和較低的 Vmin,最適合節(jié)能計算范例。”

和三星一樣,臺積電也有一個N2P節(jié)點,這將在2026年某個日子推出。同時,在這個工藝上,臺積電也將引入背面供電技術(shù)。目前,臺積電尚未透露關(guān)于背面供電的更多信息,有關(guān) N2P 相對于 N2 的性能、功耗和面積 (PPA) 優(yōu)勢的任何硬數(shù)據(jù),臺積電也還沒公布。但根據(jù)anandtech從行業(yè)消息來源了解到的情況,僅背面電源供電就可以帶來個位數(shù)的功率改進和兩位數(shù)的晶體管密度改進。

臺積電還表示,N2P 有望在 2026 年投入生產(chǎn),因此我們可以推測第一批基于 N2P 的芯片將于 2027 年上市。

除了可能成為臺積電 2nm 代工藝主力的 N2P 之外,臺積電還在準備 N2X。這將是專為高性能計算 (HPC) 應(yīng)用(例如需要更高電壓和時鐘的高端 CPU)量身定制的制造工藝。代工廠并未概述該節(jié)點與 N2、N2P 和 N3X 相比的具體優(yōu)勢,但與所有性能增強節(jié)點一樣,實際優(yōu)勢預(yù)計將在很大程度上取決于設(shè)計技術(shù)協(xié)同優(yōu)化 (DTCO) 的實施程度。

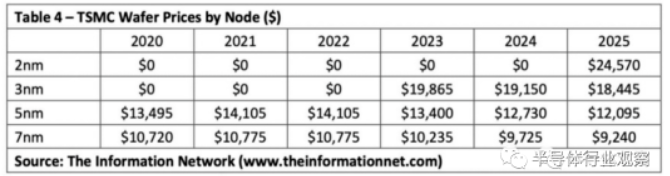

對于臺積電2nm,近來還有消息透露,他們這個節(jié)點的單片晶圓定價逼近25000美元,相比屆時的3 納米晶圓代工報價的18,445 美元大幅上漲。這對于Fabless來說無疑是另一個挑戰(zhàn)。回顧過去,臺積電加工每? 90 納米制程晶圓所消耗的成本為411 美元,加工每? 5 納米制程晶圓所消耗的成本已經(jīng)上升到了4,235 美元,相較加工每? 7 納米制程晶圓所消耗的成本2,330 美元,也增加了81.8%。

由此看來,臺積電晶圓代工報價的上漲幅度,其與加工成本的上漲幅度是相接近的。

英特爾寄以厚望

在制造工藝上落后許久的英特爾在最近對其晶圓代工業(yè)務(wù)進行了調(diào)整,向著下一步拆分做好準備。與此同時,他們還對2nm(Intel 20A)工藝寄以厚望,他們希望在這個工藝上追平三星和臺積電等競爭對手。英特爾聲稱,如果正確執(zhí)行 IFS 和 IDM 2.0 路線圖,Intel 18A 代工節(jié)點應(yīng)該在技術(shù)上和上市時間上擊敗臺積電 2 納米級節(jié)點。

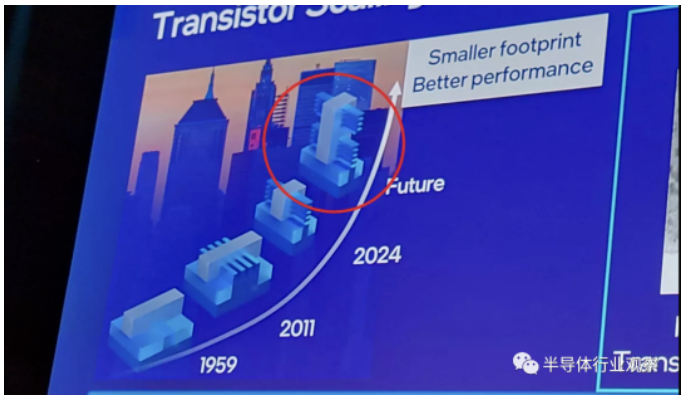

從技術(shù)上來說,Intel 20A及intel 18A不僅是他們首批進入埃米節(jié)點的工藝,在其上還會首發(fā)兩大突破性技術(shù),也就是RibbonFET和PowerVia,其中RibbonFET是Intel對Gate All Around晶體管的實現(xiàn),它將成為公司自2011年率先推出FinFET以來的首個全新晶體管架構(gòu)。

英特爾過去多年來一直在技術(shù)半導體會議上討論 GAAFET,在 2020 年 6 月的國際 VLSI 會議上,時任首席技術(shù)官 Mike Mayberry 博士展示了轉(zhuǎn)向 GAA 設(shè)計后增強靜電的圖表。當時我們詢問英特爾批量實施 GAA 的時間表,并被告知預(yù)計將在“5 年內(nèi)”實現(xiàn)。目前,英特爾的 RibbonFET 將采用 20A 工藝,根據(jù)上述路線圖,可能會在 2024 年底實現(xiàn)產(chǎn)品化。

anandtech在報道中指出,在英特爾將在RibbonFET中確實將使用 4 堆棧實施,因為添加的堆棧越多,制造所需的工藝節(jié)點步驟就越多,引用英特爾的 Kelleher 博士的話:“刪除堆棧比添加堆棧更容易”。對于任何給定的進程或功能來說,確切的堆棧數(shù)量仍然是一個活躍的研究領(lǐng)域,但英特爾似乎更熱衷于四個。

值得一提的是,在早前舉辦的 ITF World上,英特爾還展示了全新堆疊式 CFET 晶體管設(shè)計——一個被業(yè)界看好的下一代 GAA設(shè)計。

從英特爾提供的圖像我們很好地觀察到——這種設(shè)計允許該公司堆疊八個納米片,使納米片的數(shù)量增加了一倍。四個與RibbonFET一起使用,從而增加晶體管密度。我們還在上面的相冊中提供了其他三種類型的英特爾晶體管的圖像 - Planar FET、FinFET 和 RibbonFET。

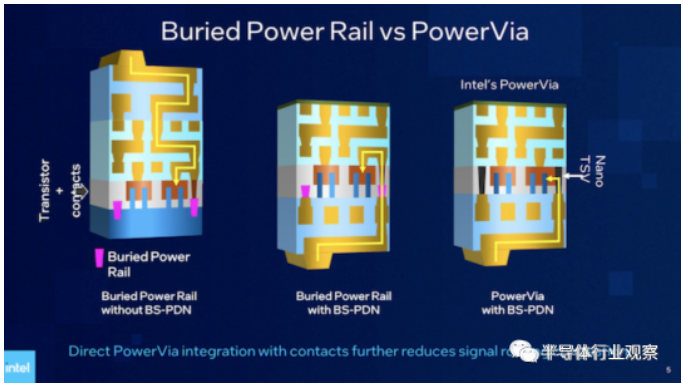

如上所說,背面供電,則是英特爾另一個在Intel 20A工藝上的另一重點技術(shù)。他們也在日前舉辦的VLSI大會上更新了這個技術(shù)的進展。

按照英特爾所說,遷移到 BS-PDN 最終有幾個好處。首先,這對簡化芯片的構(gòu)造具有重要影響。我們稍后會講述英特爾的具體聲明和發(fā)現(xiàn),但這里需要特別注意的是,它允許英特爾放寬其 M0 金屬層的密度。Intel 4 + PowerVia 的測試節(jié)點允許 36 nm 間距,而不是在 Intel 4 上要求 30 nm 間距。這直接簡化了整個芯片最復(fù)雜和昂貴的處理步驟,將其回滾到更接近intel 7 工藝的尺寸。

BS-PDN 也準備好為芯片提供一些適度的性能改進。通過更直接的方式縮短晶體管的功率傳輸路徑有助于抵消 IR Droop 效應(yīng),從而更好地向晶體管層傳輸功率。將所有這些電源線從信號層中取出也可以提高它們的性能,從而消除電源干擾并為芯片設(shè)計人員提供更多空間來優(yōu)化他們的設(shè)計。

在英特爾的方案中,首先,使用載體晶圓(carrier wafer )作為其構(gòu)建過程的一部分,以提供芯片剛性。英特爾實施 BS-PDN 的另一個值得注意的細節(jié)是使用 TSV 進行電源布線。在 PowerVia 中,芯片的晶體管層中有納米級 TSV(恰如其分地命名為 Nano TSV)。這與行業(yè)先驅(qū) IMEC 一直在研究其 BS-PDN 的埋入式電源軌形成對比。

總而言之,雖然電源軌仍然需要向上和越過晶體管層來輸送電力,但使用 TSV 可以讓電力更直接地輸送到晶體管層。對于英特爾來說,這是他們熱衷于利用的一項技術(shù)優(yōu)勢,因為它避免了必須設(shè)計和內(nèi)置埋入式電源軌所需的路由。

關(guān)于英特爾的背面供電,我們可以參考文章《搶進背面供電,芯片制造新王牌》。

日本Rapidus成為x因素

在大家都以為先進制造格局已定的時候,日本Rapidus橫空出世。

由日本八家大企業(yè)支持成立、并獲政府注資的半導體公司Rapidus正在興建的首座晶圓廠就直攻2納米制程,背負著復(fù)興日本晶圓制造的重責大任。Rapidus會長東哲郎上月接受受訪時表示,有信心讓公司在短時間內(nèi)就追上兩大晶圓大工業(yè)者臺積電與三星電子。

東哲郎說:“領(lǐng)先他人且獨特,是賺取大量獲利的唯一地位;如果你做別人已經(jīng)在做的,你會讓自己變得廉價。”

東哲郎說:“我對2納米與之后的1.4納米相當有信心,不過1納米會是一大挑戰(zhàn)。」「我們與材料和制造設(shè)備制造商密切合作,這些業(yè)者已與包括臺積電在內(nèi)的市場領(lǐng)導者合作先進技術(shù)。我們的全球伙伴也承諾將全力支持提供技術(shù)和教育。”

Rapidus目前已與IBM、比利時微電子研究中心IMEC結(jié)盟,而且也獲得包括豐田、Sony和軟銀等日本大企業(yè)的支持,這讓他們的2nm給市場提供新變數(shù)。

更多精彩內(nèi)容歡迎點擊==>>電子技術(shù)應(yīng)用-AET<<