使用半大馬士革工藝流程研究后段器件集成的工藝

2023-10-24

作者:半導(dǎo)體工藝與整合 (SPI) 資深工程師 Assawer Soussou 博士

來源:泛林集團(tuán)

介紹

隨著技術(shù)推進(jìn)到1.5nm及更先進(jìn)節(jié)點(diǎn),后段器件集成將會遇到新的難題,比如需要降低金屬間距和支持新的工藝流程。為了強(qiáng)化電阻電容性能、減小邊緣定位誤差,并實現(xiàn)具有挑戰(zhàn)性的制造工藝,需要進(jìn)行工藝調(diào)整。為應(yīng)對這些挑戰(zhàn),我們嘗試在1.5nm節(jié)點(diǎn)后段自對準(zhǔn)圖形化中使用半大馬士革方法。我們在imec生產(chǎn)了一組新的后段器件集成掩膜版,以對單大馬士革和雙大馬士革進(jìn)行電性評估。新掩膜版的金屬間距分別為14nm、16nm、18nm、20nm和22nm,前兩類是1.5nm節(jié)點(diǎn)后段的最小目標(biāo)金屬間距,后三類用于工藝窗口評估。

SEMulator3D?虛擬制造平臺可以展示下一代半大馬士革工藝流程,并使用新掩膜版研究后段器件集成的工藝假設(shè)和挑戰(zhàn)。此外,我們還使用新掩膜版模擬和測試了用于提升電阻電容性能和改進(jìn)制造的額外工藝。

在自對準(zhǔn)圖形化中使用半大馬士革方法

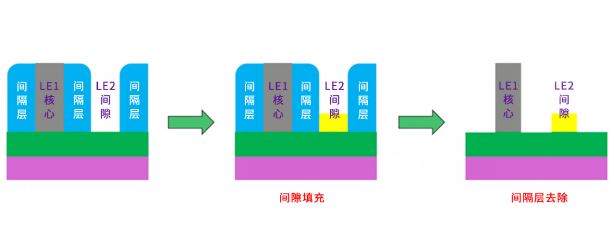

使用間隙填充和間隔層去除方案,我們提出在自對準(zhǔn)圖形化中使用半大馬士革方法。

間隔層去除方案需要選擇性刻蝕工藝。區(qū)域選擇性沉積 (ASD) 是填充LE2間隙的最佳沉積選擇。圖1 (a) 展示間隙填充工藝的剖面圖,以及間隔層和LE1核心的位置。通過使用SEMulator3D軟件,我們可以更好地研究間隙填充方案和間隔層去除方案會面臨的挑戰(zhàn)。

圖1:1.5nm節(jié)點(diǎn)圖形化工藝的間隙填充和間隔層去除方案

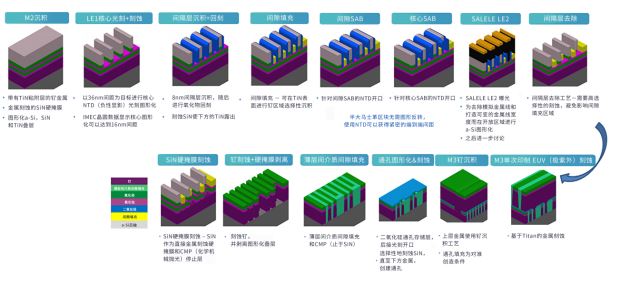

半大馬士革工藝流程

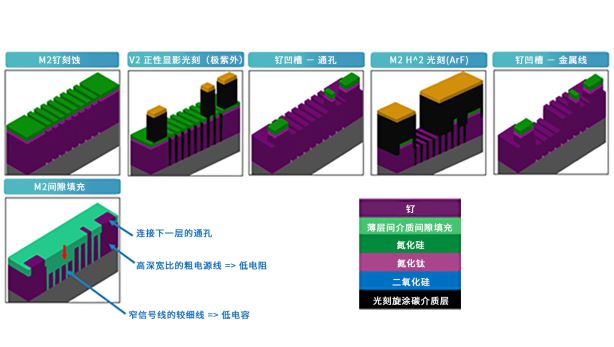

我們還使用SEMulator3D虛擬制造對半大馬士革工藝流程進(jìn)行了模擬。圖2展示模擬出的工藝流程。使用SALELE(自對準(zhǔn)光刻-刻蝕-光刻-刻蝕)方法對金屬2進(jìn)行了圖形化,并使用極紫外光刻將其連接到金屬3。之后,使用模擬的工藝流程對金屬2圖形化和金屬2與金屬3的連接進(jìn)行敏感性分析。

圖2:使用新掩膜版進(jìn)行后段器件集成的半大馬士革工藝流程

工藝助推器

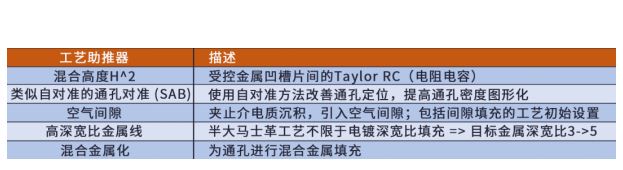

圖3展示新掩膜版的工藝助推器。我們也使用SEMulator3D來模擬和分析這些掩膜版助推器的可行性和性能。

圖3:掩膜版的1.5nm節(jié)點(diǎn)工藝助推器

混合高度

通過定制金屬線的高度,可以完全優(yōu)化電阻電容性能(如圖4),而金屬線高度的靈活性可以通過刻蝕金屬線實現(xiàn)。高金屬線電阻低、電容高,因此可能適用于電源線和長信號線;短金屬線電阻高、電容低,因此最有可能適用于信號線。我們使用SEMulator3D對這一概念進(jìn)行了初步分析。

圖4:為優(yōu)化電阻電容產(chǎn)品性能進(jìn)行的混合高度定制

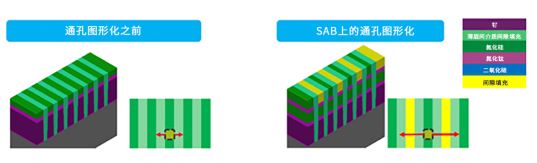

類似自對準(zhǔn)的通孔對準(zhǔn)(SAB)

自對準(zhǔn)圖形化技術(shù)最早被用于14nm節(jié)點(diǎn)的互連技術(shù)。為了生成有效器件,需要切斷由這一技術(shù)產(chǎn)生的平行金屬線。這種切斷掩膜的邊緣定位誤差很有挑戰(zhàn)性,因此在10nm和7nm節(jié)點(diǎn)開發(fā)了自對準(zhǔn)區(qū)塊技術(shù),將套刻允許誤差擴(kuò)大到?間距。邊緣定位誤差在1.5nm技術(shù)節(jié)點(diǎn)會更具挑戰(zhàn)性,我們預(yù)計這一自對準(zhǔn)技術(shù)需要擴(kuò)展至通孔層。此時,我們再次使用SEMulator3D研究1.5nm節(jié)點(diǎn)通孔自對準(zhǔn)的不同選擇(如圖5)。

圖5:使用半大馬士革自對準(zhǔn)通孔以改善通孔套刻精度

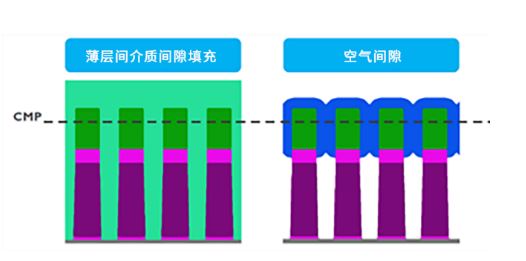

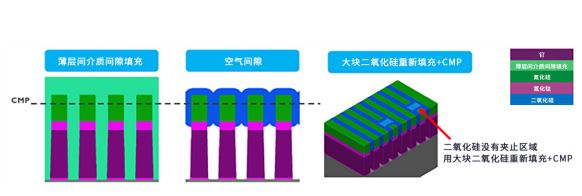

空氣間隙

為進(jìn)行大馬士革工藝引入了空氣間隙,但還需要額外的刻蝕步驟來去除薄層間介質(zhì)。在直接金屬刻蝕中,工藝結(jié)束時會沉積薄層間介質(zhì)。沉積工藝可以在間距緊密處夾止二氧化硅,從而形成空氣間隙。在模擬中,我們探索了空氣間隙形成的基本模型,并計劃了額外的模擬項目。在初始工藝流程中,我們模擬了簡單的空氣間隙填充、氧化物間隙填充和化學(xué)機(jī)械拋光 (CMP)。我們使用SEMulator3D模擬了這一工藝流程(如圖6)。

圖6:空氣間隙工藝形成模擬

高深寬比金屬線

在傳統(tǒng)的大馬士革工藝中,深寬比通常限于2左右。超過這個深寬比,就很難在不形成空隙的情況下沉積金屬線了。直接金屬刻蝕中,金屬高度受限于刻蝕工藝,深寬比可以達(dá)到甚至超過5。因為電阻隨著尺寸的減小而增加,這對于先進(jìn)節(jié)點(diǎn)來說是很重要的工藝助推器。增加金屬高度是持續(xù)電阻微縮的重要方法。直接金屬刻蝕工藝的關(guān)鍵挑戰(zhàn)是減少刻蝕過程中的硬掩膜消耗。我們使用SEMulator3D對這一挑戰(zhàn)進(jìn)行了建模。

混合金屬化

為了減少總電阻,可以為金屬線和通孔使用不同的金屬。imec正在研究中對這一方面進(jìn)行探索。

結(jié)論

我們使用SEMulator3D定義和模擬1.5nm及更先進(jìn)節(jié)點(diǎn)的后段工藝流程。基于這些模擬結(jié)果,我們建立了新掩膜版的設(shè)計規(guī)則。使用模擬推薦的工藝流程,我們成功試產(chǎn)了掩膜版。SEMulator3D模擬出性能助推器的原始概念后,我們也在硅片上對完全自對準(zhǔn)通孔、高深寬比金屬線和空氣間隙等工藝助推器進(jìn)行了演示。這些模擬結(jié)果有助于imec先進(jìn)節(jié)點(diǎn)領(lǐng)域的研究,并作用于硅芯片這個終端產(chǎn)品上。

鳴謝

感謝Martin O'Toole和imec向泛林集團(tuán)分享這項研究。該研究得到了IT2 ECSEL Joint Undertaking的支持。

更多精彩內(nèi)容歡迎點(diǎn)擊==>>電子技術(shù)應(yīng)用-AET<<