以工藝窗口建模探索路徑:使用虛擬制造評(píng)估先進(jìn)DRAM電容器圖形化的工藝窗口

2023-11-23

作者:泛林集團(tuán) Semiverse Solutions 部門半導(dǎo)體工藝與整合高級(jí)工程師王青鵬博士

來(lái)源:泛林集團(tuán)

持續(xù)的器件微縮導(dǎo)致特征尺寸變小,工藝步驟差異變大,工藝窗口也變得越來(lái)越窄[1]。半導(dǎo)體研發(fā)階段的關(guān)鍵任務(wù)之一就是尋找工藝窗口較大的優(yōu)秀集成方案。如果晶圓測(cè)試數(shù)據(jù)不足,評(píng)估不同集成方案的工藝窗口會(huì)變得困難。為克服這一不足,我們將舉例說(shuō)明如何借助虛擬制造評(píng)估 DRAM 電容器圖形化工藝的工藝窗口。

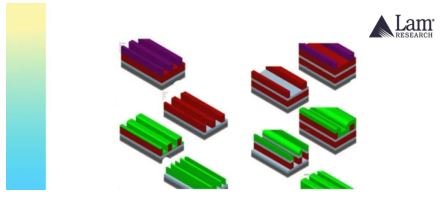

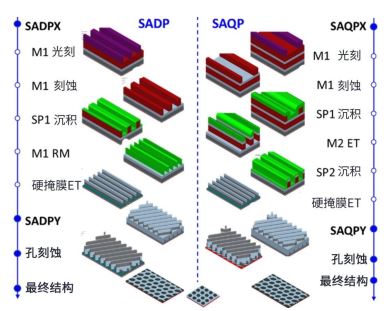

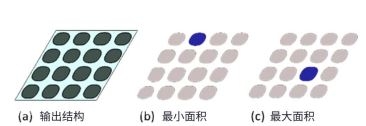

在 DRAM 器件開發(fā)中,必須在硅晶圓上刻蝕用于存儲(chǔ)電荷的電容孔陣列。可用來(lái)制造 40nm 孔陣列的圖形化方案包括極紫外光刻刻蝕、四重光刻刻蝕、雙自對(duì)準(zhǔn)雙重圖形化技術(shù) (SADP)(80nm芯軸間距)和雙自對(duì)準(zhǔn)四重圖形化技術(shù) (SAQP)(160nm芯軸間距)。在這項(xiàng)研究中,我們選擇了浸潤(rùn)式雙 SADP 和 SAQP 圖形化方案,并對(duì)其工藝靈敏性和工藝窗口進(jìn)行了比較。我們?yōu)槊總€(gè)圖形化方案 (SADP和SAQP) 建立了虛擬工藝流程(如圖1),并將電容器孔面積作為電容及其均勻性分析的衡量標(biāo)準(zhǔn)。為了算出孔面積的變化范圍,我們?cè)?SEMulator3D 中使用結(jié)構(gòu)搜索,尋找 4×4 孔陣列中電容器孔面積的最小值和最大值,并計(jì)算出平均面積和面積差值。圖2顯示了一次輸出結(jié)構(gòu)的測(cè)量結(jié)果,其中確定了結(jié)構(gòu)中孔面積的最小值和最大值。

圖1:SADP和SAQP的主要工藝步驟

圖2:最小面積與最大面積的虛擬測(cè)量結(jié)果

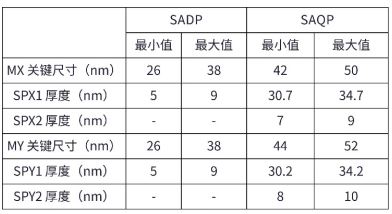

基于以上的虛擬流程和測(cè)量,我們使用 SEMulator3D 分析模塊,進(jìn)行了3000次蒙特卡羅實(shí)驗(yàn)。我們將芯軸關(guān)鍵尺寸和間隔層厚度設(shè)置為實(shí)驗(yàn)設(shè)計(jì)的輸入?yún)?shù),將平均面積和面積變化范圍設(shè)置為輸出參數(shù)。表1列出了 SADP 和 SAQP 工藝的輸入?yún)?shù)值范圍。虛擬實(shí)驗(yàn)設(shè)計(jì)結(jié)果幫助我們研究每項(xiàng)輸入對(duì)平均面積和面積變化范圍的影響。在表1中,MX 表示 X 方向芯軸關(guān)鍵尺寸;MY 表示 Y 方向芯軸關(guān)鍵尺寸;SPX1 表示 X 方向第一個(gè)間隔層厚度;SPX2 表示 X 方向第二個(gè)間隔層厚度;SPY1 表示 Y 方向第一個(gè)間隔層厚度;SPY2 表示 Y 方向第二個(gè)間隔層厚度。

表1:實(shí)驗(yàn)設(shè)計(jì)變量及輸入范圍

平均面積越大、面積變化范圍越小,電容分布就越密集且均勻。通常認(rèn)為,平均面積在900nm2至1100nm2之間,面積變化范圍小于200nm2被定義為實(shí)驗(yàn)成功。在特定條件下,可以為工藝窗口算出成功模擬實(shí)驗(yàn)在總體實(shí)驗(yàn)所占比率(稱為規(guī)格內(nèi)比率),從而生成平均值和3-sigma(±3*標(biāo)準(zhǔn)差)分布。這個(gè)比率表示產(chǎn)生成功標(biāo)準(zhǔn)范圍內(nèi)平均面積和面積變化范圍需要的輸入組合比例。

為了最大化平均±3 sigma窗口中的實(shí)驗(yàn)成功次數(shù),可以通過(guò)調(diào)整輸入工藝參數(shù)平均值的方法,優(yōu)化規(guī)格內(nèi)比率[2]。如果優(yōu)化后的規(guī)格內(nèi)比率仍然不夠高,還可以通過(guò)提高規(guī)格 (3 sigma) 要求,進(jìn)一步對(duì)其進(jìn)行優(yōu)化。我們計(jì)算了不同條件下 SADP 和 SAQP 工藝的規(guī)格內(nèi)比率。在 3 sigma 分布相同的情況下,SADP 工藝的規(guī)格內(nèi)比率比 SAQP 工藝高約10%。調(diào)整芯軸關(guān)鍵尺寸的 3-sigma 規(guī)格后,SADP 工藝的規(guī)格內(nèi)比率接近100%。當(dāng)芯軸關(guān)鍵尺寸相同時(shí),SAQP 工藝的規(guī)格內(nèi)比率較低,表明 SAQP 工藝窗口需要進(jìn)一步緊縮。

結(jié)論

在這項(xiàng)研究中,我們使用虛擬制造為先進(jìn) DRAM 結(jié)構(gòu)中的電容器形成工藝進(jìn)行了工藝窗口評(píng)估和優(yōu)化。虛擬評(píng)估提供了明確且可量化的指導(dǎo),幫助我們判斷在先進(jìn) DRAM 結(jié)構(gòu)中使用不同圖形化方案的工藝難題。最重要的是,我們能在晶圓實(shí)驗(yàn)前確定每個(gè)圖形化方案的最佳工藝目標(biāo)組合和條件允許的最大工藝窗口。

參考資料:

1.A.J., Strojwas, 2006 IEEE International Symposium on Semiconductor Manufacturing (pp. xxiii-xxxii)。

2.Q. Wang, Y. D. Chen, J. Huang, W. Liu and E. Joseph, 2020 China Semiconductor Technology International Conference (CSTIC) (pp. 1-3)。

更多精彩內(nèi)容歡迎點(diǎn)擊==>>電子技術(shù)應(yīng)用-AET<<