在半導體行業(yè)的激烈競爭中,,英特爾和臺積電正展開一場激動人心的工藝之爭,,吸引了業(yè)界的廣泛關注。兩家企業(yè)最新的 18A 工藝和 N2 工藝帶來了一場技術與創(chuàng)新的角逐,。

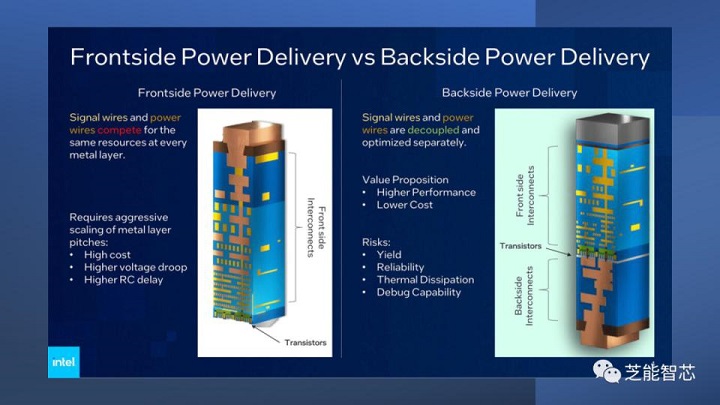

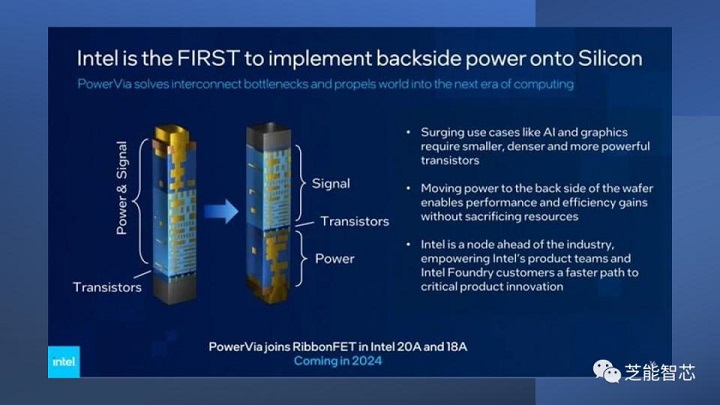

● 英特爾首席執(zhí)行官 Pat Gelsinger 相信將在未來幾年擊敗臺積電,。在接受采訪時,,強調(diào)了 18A 工藝(1.8 納米)與臺積電的 N2(2 納米)節(jié)點。18A 和 N2 都將利用 GAA 晶體管 ( RibbonFET ) ,, 1.8 納米級節(jié)點將采用 BSPND,,一種可優(yōu)化功率和時鐘的背面功率傳輸技術。

● 當然臺積電相信其 N3P(3 納米級)技術將在功耗,、性能和面積(PPA)等方面與英特爾的 18A 相媲美,,而其 N2(2 納米級)將在所有方面超越之。

一)兩家的爭斗

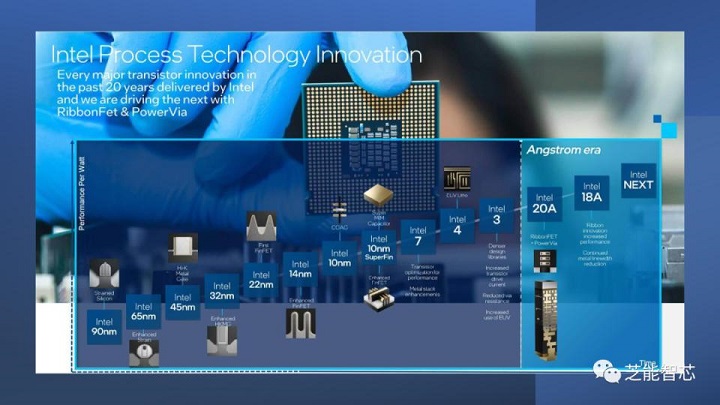

英特爾的 20A(2 納米級)和 18A(1.8 納米級)制造技術即將比臺積電的相應制造工藝提前推出,。

英特爾的 20A 制造技術計劃于 2024 年推出,,將引入 RibbonFET 環(huán)繞柵極晶體管以及背面供電網(wǎng)絡(BSPDN)兩項創(chuàng)新技術,旨在實現(xiàn)更高的性能、更低的功耗和增加的晶體管密度,。與此同時,,英特爾的 18A 生產(chǎn)節(jié)點旨在進一步完善 20A 的創(chuàng)新,并在 2024 年底至 2025 年初提供進一步的 PPA 改進,。

臺積電的 3 納米級 N3,、N3E、N3P 和 N3X 制造工藝都依賴于成熟的 FinFET 晶體管和傳統(tǒng)的電源傳輸網(wǎng)絡,。

臺積電似乎不急于推出其納米片 GAA 晶體管和 BSPDN,,前者將由臺積電的 N2 節(jié)點引入,計劃在 2025 年下半年實現(xiàn)大規(guī)模生產(chǎn),,而后者將在 N2P 上加入,,計劃在 2026 年底開始大規(guī)模生產(chǎn)。 臺積電在財報電話會議中表示:" 內(nèi)部評估顯示,,臺積電的 N3P 與 [ Intel ] 18A 相媲美,,但上市時間更早,技術成熟度更高,,成本也更低,。不帶背面電源的 2 納米技術(N2)比 N3P 和 18A 都更先進,并將在 2025 年推出時成為半導體行業(yè)最先進的技術,。"

英特爾未來幾年的主要目標之一是在技術領導力方面擊敗臺積電,,并從需要領先工藝節(jié)點的公司中獲得晶圓代工訂單。英特爾計劃在未來五個季度推出三個先進的制造工藝,,并在 2024 年下半年至 2025 年上半年開始 2 納米和 1.8 納米級制造技術的大規(guī)模生產(chǎn),。臺積電認為即使是將在 2025 年投入使用的 N3P 節(jié)點,在性能,、功耗和成本等方面也能夠與英特爾的 18A 相媲美,,而 N2 將在市場上投放一年后超越它。顯然臺積電對其即將推出的工藝節(jié)點非常自信,。

二)背面供電網(wǎng)絡(BSPDN)

從表面上看,,臺積電在工藝技術和代工設計方面一直領先,擁有強大的生態(tài)系統(tǒng),。英特爾憑借 18A 工藝取得的進展表明,,半導體競技場上的競爭遠比外界所見更為激烈。背面供電技術是一項頗具潛力的創(chuàng)新,,英特爾成為首家將其實踐應用的公司,,通過將電力傳送到芯片背面而非正面,為熱管理和整體性能提供了優(yōu)勢,。有效的散熱和電力傳輸有助于優(yōu)化芯片布局和設計,,改進功能和熱量分布。這一創(chuàng)新的實施使英特爾再次站在半導體制造的最前沿,實現(xiàn)了戈登 · 摩爾的愿景,。

臺積電和三星也將進入背面供電領域,,但相較于英特爾,可能需要一兩年的時間,。臺積電在這方面的優(yōu)勢之一是與客戶的緊密合作,,為其成功提供了強大支持。英特爾在內(nèi)部生產(chǎn) CPU 小芯片,,同時將小芯片和 GPU 外包給臺積電(N5-N3)。英特爾是否能夠在內(nèi)部生產(chǎn) 18A 及以下的所有小芯片,,尤其是在與 AMD 和 Nvidia 等競爭對手的比較中,。

工藝領先固然重要,但在代工行業(yè),,客戶支持同樣至關重要,。如果英特爾能夠在合理時間內(nèi)完成 BPD 版本,并吸引更多客戶,,那么這可能成為其新的代工收入來源,。然而,在與像臺積電這樣的業(yè)界巨頭競爭時,,英特爾需要著眼于大量客戶芯片的生產(chǎn),,這將是其持續(xù)成功的關鍵。

小結(jié):英特爾與臺積電的工藝之爭為半導體行業(yè)帶來了一場激動人心的競賽,,我們將見證這場競爭的發(fā)展,,看看誰能在技術創(chuàng)新和客戶支持方面取得更大的優(yōu)勢。