使用SEMulator3D進(jìn)行虛擬工藝故障排除和研究

2024-01-30

作者:泛林集團 Semiverse Solutions 部門半導(dǎo)體工藝與整合部經(jīng)理 Brett Lowe

來源:泛林集團

在 3D NAND 存儲器件的制造中,有一個關(guān)鍵工藝模塊涉及在存儲單元中形成金屬柵極和字線。這個工藝首先需要在基板上沉積數(shù)百層二氧化硅和氮化硅交替堆疊層。其次,在堆疊層上以最小圖形間隔來圖形化和刻蝕存儲孔陣列。此時,每層氮化硅(即將成為字線)的外表變得像一片瑞士奶酪。在這些工藝步驟中,很難實現(xiàn)側(cè)壁剖面控制,因為刻蝕工藝中深寬比較高,且存儲單元孔需要極大的深度。因此,刻蝕工藝中可能會出現(xiàn)彎折、扭曲等偏差。從堆疊層頂部到底部,存儲單元孔直徑和孔間隔可存在最高25%的偏差。

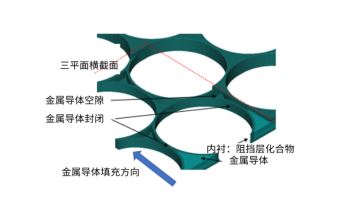

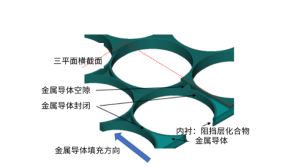

在存儲單元孔中沉積存儲單元材料后,在區(qū)塊外邊緣上圖形化和刻蝕一系列窄長的狹縫溝槽。這第二次刻蝕暴露出狹縫溝槽側(cè)壁中的犧牲氮化硅后,對其從邊緣到中間進(jìn)行橫向刻蝕,直至完全去除。(1) 隨后,沉積阻擋層化合物內(nèi)襯和導(dǎo)電金屬,填充氮化硅層邊緣到中間的空間。這一工藝會生成金屬柵極存儲器單元和字線。(2) 從外部存儲單元孔到狹縫溝槽內(nèi)邊緣的距離稱為“軌距”(如圖1)。該導(dǎo)通路徑提供一條沿字線外邊緣的低電阻傳導(dǎo)通路。字線很長,通常等于存儲區(qū)塊的整個長度。為了維持所需的存儲器開關(guān)速度,需要對字線電阻進(jìn)行高度控制。

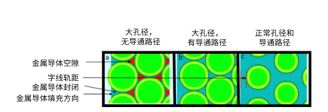

圖1:虛擬模型實驗的俯視圖,每次實驗(a、b和c)設(shè)置不同的實驗條件。a) 模型中有較大存儲單元孔、有空隙、無字線導(dǎo)通路徑。字線空隙標(biāo)紅。由于存儲單元孔間距較小,空隙引發(fā)封閉。b) 模型中有較大存儲單元孔、字線導(dǎo)通路徑正常、無空隙。c)模型中有正常大小存儲單元孔、字線導(dǎo)通路徑正常。

我們使用 SEMulator3D 模型以更好地研究 3D NAND 中字線電阻的影響因素。該研究表明,僅因為去除了存儲單元孔中的導(dǎo)電材料,造成的 3D NAND 字線電阻遠(yuǎn)大于預(yù)期值。這表明,去除犧牲氮化硅,或用導(dǎo)電金屬替換犧牲氮化硅的過程會形成空隙,從而增加字線電阻。SEMulator3D 虛擬模型顯示,如果存儲單元孔過大,或孔間隔過窄,通向字線內(nèi)部的橫向沉積通路將被封閉,并在導(dǎo)電金屬中形成空隙(如圖2)。

圖2:SEMulator3D 虛擬模型展示了字線邊緣的三平面橫截面圖。金屬導(dǎo)體填充沒有從狹縫溝槽邊緣的封閉處持續(xù)到字線中心。電流僅通過內(nèi)襯,從字線中心傳導(dǎo)到封閉處。

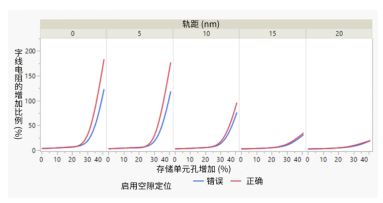

我們使用 SEMulator3D 工藝模型,以不同的存儲單元孔直徑、軌距和空隙定位,進(jìn)行了200次虛擬模型實驗。用 SEMulator3D 電性分析軟件包模擬了字線電阻,隨后從虛擬模型實驗中提取字線電阻,并繪制了電阻增加百分比與軌距、存儲單元孔徑增加和帶有空隙的對比圖(如圖3)。

圖3顯示了空隙形成對字線電阻的影響。如果比較無空隙時的字線電阻增加(紅線)和存在空隙時的字線電阻增加(藍(lán)線),空隙的影響比較明顯。不考慮存儲孔大小,空隙的存在使字線電阻增加了55%。增加外軌距后,存儲單元孔大小對字線電阻的影響減少200%,并將引入空隙對字線電阻的影響降低到可以忽略不計的程度。結(jié)果表明,字線電阻隨存儲孔大小增加而增加。

圖3:字線電阻增加(單位:百分比)與存儲單元孔直徑增加(單位:百分比)和軌距(單位:nm)的關(guān)系圖。紅線表示模型中包含字線空隙的結(jié)果(正確),藍(lán)線表示模型中刪除字線空隙并對其填充的結(jié)果(錯誤)。

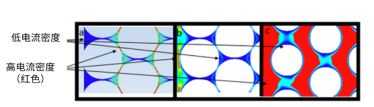

隨著軌距趨于零,迫使更多電流流入字線內(nèi)部區(qū)域。當(dāng)存儲孔尺寸增加時,空隙尺寸增加,低電阻導(dǎo)電金屬和較高電阻的阻擋層化合物內(nèi)襯間的體積減小(如圖4)。當(dāng)保留字線軌距時,字線電阻對存儲孔尺寸和金屬空隙的依賴降至最低。

圖4:虛擬模型實驗中的電流密度俯視圖,每項設(shè)定(如圖a、b和c所示)根據(jù)不同實驗有所變化(參閱圖1)。a) 導(dǎo)通路徑不連續(xù),導(dǎo)致電流流入字線內(nèi)部。b)?存儲孔大小與圖a中的一致,但較寬的導(dǎo)通路徑使電流沿著字線外邊緣流動。c)?字線軌距產(chǎn)生更均勻的電流密度圖形。

使用 SEMulator3D 空隙定位,虛擬模型可以在不考慮存儲孔大小的情況下,預(yù)測空隙對字線電阻的影響。在實際的硅晶圓工藝中,沒有辦法在 3D NAND 工藝開發(fā)中對空隙形成和存儲單元孔大小進(jìn)行分離實驗。SEMulator3D 可實現(xiàn)晶圓廠中很難或者不可能進(jìn)行的實驗。

我們用 SEMulator3D 工藝建模模擬了 3D NAND 字線形成工藝。我們觀察到,上游存儲單元空隙模塊會對下游字線形成模塊產(chǎn)生負(fù)面影響,并導(dǎo)致字線電阻的急劇增加。通過虛擬模型,我們得以模擬上游和下游模塊間存在的問題,并用多次實驗探索潛在的解決方案(在我們的案例中,解決方案涉及設(shè)計上的調(diào)整)。SEMulator3D 工藝建模可以在開發(fā)早期識別工藝和設(shè)計問題,其間無需大量的硅晶圓實驗,這減少了開發(fā)延遲、晶圓制造成本和上市時間。

參考資料:

[1] Handy, “An Alternative Kind of Vertical 3D NAND String”, Jim Handy, Objective Analysis, on Semiconductor Memories, Nov 8, 2013.

[2] A. Goda, “Recent Progress on 3D NAND Flash Technologies”, Electronics2021, 10(24), 3156.

更多精彩內(nèi)容歡迎點擊==>>電子技術(shù)應(yīng)用-AET<<