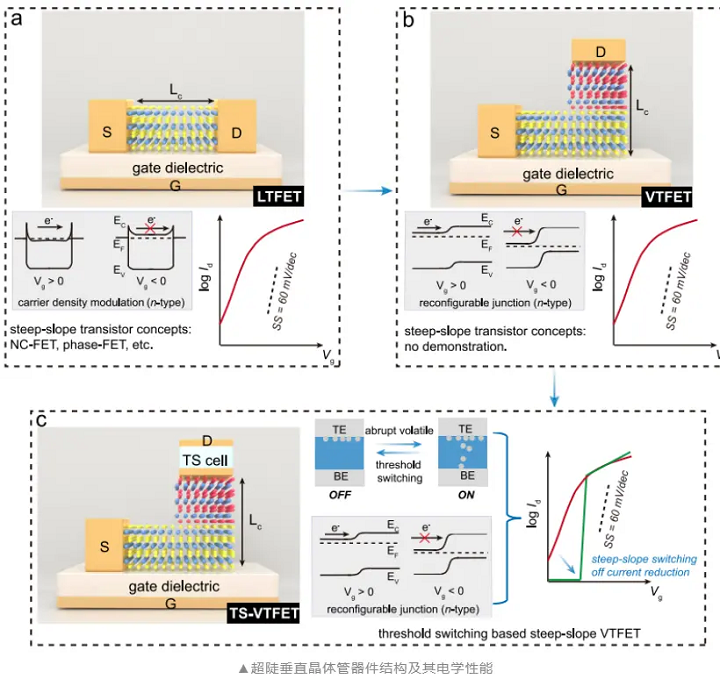

近日,西安電子科技大學(xué)郝躍院士團(tuán)隊(duì)劉艷教授和羅拯東副教授在超陡垂直晶體管器件研究方面取得重要進(jìn)展,相關(guān)研究成果以“Steep-Slope Vertical-Transport Transistors Built from sub-5 nm Thin van der Waals Heterostructures”為題發(fā)表于《自然?通訊》。該工作報(bào)道一種新型晶體管器件技術(shù),將電阻閾值開關(guān)與垂直晶體管進(jìn)行集成,實(shí)現(xiàn)了兼具超陡亞閾值擺幅與高集成密度潛力的垂直溝道晶體管,電流開關(guān)比超過8個(gè)數(shù)量級(jí)且室溫亞60mV/dec電流范圍超過6個(gè)數(shù)量級(jí),為后摩爾時(shí)代高性能晶體管技術(shù)提供了一種新的器件方案。

隨著集成電路制造工藝下探亞5納米技術(shù)節(jié)點(diǎn),傳統(tǒng)的晶體管尺寸微縮路線無法像過去一樣使能“器件-芯片”性能提升與成本控制。在此背景下,學(xué)術(shù)界與工業(yè)界近年來提出多種創(chuàng)新器件技術(shù),以期克服常規(guī)MOSFET的技術(shù)局限。其中,三星、IBM、歐洲微電子中心(IMEC)等國(guó)際研發(fā)機(jī)構(gòu)推出了垂直輸運(yùn)場(chǎng)效應(yīng)晶體管(vertical-transport field-effect transistor, VTFET)器件技術(shù)。通過將電流方向從傳統(tǒng)MOSFET的平面方向轉(zhuǎn)換為垂直方向,該器件結(jié)構(gòu)有望在芯片上垂直構(gòu)造晶體管,從而大幅降低器件占有空間,提高集成密度。

受此啟發(fā),西電研究團(tuán)隊(duì)采用超薄二維異質(zhì)結(jié)構(gòu)造VTFET半導(dǎo)體溝道并與電阻閾值開關(guān)(TS)垂直集成,實(shí)現(xiàn)超陡垂直晶體管(TS-VTFET)。這一器件技術(shù)借助超薄二維半導(dǎo)體出色的靜電調(diào)控,大幅提升器件柵控能力;同時(shí),借助電阻閾值開關(guān)的電壓控制“絕緣-導(dǎo)電”相變特性,該器件的室溫亞閾值擺幅達(dá)到1.52mV/dec,遠(yuǎn)低于常規(guī)MOSFET室溫亞閾值擺幅高于60mV/dec的理論極限。此外,在發(fā)表的概念驗(yàn)證工作中,研究團(tuán)隊(duì)制備的超陡垂直晶體管表現(xiàn)出強(qiáng)大性能,包括電流開關(guān)比高于8個(gè)數(shù)量級(jí)、亞60mV/dec電流區(qū)間超過6個(gè)數(shù)量級(jí)、漏電流小于10fA等,為后摩爾時(shí)代高性能低功耗晶體管技術(shù)提供了一種新的方案。