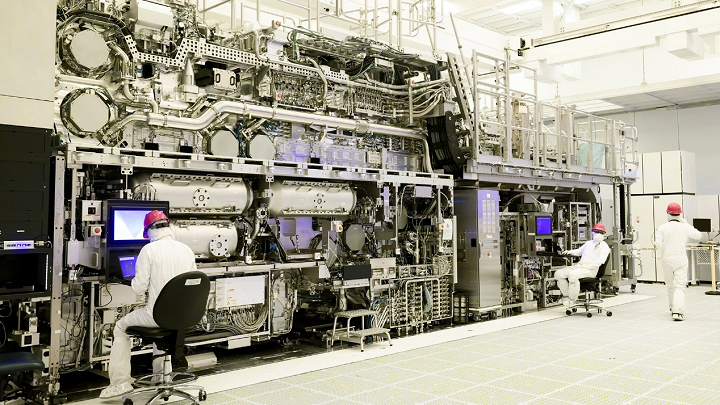

4 月 22 日消息,英特爾近日宣布完成世界首臺商用 High NA EUV 光刻機的安裝。

而在上周的一場電話會議上,英特爾院士馬克?菲利普斯(Mark Phillips)表示這臺耗資約 3.5 億美元(當(dāng)前約 25.38 億元人民幣)的龐然大物年內(nèi)就將啟用。

菲利普斯是英特爾代工旗下邏輯技術(shù)開發(fā)部門的光刻、硬件和解決方案主管。他表示英特爾將于今年晚些時候?qū)?High NA EUV 光刻機投入制程開發(fā)工作。

英特爾將在 18A 尺度的概念驗證節(jié)點上對 High NA EUV 和傳統(tǒng) 0.33NA EUV 光刻的混合使用進(jìn)行測試,并在之后的 14A 節(jié)點上進(jìn)入商業(yè)化量產(chǎn)階段。

菲利普斯預(yù)測 High NA EUV 光刻機至少可在三代的未來節(jié)點上沿用,從而將光刻技術(shù)的名義尺度突破到 1nm 以下量級。

關(guān)于未來光刻技術(shù)發(fā)展,菲利普斯認(rèn)為將光線波長進(jìn)一步縮短至 6.7nm 會引入大量新的問題,包括明顯更大的光學(xué)組件;在他眼中,更高的數(shù)值孔徑(Hyper NA)是可能的技術(shù)方向。

對于 High NA EUV 光刻帶來的單芯片理論最大面積減小問題,菲利普斯表示英特爾正同 EDA 企業(yè)一道就芯片“縫合”技術(shù)進(jìn)行開發(fā),以方便設(shè)計師使用。

本站內(nèi)容除特別聲明的原創(chuàng)文章之外,轉(zhuǎn)載內(nèi)容只為傳遞更多信息,并不代表本網(wǎng)站贊同其觀點。轉(zhuǎn)載的所有的文章、圖片、音/視頻文件等資料的版權(quán)歸版權(quán)所有權(quán)人所有。本站采用的非本站原創(chuàng)文章及圖片等內(nèi)容無法一一聯(lián)系確認(rèn)版權(quán)者。如涉及作品內(nèi)容、版權(quán)和其它問題,請及時通過電子郵件或電話通知我們,以便迅速采取適當(dāng)措施,避免給雙方造成不必要的經(jīng)濟(jì)損失。聯(lián)系電話:010-82306118;郵箱:[email protected]。