1 引言

測(cè)控系統(tǒng)常常需要處理所采集到的各種數(shù)字量信號(hào),。通常測(cè)控系統(tǒng)采用通用MCU完成系統(tǒng)任務(wù),。但當(dāng)系統(tǒng)中采集信號(hào)量較多時(shí),僅依靠MCU則難以完成系統(tǒng)任務(wù),。針對(duì)這一問題,,提出一種基于FPGA" title="FPGA">FPGA技術(shù)的多路數(shù)字量采集" title="多路數(shù)字量采集">多路數(shù)字量采集模塊。利用FPGA的I/O端口數(shù)多且可編程設(shè)置的特點(diǎn),,配以VHDL編寫的FPGA內(nèi)部邏輯,,實(shí)現(xiàn)采集多路數(shù)字量信號(hào)。

2 模塊設(shè)計(jì)方案

2.1 功能要求

該數(shù)字量采集模塊主要功能是采集輸入的36路數(shù)字及脈沖信號(hào),,并將編幀后的信號(hào)數(shù)據(jù)上傳給上位機(jī),,上位機(jī)經(jīng)解包處理后顯示信號(hào)相應(yīng)的狀態(tài)進(jìn)行判斷。

根據(jù)設(shè)計(jì)要求,,所測(cè)量的36路數(shù)字信號(hào)中,,有15路正脈沖信號(hào)。它們均由一個(gè)同步脈沖信號(hào)觸發(fā),,因此需要測(cè)量這些正脈沖的寬度和相對(duì)于同步信號(hào)脈沖的延時(shí),。

要求采集步長不能大于10 ns,即采集頻率高于100 MHz,。而其他數(shù)字信號(hào)需要顯示高低電平狀態(tài),,其中一路信號(hào)是固定頻率信號(hào),需測(cè)量其頻率值,。上位機(jī)要求顯示所采集信號(hào)的狀態(tài),。

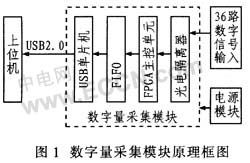

2.2 模塊原理框圖

FPGA內(nèi)部邏輯功能強(qiáng)大,外圍電路設(shè)計(jì)基于簡(jiǎn)單,、可靠的原則,。該模塊由FIFO、USB2.0單片機(jī),、光電隔離器等部分組成,。36路數(shù)字信號(hào)經(jīng)光電隔離器進(jìn)入FPGA主控單元,以供采集,;FPGA處理采集到的信號(hào),,轉(zhuǎn)換成數(shù)據(jù)進(jìn)行編幀,然后寫入FIFO。USB單片機(jī)提取FIFO中的數(shù)據(jù),,通過USB電纜傳送給上位機(jī),,上位機(jī)將傳送來的數(shù)據(jù)解幀,然后顯示所有信號(hào)狀態(tài),。模塊通過電源接口向各個(gè)部分供電,。其原理框圖如圖1所示。

3 模塊電路設(shè)計(jì)

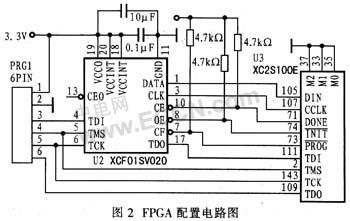

3.1 FPGA配置電路

FPGA是采用XILINX公司的Spantan-II" title="Spantan-II">Spantan-II系列XC2S100E" title="XC2S100E">XC2S100E,,該系列器件的內(nèi)核采用2.5 V供電,,工作頻率高達(dá)200 MHz;I/O端口供電電壓為3.3 V,,可承受5 V的輸入高電平,。Spartan-II系列的FPGA具有豐富的I/O端口資源。其I/O端口輸出緩沖器接收高達(dá)24 mA源出電流和48 mA灌入電流,。

由于FPGA基于RAM工藝技術(shù),,掉電后不能保存信息,因此需要一個(gè)外置存儲(chǔ)器來保存信息,。采用一次可編程的PROM(高有效或低有效)XCF01SV020,,其復(fù)位引腳的極性可編程設(shè)置,供電電壓為3.3 V,。XCF01SVO20的DONE,、INIT、CCLK信號(hào)來自于FPGA XC2S100E,。系統(tǒng)上電后,,首先FPGA初始化,INIT,、DONE置低,。INIT置低后復(fù)位PROM,,此時(shí)由于PROM的CE為低,,因此選取PROM,從而可將數(shù)據(jù)流從DATA引腳輸入到FPGA的DIN引腳,。配置完成后,,F(xiàn)PGA將DONE接高,PROM處于低功耗的待機(jī)模式,,并將DATA引腳置為高阻態(tài),。圖2為FPGA配置電路圖。

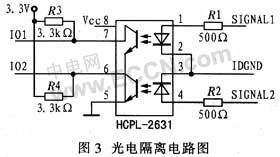

3.2 光電隔離電路

采用高速光電耦合器HCPL-2631,,其開關(guān)頻率高達(dá)10 MHz,,而輸人數(shù)字信號(hào)頻率為120 kHz,完全滿足要求。由于光電耦合器件以光為媒介傳輸信息,,可使輸入輸出隔離,,由于光電耦合器的輸入回路為發(fā)光二極管,其輸入阻抗很小,,而干擾源的內(nèi)阻較大,,根據(jù)分壓原理可知,饋送到光電耦合器輸入端的噪聲干擾電壓變得很小,,從而能有效抑制尖峰脈沖及各種噪聲干擾,,具有較強(qiáng)的抗干擾性能;另外由于光電隔離器的兩端采用不同的接地方式,,因此數(shù)字信號(hào)地和模塊地被完全隔離,。圖3為光電隔離電路圖。

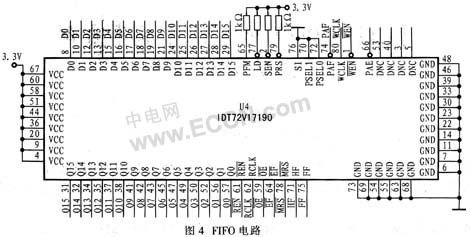

3.3 FIFO電路

FIFO電路采用IDT公司的IDT72V17190器件,,該器件采用3.3 V電壓供電,,16位64 KB容量的FIFO,工作時(shí)鐘高達(dá)100 MHz,。如圖4所示,,F(xiàn)IFO的數(shù)據(jù)輸入D0~D15及PAF、WCLK,、WEN均與FPGA相連,。數(shù)據(jù)輸出Q0~Q15及REN、RCLK,、OE,、EF、MRS,、HF,、FF均與USB2.0單片機(jī)相連。讀FIFO狀態(tài)時(shí),,USB2.0單片機(jī)給出FIFO復(fù)位信號(hào)MRS和使能信號(hào)OE,,然后判斷FIFO的狀態(tài)信號(hào)EF(空)和HF(半滿)。當(dāng)FIFO半滿且非空,,即EF為高,,HF為低時(shí),給出FIFO讀使能信號(hào)REN和讀時(shí)鐘RCLK,,從FIFO中讀出數(shù)據(jù),;寫FIFO時(shí),F(xiàn)PGA判斷FIFO的PAF(幾乎滿)信號(hào),,如果該信號(hào)無效,,則給出寫使能WEN和寫時(shí)鐘WCLK,,將數(shù)據(jù)寫入FIFO。

4 FPGA內(nèi)部邏輯設(shè)計(jì)

FPGA內(nèi)部邏輯主要分為數(shù)字信號(hào)采集,、數(shù)據(jù)緩存和數(shù)據(jù)讀取,、FIFO控制。根據(jù)要求,,信號(hào)采集又分為頻率信號(hào)采集,、20路數(shù)字信號(hào)采集和15路脈沖信號(hào)采集。系統(tǒng)同時(shí)采集三組信號(hào),,再送入外部FIFO中緩存,。由于脈沖信號(hào)的數(shù)據(jù)量較大,時(shí)序不匹配,,因此在信號(hào)采集完后數(shù)據(jù)還應(yīng)緩存,,然后再經(jīng)數(shù)據(jù)編幀送至外部FIFO。內(nèi)部緩存利用VHDL編寫模塊,,但是更簡(jiǎn)易的方法是利用FPGA內(nèi)部的雙口RAM,。因此,F(xiàn)PGA選用Xilinx公司的XCF2S-100E,,其內(nèi)部集成5 KB容量的RAM,,足夠內(nèi)部緩存使用。數(shù)據(jù)經(jīng)信號(hào)采集后送人緩存,,然后由讀取模塊讀出再送入外部FIFO,,整個(gè)模塊采用120 MHz的時(shí)鐘,可以滿足要求大于100 MHz的時(shí)鐘頻率,。采集20路數(shù)字信號(hào)的方法是當(dāng)信號(hào)變化時(shí),,就將當(dāng)前所有數(shù)字信號(hào)的電平狀態(tài)都送入緩存,而對(duì)于頻率信號(hào)和脈沖信號(hào)的采集則采用如下方法,。

4.1 頻率信號(hào)采集

由于頻率信號(hào)只需體現(xiàn)出其頻率大小即可,,因此采集頻率信號(hào)時(shí)只記錄該信號(hào)兩沿間的時(shí)間。即就是設(shè)定一個(gè)16位的計(jì)數(shù)器T,,計(jì)數(shù)器的值隨主時(shí)鐘累加,,當(dāng)判斷到該信號(hào)有變化時(shí),就將計(jì)數(shù)器的值T1送人緩存,,然后將該計(jì)數(shù)器清零,。計(jì)數(shù)器的值繼續(xù)累加,,直到該信號(hào)下一次變化,,再將計(jì)數(shù)器的值T2送入緩存,計(jì)數(shù)器再清零,,以此類推,,來記錄該信號(hào)兩沿間的時(shí)間,。

4.2 脈沖信號(hào)采集

采集脈沖信號(hào)需記錄該信號(hào)的脈寬以及相對(duì)于同步信號(hào)的延遲。記錄方法是:使用一個(gè)單獨(dú)的進(jìn)程,,定義一個(gè)24位的計(jì)數(shù)器TB,,當(dāng)同步信號(hào)的上升沿到來時(shí)開始計(jì)數(shù),當(dāng)同步信號(hào)的下一個(gè)上升沿到來時(shí),,該計(jì)數(shù)器清零,。另一個(gè)進(jìn)程判斷15路脈沖信號(hào)中有一路信號(hào)變化時(shí),將當(dāng)前計(jì)數(shù)器TB的值送人緩存,,并將當(dāng)前所有脈沖信號(hào)的電平狀態(tài)都送入緩存,。

4.3 數(shù)據(jù)的編幀和解幀

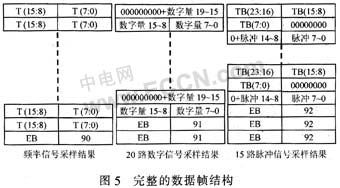

在數(shù)據(jù)采集部分中,當(dāng)同步信號(hào)的上升沿到來時(shí),,將3個(gè)幀標(biāo)志分別寫入3個(gè)緩存,,頻率信號(hào)數(shù)據(jù)的幀標(biāo)志為EB90;20路數(shù)字信號(hào)的幀標(biāo)志為2個(gè)EB91,;15路脈沖信號(hào)數(shù)據(jù)的幀標(biāo)志為3個(gè)EB92,。讀取數(shù)據(jù)模塊中,當(dāng)同步信號(hào)的下降沿到來時(shí),,開始讀取緩存的數(shù)據(jù)送至外部FIFO,,并判斷當(dāng)讀取一個(gè)EB90后,開始讀取緩存的數(shù)據(jù),,并送入外部FIFO,;當(dāng)讀到兩個(gè)EB91后,讀取緩存的數(shù)據(jù),,并送入外部FIFO,;當(dāng)讀到3個(gè)EB92后表明一幀數(shù)據(jù)讀取完畢,等待下一個(gè)同步信號(hào)的下降沿后再開始讀取下一幀數(shù)據(jù),。由于外部FIFO是16位,,所以數(shù)據(jù)中不滿16位的都用0將數(shù)據(jù)補(bǔ)充完整,完整的數(shù)據(jù)幀結(jié)構(gòu)如圖5所示,。

上位機(jī)收到一幀數(shù)據(jù)后進(jìn)行解幀處理,,對(duì)于頻率信號(hào)數(shù)據(jù),將這些T值相加并求平均得出T’,,再乘以2,,由于系統(tǒng)時(shí)鐘是120 MHz,所以2T’/120為頻率信號(hào)周期(μs級(jí)),,然后求倒數(shù)即可得出該信號(hào)的頻率值,。

20路數(shù)字量信號(hào)數(shù)據(jù)直接顯示其電平狀態(tài)。脈沖信號(hào)數(shù)據(jù)則先判斷哪一路(多路)脈沖信號(hào)發(fā)生變化,,再判斷該信號(hào)(幾路信號(hào))的電平狀態(tài),。若為高電平,,則對(duì)應(yīng)的時(shí)間應(yīng)為TBa;若為低電平,,則對(duì)應(yīng)的時(shí)間應(yīng)為TBb,。TBa即為該脈沖信號(hào)相對(duì)于同步信號(hào)的延遲,而TBb-TBa的值即為該脈沖信號(hào)的正脈沖脈寬,。

5 結(jié)束語

針對(duì)測(cè)控系統(tǒng)監(jiān)測(cè)信號(hào)數(shù)量較多的問題,,提出了一種基于FPGA的多路數(shù)字量采集與處理模塊,設(shè)計(jì)了相應(yīng)的電路和FPGA邏輯,。在綜合調(diào)試成功的基礎(chǔ)上,,該多路數(shù)字量采集模塊已成功應(yīng)用于某測(cè)試系統(tǒng)。