摘 要:依據(jù)X射線安檢設(shè)備各部分工作原理及控制要求,本文采用FPGA和以太網(wǎng)技術(shù)設(shè)計了基于FPGA的X射線安檢設(shè)備控制器。本文以Xilinx公司的ISE為開發(fā)平臺,在ModelSim中仿真了控制器各個模塊的功能,得到了符合控制器要求的波形。

引言

X射線安檢設(shè)備廣泛應(yīng)用于機場、車站、海關(guān)、港口、倉庫等地。近年來由于犯罪分子大量使用先進的偽裝技術(shù),使傳統(tǒng)的安檢設(shè)備顯得力不從心。針對上述情況,本文設(shè)計了基于FPGA的X射線安檢設(shè)備控制器,該控制器通過加載Thin TCP/IP接入以太網(wǎng),使得多臺PC共同對可疑物品的圖像數(shù)據(jù)進行分析,進而提高鑒別精度。

工作原理及控制要求

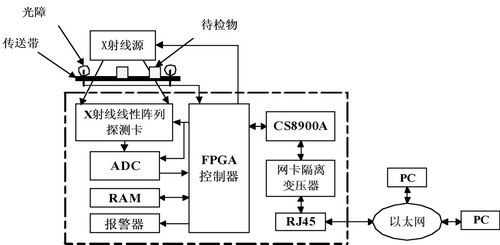

X射線安檢設(shè)備主要由X射線源、傳送裝置、控制器、X射線線性陣列探測卡、以太網(wǎng)控制器(CS8900A)、屏蔽輻射所需的機械裝置、裝有該設(shè)備配套軟件的PC等組成,X射線安檢設(shè)備原理如圖1所示。

圖1中,當控制器產(chǎn)生X射線觸發(fā)信號時,X射線源發(fā)出圓錐形X射線束,該射線束經(jīng)準直器后變?yōu)樯刃纹矫嫔渚€束。射線束穿過傳送帶上待檢測物,X射線部分能量被吸收,最后轟擊X射線線性陣列探測卡上的晶體管。被檢測物體以某一速度相對于探測卡和X射線源移動時,探測卡逐行采集經(jīng)過物體的射線,晶體-光電二極管將X射線轉(zhuǎn)換成一個正比于所吸收的X射線流量和能量的電流信號,經(jīng)放大和積分后,得到一個正比于積分電流乘積分時間的電壓,再經(jīng)A/D轉(zhuǎn)換后送往圖像數(shù)據(jù)處理單元。

圖1 X射線安檢設(shè)備原理示意圖

CS8900A工作原理

CS8900A是一個集成了ISA總線接口的10Base-T以太網(wǎng)控制器。發(fā)送數(shù)據(jù)時,可以采用中斷模式和查詢方式。如果采用中斷模式發(fā)送數(shù)據(jù)幀,在收到主機發(fā)來的命令后檢測內(nèi)部空間,若空間足夠大,芯片通知主機傳送數(shù)據(jù),主機接到通知后發(fā)送數(shù)據(jù)包。發(fā)送過程中由CS8900A自動為要發(fā)送的數(shù)據(jù)幀添加前導(dǎo)符、定界符、CRC校驗碼等。若相應(yīng)的寄存器已被設(shè)置,還會引發(fā)發(fā)送成功中斷。如果采用查詢方式發(fā)送數(shù)據(jù),則主機對相應(yīng)的寄存器進行查詢,若可以發(fā)送,CS8900A將數(shù)據(jù)幀加幀頭,生成校驗碼,最后發(fā)送至以太網(wǎng)中。

接收時,CS8900A將自動地從網(wǎng)絡(luò)中讀取數(shù)據(jù)包,在經(jīng)過解碼、去掉幀頭和地址檢驗等步驟后,將數(shù)據(jù)幀在片內(nèi)進行緩存。在CRC校驗通過后,CS8900A會根據(jù)初始化配置情況,通知主機收到了數(shù)據(jù)幀。最后選擇I/O模式、Memory模式、DMA模式中的一種,將數(shù)據(jù)傳送到主機的存儲區(qū)中。本設(shè)計選用I/O模式對數(shù)據(jù)進行讀取。

FPGA控制器工作原理

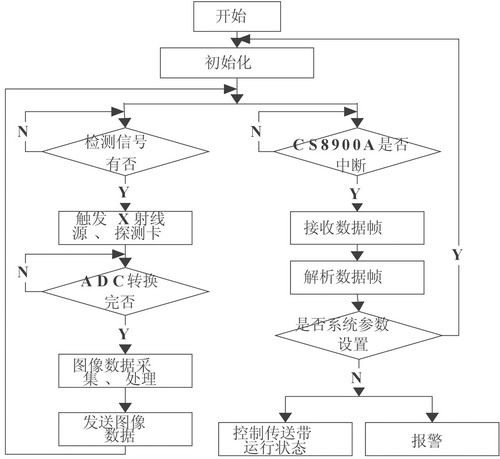

系統(tǒng)上電后,F(xiàn)PGA控制器初始化X射線源、CS8900A、X射線線性陣列探測卡等。由于FPGA內(nèi)部邏輯是并發(fā)機制,所以以下進程是并發(fā)的:接收到檢測信號后觸發(fā)X射線源、X射線線性陣列探測卡,當接收到ADC的EOC端信號后進行圖像數(shù)據(jù)的接收、處理、發(fā)送;接收到CS8900A中斷信號后進行數(shù)據(jù)解析,根據(jù)解析的數(shù)據(jù)進行參數(shù)設(shè)置、控制傳送帶的運行狀態(tài)、報警等相應(yīng)操作。工作流程如圖2所示。

圖2 X射線安檢設(shè)備控制器工作流程圖

控制要求

系統(tǒng)需要完成初始化、圖像數(shù)據(jù)采集、控制傳送帶運行狀態(tài)、報警等。FPGA控制器通過以太網(wǎng)網(wǎng)卡接收PC發(fā)來的參數(shù)數(shù)據(jù)對整個系統(tǒng)控制調(diào)節(jié)。

控制器設(shè)計

根據(jù)控制要求,控制器主要實現(xiàn)解析IP分組、數(shù)據(jù)處理、產(chǎn)生控制信號、生成IP分組等任務(wù)。解析IP分組實際上是對TCP/IP協(xié)議的解析;生成IP分組就是進行數(shù)據(jù)的封裝。本文是基于FPGA芯片設(shè)計的控制器,所以,解析IP分組、數(shù)據(jù)處理、產(chǎn)生控制信號、生成IP分組都是以邏輯電路形式出現(xiàn)在FPGA中。

FPGA控制器中TCP/IP協(xié)議的裁剪方案

隨著互聯(lián)網(wǎng)應(yīng)用的迅猛發(fā)展,TCP/IP協(xié)議已成為嵌入式互聯(lián)網(wǎng)的主體構(gòu)架。TCP/IP協(xié)議通常被認為是一個四層體系結(jié)構(gòu),包括鏈路層、網(wǎng)絡(luò)層、傳輸層和應(yīng)用層。在本設(shè)計中,根據(jù)控制器的具體要求,對TCP協(xié)議進行了適當?shù)牟眉簦瑑H實現(xiàn)了四個協(xié)議:ARP(地址解析)、IP(網(wǎng)絡(luò)協(xié)議)、ICMP(控制報文協(xié)議)、TCP。

TCP是一種面向連接的協(xié)議,它能提供高可靠性服務(wù)。通過使用序列號和確認信息,TCP協(xié)議能夠向發(fā)送方提供到達接收方的數(shù)據(jù)包的傳送信息,從而實現(xiàn)端對端的通信,為了保障圖像數(shù)據(jù)的可靠性,本控制器采用該協(xié)議。

FPGA控制器片內(nèi)邏輯設(shè)計

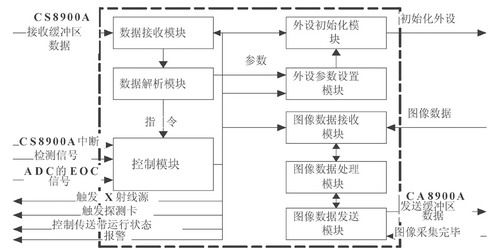

本文采用VHDL分模塊設(shè)計了基于FPGA的安檢設(shè)備控制器。FPGA片內(nèi)邏輯設(shè)計框圖如圖3所示。

圖3 FPGA片內(nèi)邏輯設(shè)計框圖

數(shù)據(jù)接收模塊、數(shù)據(jù)解析模塊

圖3中,數(shù)據(jù)接收模塊實現(xiàn)CS8900A與FPGA內(nèi)數(shù)據(jù)解析模塊的鏈接。當控制模塊產(chǎn)生確認接收數(shù)據(jù)信號時,數(shù)據(jù)接收模塊將CS8900A接收緩沖區(qū)中的數(shù)據(jù)讀出,然后將其寫入數(shù)據(jù)解析模塊。數(shù)據(jù)解析模塊實際上是將上述TCP/IP裁剪協(xié)議硬件化,主要用于解析來自數(shù)據(jù)接收模塊的數(shù)據(jù),將解析的數(shù)據(jù)與預(yù)存于FPGA內(nèi)的數(shù)據(jù)表對照。若解析的結(jié)果是指令和外設(shè)參數(shù),將其分別寫入控制模塊和外設(shè)參數(shù)配置模塊,否則將其丟棄。

控制模塊

控制模塊是FPGA控制器的核心模塊,主要用于接收檢測信號后觸發(fā)X射線源、探測卡;接收ADC的EOC端信號后對圖像數(shù)據(jù)接收模塊產(chǎn)生采集數(shù)據(jù)信號;接收CS8900A中斷信號后對數(shù)據(jù)接收模塊產(chǎn)生接收網(wǎng)卡緩沖區(qū)中數(shù)據(jù)信號;據(jù)解析模塊所處理的指令,相應(yīng)地有如下響應(yīng):產(chǎn)生外設(shè)參數(shù)配置信號、產(chǎn)生控制傳送帶運行狀態(tài)信號、產(chǎn)生報警信號。

外設(shè)初始化和參數(shù)配置模塊

外設(shè)初始化模塊在系統(tǒng)上電時,對控制器外設(shè)發(fā)送初始化信號,然后檢測控制模塊對其是否發(fā)送指令,若有指令,則重新初始化外設(shè)。外設(shè)參數(shù)配置模塊用于對外設(shè)進行參數(shù)設(shè)置,當控制模塊對其產(chǎn)生參數(shù)配置信號時,該模塊將參數(shù)寫入初始化模塊,

圖像數(shù)據(jù)接收、處理及發(fā)送模塊

圖像數(shù)據(jù)接收模塊實現(xiàn)ADC與控制模塊、圖像數(shù)據(jù)處理模塊鏈接。當控制模塊產(chǎn)生圖像數(shù)據(jù)采集信號時,接收模塊給X射線線性陣列探測卡發(fā)送啟動采集信號,然后將ADC圖像數(shù)據(jù)寫入處理模塊。處理模塊針對內(nèi)置幾何校正、灰度變換、偽彩色等多種清晰度增強算法,利用數(shù)字圖像處理技術(shù),將圖像對比度和清晰度進行增強。發(fā)送模塊對處理模塊處理好的圖像數(shù)據(jù)進行IP封裝,然后將其寫入CS8900A發(fā)送數(shù)據(jù)緩沖區(qū),啟動網(wǎng)卡,將此數(shù)據(jù)發(fā)送到所連接的網(wǎng)絡(luò)上。

實驗與驗證

由于VHDL是并發(fā)程序,所以要把順序執(zhí)行的思想轉(zhuǎn)化為并發(fā)設(shè)計思想。本設(shè)計采用Xilinx公司的ISE8.1在Virtex- xc2v6000芯片上實現(xiàn)了控制功能,在Modelsim SE6.1b中進行了仿真。由仿真結(jié)果得出,控制信號時序正確,符合控制要求。

結(jié)語

本文在分析X射線安檢設(shè)備部分組成器件工作原理及控制要求的基礎(chǔ)上,設(shè)計了FPGA內(nèi)部邏輯,給出了控制器的工作流程,驗證了控制信號時序的正確性。預(yù)計此種控制器可以帶來可觀的經(jīng)濟效益和市場前景。■