引 言

有潛在缺陷的芯片有可能通過生產(chǎn)測試,但是在實際應(yīng)用中卻會引起早期失效的問題,進而引起質(zhì)量問題。為了避免這個問題,就需要在產(chǎn)品賣給客戶之前檢測出這種有問題的芯片。一般的檢測技術(shù)包括Burn—in、IDDQ測試、高壓測試和低壓測試等。Burn—in是一種有效的也是目前應(yīng)用最廣泛的測試技術(shù),但是Burn—in的硬件設(shè)備相當(dāng)昂貴,而且測試時間也比較長,從而間接地增加了產(chǎn)品的成本。IDDQ測試對于大規(guī)模集成電路,特別是亞微米電路效果不理想,主要是由于隨著電路規(guī)模的增加和尺寸的減少,暗電流也會增加。高壓檢測對電路中的異物連接,如金屬短路,也沒有很好的效果,甚至有時會掩蓋此類缺陷。在遠低于正常運行電壓的環(huán)境下,正常芯片和有缺陷的芯片有著不同的電性表現(xiàn),因此可以根據(jù)正常芯片的數(shù)據(jù)設(shè)置最小電壓,根據(jù)此數(shù)值來判斷芯片是否合格。

以下將具體介紹最小電壓(MINVDD)測試方法。

1 合格芯片的最小電壓

CMOS電路的正常運轉(zhuǎn)依靠正常的電壓供給。在正常的范圍內(nèi),電壓供給越高,電路就會運行得越快;同樣,電壓供給越低,電路就會運行得越慢。如果電壓足夠低,電路就會輸出錯誤信號或者停止運行。最小電壓就是電路能夠輸出正確邏輯值的電壓臨界值。

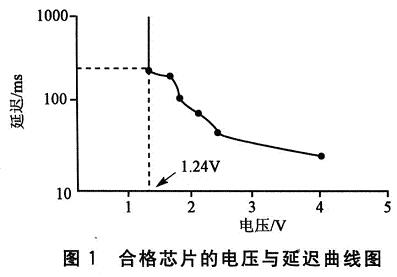

圖1是O.7μm技術(shù)制造的芯片的電壓與延遲的關(guān)系曲線圖。正常的電源電壓是5 V,當(dāng)電壓降低時,芯片運行的延遲就相應(yīng)地增加。當(dāng)電壓低于1.24 V時,芯片就不能輸出正確的邏輯數(shù)值。因此這種芯片的最小電壓值就是1.24 V。

2 有缺陷芯片的最小電壓

不合格芯片的缺陷類型主要有:金屬污染物造成的短路,氧化物污染物造成的短路,閾值電壓偏移,電性通道開路。本文主要針對在實際生產(chǎn)中具有代表性的金屬污染物造成的短路、閾值電壓偏移和電性通道開路來做最小電壓測試的研究。

2.1 金屬性短路

金屬性短路是在封裝前隨機地沾染到金屬微粒,從而在電路節(jié)點處造成的短路。圖2是一個典型的金屬性短路的模型。可以看到‘a’與‘b’之間的金屬微粒造成了2條電路之間的短路,并假設(shè)該金屬微粒的電阻是Rm,INl口輸入邏輯“0”,IN2口輸入邏輯“1”。如圖2所示,電流的路徑由X1中的PMOS,金屬微粒,X3中的NMOS電路組成,因此,a、b之間的電壓值就不是VDD與GND之間的電壓,而是介于兩者之間的一個值。

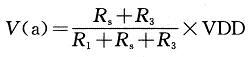

假設(shè)PMOS的電阻是R1,NMOS電阻是R3。R1、R3、Rs就組成了一個分壓串聯(lián)電路,則a處的電壓可以表示成:

當(dāng)電源電壓變小時,由于R1和R3增大,V(a)會隨之下降。因此從輸入INl到OUTl之間的延遲會由于反相器X2延遲的增加而增加。當(dāng)電源電壓降到一定數(shù)值時,V(a)就會低于X2的門限電壓,輸出邏輯“1”,而正確的輸出結(jié)果應(yīng)該是邏輯“0”,在這個電壓值處,電路的功能就開始發(fā)生錯誤。這點電壓就是最小電壓值,也就是判斷芯片是否具有金屬性缺陷的數(shù)值標(biāo)準(zhǔn)。

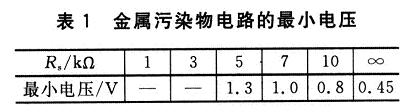

表1列出了當(dāng)金屬微粒的電阻不同時,所對應(yīng)的最小電壓值。合格芯片的最小電壓值是O.45 V,當(dāng)Rs小于3kΩ時,電路在正常的電源電壓(實驗中為1.8 V)下就會失效;當(dāng)Rs的范圍在3 kΩ到10 kΩ時,最小電壓值逐步遞減,但是仍然遠高于O.45 V。

2.2 閾值電壓的偏移

如果一個晶體管有一個很大的閾值電壓偏移,那它的跨導(dǎo)將會很小。因此晶體管的驅(qū)動能力就會很低,繼而在周期轉(zhuǎn)化中會有更多的額外延遲。下面將會初步研究由閾值電壓偏移所引起的最小電壓的變化。

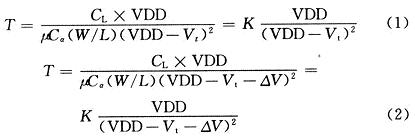

最小電壓的另一個定義就是使得芯片狀態(tài)轉(zhuǎn)換無限延遲的臨界電壓。上面的公式中,CL是寄生電容,Cα是感生電容,W/L是柵級與源漏極的尺寸比,VDD是電源電壓,Vt是芯片正常運行的最小電壓,△V是閾值電壓偏移量。式(1)是CMOS門電路的延遲計算公式。根據(jù)式(1),當(dāng)VDD=Vt時,電路的延遲會無限大,因此合格芯片的最小電壓就是處于Vt的臨界值。當(dāng)閾值電壓有一定偏移△V時,延遲計算公式如式(2)所示,當(dāng)VDD=Vt+△V時,延遲將會無限大。因此可見,由于閾值電壓偏移的存在,芯片的最小電壓增加了,偏移量越大,最小電壓增加量就越大。

2.3 電性通道開路的最小電壓

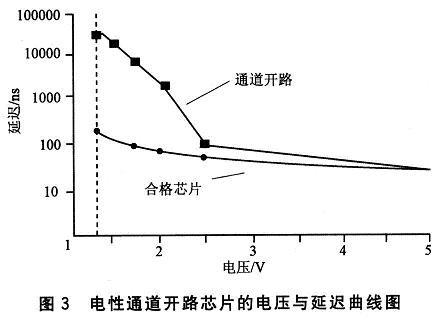

電性通道開路是不正常厚度的氧化層所引起的電流的流動。當(dāng)氧化層厚度由于工藝或者隨機原因變薄,并超出了正常的標(biāo)準(zhǔn)范圍,就會引起電流穿透氧化層流入到其他的電路層。當(dāng)此電流達到一定程度的時候就會引起芯片的不正常工作狀態(tài)。然而在產(chǎn)品測試?yán)铮哂羞@種缺陷的芯片的表現(xiàn)卻與合格芯片一樣,只有在環(huán)境惡劣或者使用一段時間后才會表現(xiàn)出來。圖3是合格芯片與通道開路的不合格芯片的延遲曲線圖。隨著電壓降低,有通道開路問題的芯片的延遲速度遠大于正常芯片,但是它們的最小電壓值卻是一樣的,因為通道開路只會引起時間上的失效,而不會影響芯片的最小電壓。

3 結(jié) 論

最小電壓測試就是利用合格芯片與不合格芯片之間最小電壓的差別來進行測試,有缺陷芯片的最小電壓遠高于合格芯片。最小電壓檢測對于金屬性短路(2條金屬線之間的短路)、氧化物短路(晶體管中斷的短路,例如小孔或者不合格的氧化層厚度)、閾值電壓偏移(工藝的偏差)以及通道開路(絕緣材料斷裂)等失效模式是十分有效的,上述實驗結(jié)果顯示出這一方法的有效性。

實驗結(jié)果也表明了最小電壓測試是一種有效的可靠性檢測技術(shù)。最小電壓測試和超低壓測試都是把芯片放在低壓環(huán)境下進行測試,測試電壓必須是已經(jīng)確定好的最小電壓值,通過檢測在最小電壓值上能否正確運行,或者正確輸出邏輯值,檢測出有潛在缺陷的芯片,從而提高芯片的質(zhì)量和可靠性。