前言

腦電信號EEG(Electroencephalography)是由腦神經(jīng)活動產(chǎn)生并存在于中樞神經(jīng)系統(tǒng)的自發(fā)性電位活動,含有豐富的大腦活動信息。它是大腦研究、生理研究和臨床腦疾病診斷的重要手段。記錄腦電信號,可為臨床診斷提供依據(jù)。因此,提取腦電信號具有重要的現(xiàn)實(shí)意義。由于腦電信號處理一般都是基于數(shù)字技術(shù),因此電極采集到的模擬信號經(jīng)信號調(diào)理后,通過A/D轉(zhuǎn)換器轉(zhuǎn)換成數(shù)字信號是必不可少的過程。這里提出一種基于FPGA和AD977A的腦電信號數(shù)據(jù)采集系統(tǒng),采用FPGA作為信號處理器,并控制模數(shù)轉(zhuǎn)換,從而實(shí)現(xiàn)高可靠性,高通用性的腦電信號數(shù)據(jù)采集系統(tǒng)。

2 系統(tǒng)總體設(shè)計(jì)

通過對人體進(jìn)行視覺刺激、聽覺刺激或神經(jīng)刺激,使人體的大腦皮層產(chǎn)生一個誘發(fā)電位,通過電極連接來獲取該誘發(fā)電位,將此電位經(jīng)放大濾波后使其滿足采集系統(tǒng)要求,輸出的模擬信號通過高速串門A/D轉(zhuǎn)換器AD977A進(jìn)行模數(shù)轉(zhuǎn)換。給FPGA一個啟動/停止信號,用其控制模數(shù)、數(shù)模轉(zhuǎn)換等。采用USB器件與FPGA直接連接,這樣通過時(shí)序即可控制FP-GA與USB的通信。圖1為系統(tǒng)總體設(shè)計(jì)框圖。

3 高速串行A/D轉(zhuǎn)換器AD977A簡介

A/D轉(zhuǎn)換器種類很多,其中F1ash A/D轉(zhuǎn)換器的轉(zhuǎn)換速度高,但分辨率低,適用于雷達(dá)信號的采集及處理等方面;∑-△A/D轉(zhuǎn)換器的轉(zhuǎn)換精度高,但轉(zhuǎn)換速度低,適用于音頻及低頻信號的采集處理等領(lǐng)域;逐次逼近型A/D轉(zhuǎn)換器的轉(zhuǎn)換速度和分辨率介于前兩者之間,適用于控制系統(tǒng)等中速率采集而分辨率要求較高的場合。而AD977A是一款逐次逼近型A/D轉(zhuǎn)換器,AD977A具有以下主要特點(diǎn):單電源5 V供電;最高采樣速率為200 kS/s;內(nèi)部2.5 V參考電源可選;高速串行數(shù)據(jù)接口;內(nèi)部時(shí)鐘可選;低功耗,最大功耗100 mW,省電模式下50 μW;輸入電壓范圍:單極性0~4 V,0~5 V和0~10 V;雙極性-3.3~+3.3 V,-5~+5 V和-10~+10 V;采用20針DIP或SOIC封裝。AD977A內(nèi)部功能框圖如圖2所示。

AD977A的控制引腳的功能描述如下:R1IN、R2IN、R3IN為模擬信號輸入端;AGND1、AGND2為模擬地;DGND為數(shù)字地:CAP為緩沖輸出參考端;REF為基準(zhǔn)電壓;SB/BTC用于選擇輸出數(shù)據(jù)格式,高電平為二進(jìn)制碼,低電平為二進(jìn)制補(bǔ)碼;EXT/INT用于選擇DATACLK時(shí)鐘模式,高電平選擇外部時(shí)鐘,低電平選擇內(nèi)部時(shí)鐘;SYNC是外部時(shí)鐘模式下幀同步信號輸出:DATACLK為串行數(shù)據(jù)時(shí)鐘端;DATA用于輸出轉(zhuǎn)換結(jié)果:TAG為級聯(lián)輸入端:R/C用于讀取/轉(zhuǎn)換控制信號,低電平時(shí)啟動A/D轉(zhuǎn)換,高電平時(shí)讀取A/D轉(zhuǎn)換結(jié)果;CS是片選信號;BUSY是工作狀態(tài)輸出,當(dāng)AD977A進(jìn)行模數(shù)轉(zhuǎn)換時(shí)為低電平,轉(zhuǎn)換結(jié)束后恢復(fù)高電平;PWRD為低電平輸入端;VANA為模擬電壓輸出端;VDIC為數(shù)字電壓輸出端。

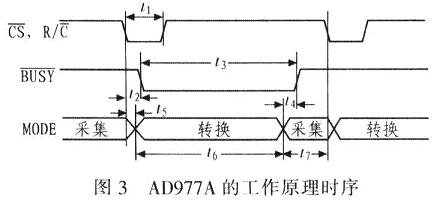

AD977A的工作原理時(shí)序如圖3所示。當(dāng)cs為低電平時(shí),R/C電平跳為低電平,AD977A的內(nèi)部電容陣列保持輸入信號,并開始模數(shù)轉(zhuǎn)換。一旦轉(zhuǎn)換開始,BUSY引腳電平也跳為低電平,并一直持續(xù)到轉(zhuǎn)換結(jié)束才恢復(fù)為高電平。模數(shù)轉(zhuǎn)換結(jié)果的輸m以及產(chǎn)生幀同步都是由時(shí)鐘信號DATACLK控制。

AD977A有內(nèi)、外部時(shí)鐘兩種工作模式。當(dāng)EXT/INT處于低電平時(shí),其工作在內(nèi)部時(shí)鐘模式;高電平時(shí),則工作在外部時(shí)鐘模式。內(nèi)部時(shí)鐘模式下,R/C啟動轉(zhuǎn)換,在轉(zhuǎn)換期間,AD977A的DATACLK引腳輸出16個連續(xù)的時(shí)鐘脈沖,DA-TA引腳同步輸出上一次轉(zhuǎn)換的結(jié)果。而在外部時(shí)鐘模式下,則通過CS、R/C和DATACLK信號控制轉(zhuǎn)換期間輸出上一次的轉(zhuǎn)換結(jié)果或轉(zhuǎn)換結(jié)束后輸出本次轉(zhuǎn)換結(jié)果,控制是否產(chǎn)生幀同步信號。因而外部時(shí)鐘模式有以下6種工作方式:(1)連續(xù)時(shí)鐘,轉(zhuǎn)換期間讀取上一次轉(zhuǎn)換數(shù)據(jù),產(chǎn)生幀同步;(2)連續(xù)時(shí)鐘,轉(zhuǎn)換完成讀取本次轉(zhuǎn)換數(shù)據(jù),產(chǎn)生幀同步;(3)不連續(xù)時(shí)鐘,轉(zhuǎn)換完成讀取本次轉(zhuǎn)換數(shù)據(jù),不產(chǎn)生幀同步;(4)不連續(xù)時(shí)鐘,轉(zhuǎn)換期間讀取上一次轉(zhuǎn)換數(shù)據(jù),不產(chǎn)生幀同步;(5)不連續(xù)時(shí)鐘,轉(zhuǎn)換完成讀取本次轉(zhuǎn)換數(shù)據(jù),產(chǎn)生幀同步;(6)不連續(xù)時(shí)鐘,轉(zhuǎn)換期間讀取上一次轉(zhuǎn)換數(shù)據(jù),產(chǎn)生幀同步。

4 FPGA的優(yōu)點(diǎn)

FPGA即現(xiàn)場可編程門陣列,它既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點(diǎn);FPGA具有體系結(jié)構(gòu)和邏輯單元設(shè)計(jì)靈活、集成度高以及適用范圍廣等特點(diǎn),兼容PLD和通用門陣列的優(yōu)點(diǎn),可實(shí)現(xiàn)較大規(guī)模的電路,編程靈活;其他與門陣列ASIC相比,F(xiàn)PGA具有設(shè)計(jì)開發(fā)周期短、設(shè)計(jì)制造成本低、開發(fā)工具先進(jìn)、標(biāo)準(zhǔn)產(chǎn)品無需測試、質(zhì)量穩(wěn)定以及可實(shí)時(shí)在線檢測等優(yōu)點(diǎn)。

5 AD977A在采集系統(tǒng)中的應(yīng)用

5.1 AD977A與FPGA的接口電路

模擬信號由VIN端口輸入,輸入電壓范圍采用-5~+5 V。AD977A由CS選通,R/C啟動A/D轉(zhuǎn)換,輸出數(shù)據(jù)、時(shí)鐘為DATA與DATACLK同步的形式串行輸出,BUSY為忙輸出端、標(biāo)志轉(zhuǎn)換是否結(jié)束。這5個端口和FPGA的端口相連接。具體A/D轉(zhuǎn)換電路的實(shí)現(xiàn)如圖4所示。

5.2 設(shè)計(jì)電路需注意的問題

A/D轉(zhuǎn)換部分設(shè)計(jì)會對整體精度造成影響,本著提高精度和準(zhǔn)確度的原則。設(shè)計(jì)時(shí)要注意以下問題:

(1)參考電壓源的選取AD977A有內(nèi)置的參考電壓源,但是溫度系數(shù)較大,因此采用外加溫度系數(shù)小的參考電壓源REF02。減小溫度影響,提高準(zhǔn)確度。這個基準(zhǔn)很重要,不穩(wěn)定將對轉(zhuǎn)換結(jié)果帶來影響;

(2)偏置和增益的調(diào)整AD977A需要調(diào)節(jié)零點(diǎn)偏置和增益誤差,保證A/D轉(zhuǎn)換的高準(zhǔn)確度。其實(shí)就是通過典型采樣點(diǎn)的轉(zhuǎn)換結(jié)果,調(diào)整典型電路中電位器串入電路的阻值,實(shí)現(xiàn)準(zhǔn)確轉(zhuǎn)換;

(3)共地的處理 使A/D轉(zhuǎn)換電路部分的數(shù)字地與外部其他電路的數(shù)字地通過光耦隔離,抑制外界干擾的影響,保證A/D轉(zhuǎn)換部分獨(dú)自享用一個地。

6 結(jié)束語

腦電分析是一種有效的無創(chuàng)分析手段,能夠在無人體創(chuàng)傷的情況下提供可靠的電生理功能和病理信息,有助于準(zhǔn)確找出腦內(nèi)疾病源的位置,促進(jìn)治療。而高效的采集腦電信號是保證能夠準(zhǔn)確進(jìn)行腦電分析的一個重要環(huán)節(jié)。通過對16位高速串行A/D轉(zhuǎn)換器AD977A功能、特點(diǎn)及工作原理的研究,設(shè)計(jì)了其與FPGA的接口電路,實(shí)踐證明該設(shè)計(jì)具有可靠性高,通用性強(qiáng)等優(yōu)點(diǎn),并且具有非常重要的應(yīng)用價(jià)值和良好的市場前景。該系統(tǒng)設(shè)計(jì)創(chuàng)新之處在于以FP-GA作為邏輯控制核心單元來控制模數(shù)轉(zhuǎn)換;采用全新的開發(fā)工具——Ouartus II作為開發(fā)環(huán)境,簡化了開發(fā)流程。