模擬采集部分是所有數(shù)據(jù)采集系統(tǒng)的核心。微處理器、數(shù)字信號(hào)處理器、存儲(chǔ)器、固件、軟件驅(qū)動(dòng)、操作系統(tǒng)和軟件應(yīng)用都可能構(gòu)成一個(gè)系統(tǒng)的大腦,但它們實(shí)際上還是模擬電路。要針對(duì)某種應(yīng)用建立一個(gè)有必要的速度、分辨率和精度的系統(tǒng),需要尋找模擬數(shù)據(jù)轉(zhuǎn)換器、運(yùn)放、復(fù)用器和電壓基準(zhǔn)的正確組合。

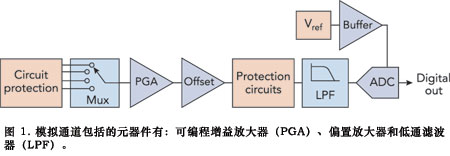

圖 1 是模數(shù)轉(zhuǎn)換器(ADC)中通過(guò)基本模擬信號(hào)的路徑。每個(gè)數(shù)據(jù)采集系統(tǒng)都要使用這種基本配置的某種形式。為每個(gè)元件所做的選擇會(huì)影響到對(duì)其他元件的選擇。

模擬信號(hào)路徑開始于輸入連接器。多數(shù)數(shù)據(jù)采集系統(tǒng)會(huì)在模擬電路前采用某種形式的電路保護(hù)。例如保險(xiǎn)絲或箝位二極管等元件可以限制進(jìn)入系統(tǒng)的電壓或電流,以保護(hù)元器件不會(huì)損壞。

數(shù)據(jù)采集系統(tǒng)很少采用單一的測(cè)量通道。數(shù)字萬(wàn)用表(DMM)一般只有一個(gè)通道,但可以用繼電器與 DMM 結(jié)合來(lái)增加通道數(shù)。數(shù)據(jù)采集系統(tǒng)(無(wú)論是插件板、USB 模塊或獨(dú)立系統(tǒng))每個(gè)通道都可能有一個(gè)專用的 ADC,或只有一個(gè) ADC,由復(fù)用器(mux)連接到多個(gè)通道。每個(gè)通道都有專用 ADC 使系統(tǒng)的所有通道可以同時(shí)采樣。

在復(fù)用器之后(如果系統(tǒng)使用的話),可編程增益放大器(PGA)對(duì)來(lái)自傳感器或其他信號(hào)源的輸入電壓進(jìn)行放大或衰減,使之最佳地適配 ADC 的輸入電壓范圍。有些系統(tǒng)可能采用第二只運(yùn)放,它為輸入信號(hào)增加了一個(gè) DC 偏置電壓。偏置電壓用于使信號(hào)偏移,使之定位于 ADC 輸入范圍的中心。因此,ADC 輸入電壓范圍就是選擇 PGA 的主要因素。

也可以使用附加的箝位電路來(lái)保護(hù) ADC。在 ADC 之前,大多數(shù)系統(tǒng)設(shè)計(jì)者都增會(huì)加一個(gè)低通抗混疊濾波器。這個(gè)濾波器用于限制信號(hào)路徑的帶寬,在 ADC 進(jìn)行信號(hào)數(shù)字化以前盡可能減少混疊的最后機(jī)會(huì)。

要成功地?cái)?shù)字化模擬信號(hào),ADC 需要一個(gè)基準(zhǔn)電壓 Vref。有些 ADC 帶有內(nèi)部基準(zhǔn),而其他則采用外接基準(zhǔn)源。

Keithley Instruments 公司的高級(jí)總工

程師 Kevin Cawley 說(shuō):“我們偏向于外接電壓基準(zhǔn)。我們認(rèn)為,外接電壓基準(zhǔn)要比內(nèi)置的更穩(wěn)定。”

United Electronic Industries(UEI)的工程經(jīng)理 Alex Ivchenko 進(jìn)一步說(shuō):“如果你用外接基準(zhǔn),就可以通過(guò)控制 ADC 基準(zhǔn)電壓來(lái)調(diào)節(jié)輸入路徑的增益。如果輸入電壓太高,就需要提供一個(gè)更高的 Vref。”

ADC 的數(shù)字輸出可以是串行方式,也可以是并行方式。串行總線能提供更好的模擬性能,因?yàn)樵谝粋€(gè)給定時(shí)間內(nèi)只有較少的線路需要改變,可以盡量減少在電源與地線上的反跳,并降低了總系統(tǒng)噪聲。但是,對(duì)于相同的位數(shù),串行接口運(yùn)行的時(shí)鐘頻率高于并行總線,因此,必須小心地發(fā)送信號(hào)以減少噪聲。

ADC 的選擇

ADC 的選擇涉及很多必須考慮的設(shè)計(jì)權(quán)衡。數(shù)據(jù)采集系統(tǒng)中的多數(shù) ADC 都采用逐次逼近型(SAR)或 Σ-Δ架構(gòu)。一般來(lái)說(shuō),SAR 器件的速度高于 Σ-Δ ADC,但 Σ-Δ 架構(gòu)有更高的分辨率。如果需要高于 18 位的分辨率,就需要 Σ-Δ 轉(zhuǎn)換器。

ADC 的采樣率與電源電壓將決定可以使用的支持電路類型。以電源電壓為例,今天的多數(shù) ADC 采用 CMOS 工藝而不是雙極工藝制造。CMOS 器件的功耗遠(yuǎn)低于雙極器件,還可以采用較低的電源電壓軌運(yùn)行。雙極器件可能需要 12V 或 15V 電壓軌,而 CMOS 器件可以采用5V、4V、3.3V、2.5V 甚至 1.8V 的單極電源。

盡管低電壓能降低功耗,但它們也壓縮了 ADC 的動(dòng)態(tài)范圍。ADC 運(yùn)行在 12V 時(shí),其動(dòng)態(tài)范圍是 0-4V 器件的六倍。因此,同樣數(shù)量的噪聲對(duì) 12V 系統(tǒng)的影響遠(yuǎn)小于一個(gè) 4V 系統(tǒng)。所以,必須使進(jìn)入 ADC 的噪聲低于 1 個(gè)最低有效位(LSB)。ADC 前的運(yùn)放噪聲級(jí)要與 1 LSB 動(dòng)態(tài)范圍相一致。這意味著24 位 ADC 的噪聲要比 16 位ADC 更低。

Cawley 稱,為獲得更好的動(dòng)態(tài)范圍,應(yīng)該盡可能使高電平信號(hào)遠(yuǎn)離模擬通道。他指出,Keithley 的 DMM 在 10V 范圍內(nèi)可以提供最佳的精度,此時(shí)對(duì)進(jìn)入的信號(hào)既不需要放大也無(wú)需衰減。

設(shè)計(jì)者的工作

由于高電壓軌可提供更好的動(dòng)態(tài)范圍,很多工業(yè)數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)者要求自己的運(yùn)放和數(shù)據(jù)轉(zhuǎn)換器采用這類電壓軌。于是,ADC 制造商開發(fā)出了工作在 16V 電壓軌的 CMOS 數(shù)據(jù)轉(zhuǎn)換器。Analog Devices 公司高級(jí)現(xiàn)場(chǎng)應(yīng)用工程師 Chris Hyde 指出,這些器件可以處理高達(dá) 15V 的傳感器輸入。

對(duì)低動(dòng)態(tài)范圍的其他補(bǔ)償是盡可能早地對(duì)傳感器信號(hào)進(jìn)行數(shù)字化。UEI 的 Ivchenko 說(shuō):“高速 ADC 價(jià)格已經(jīng)下降到了一個(gè)讓過(guò)采樣更有意義的點(diǎn)位。”

使用了過(guò)采樣,就可以用數(shù)字濾波器降低噪聲。過(guò)采樣與濾波器越多,則噪聲抑制能力越好,但系統(tǒng)會(huì)更慢。Ivchenko 指出,采用 22n 過(guò)采樣及使用一個(gè)數(shù)字均化濾波器會(huì)提高噪聲性能。下表列出了給定位數(shù)下需要多少過(guò)采樣才能提高噪聲性能的情形。

對(duì)給定位數(shù)提高噪聲性能需要的過(guò)采樣值

Ivchenko 在 ADC 后加了一個(gè)“磚墻式”(120 dB/倍頻程)數(shù)字有限脈沖響應(yīng)(FIR)濾波器,以降低噪聲并提取出感興趣的頻譜。然后,他提取一部分?jǐn)?shù)據(jù)或作一個(gè)移動(dòng)平均,使采樣速率能為應(yīng)用所接受。

低壓 ADC 與運(yùn)放要求有足夠的供電電流,才能在數(shù)據(jù)轉(zhuǎn)換期間保持信號(hào)穩(wěn)定。Hyde 說(shuō):“設(shè)計(jì)者挑選的運(yùn)放和電壓基準(zhǔn)經(jīng)常沒(méi)有足夠的驅(qū)動(dòng)能力。一個(gè)電壓基準(zhǔn)可能同時(shí)需要流出和流入電流。”一個(gè) ADC 可能有一個(gè)動(dòng)態(tài)輸入阻抗,而且可能需要一個(gè)低阻抗信號(hào)源作充分的耦合,才能維持基準(zhǔn)電壓電平。

National Instruments 的模擬設(shè)計(jì)工程師 Luis Orozco 稱:“SAR 轉(zhuǎn)換器需要一種很低的輸出阻抗源來(lái)保持輸入信號(hào)在轉(zhuǎn)換期間不會(huì)變化。由于 SAR ADC 一般對(duì)其電源表現(xiàn)為高動(dòng)態(tài)負(fù)載,我們要小心地旁路所有器件。”他指出,給一個(gè) ADC 配用正確的運(yùn)放非常重要。

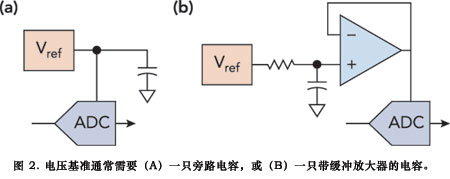

Orozco 說(shuō):“一個(gè)運(yùn)放要具備實(shí)現(xiàn)特定 ADC 規(guī)格的性能,它消耗的電流要比 ADC 自身多數(shù)倍。”ADC 的基準(zhǔn)輸入與信號(hào)輸入表現(xiàn)類似。低功耗器件(如電壓基準(zhǔn))可能需要電容器或緩沖器,從而在 ADC 對(duì)基準(zhǔn)采樣時(shí)保持輸出的穩(wěn)定電平。

Ivchenko 補(bǔ)充說(shuō):“不僅如此,還應(yīng)采用低等效串聯(lián)電阻(ESR)的旁路電容。可能的話盡量用 X7R 陶瓷電容,而不用鉭電容。電容器必須有足夠快的充放電速度,才能在轉(zhuǎn)換期間為 ADC 提供足夠的峰值電流。”高 ESR 會(huì)增加電容器的充放電時(shí)間。

圖 2 給出了提供充足電流的兩種方法。在圖 2a 中,一只電容器存儲(chǔ)能量,當(dāng) ADC 需要更多電流來(lái)保持基準(zhǔn)電壓穩(wěn)定時(shí),電容為其供電。一般 22?F 的電容就夠用了,但要查看ADC 數(shù)據(jù)手冊(cè)來(lái)確認(rèn)這一點(diǎn)。在圖 2b 中,運(yùn)放用于 ADC 電壓基準(zhǔn)的緩沖。運(yùn)放給電壓基準(zhǔn)提供了高阻抗輸入,同時(shí)其低阻抗輸出能為 ADC 提供充足的電流。雖然運(yùn)放方案更講究,但它為 Vref 增加了一個(gè)偏置電壓,這會(huì)增加系統(tǒng)噪聲、功耗,而且成本也更高。

差分輸入

為改善動(dòng)態(tài)范圍和噪聲抑制能力,應(yīng)在數(shù)據(jù)采集系統(tǒng)中采用差分輸入。使用差分輸入時(shí)(與單端輸入相反),兩根信號(hào)線上的任何信號(hào)都被共模抑制(CMR)放大器或 ADC 排除掉了。如果傳感器輸出是單端的,可使用一種單端-差分轉(zhuǎn)換驅(qū)動(dòng)電路(圖 3)。數(shù)據(jù)采集系統(tǒng)可以設(shè)計(jì)為使用單端輸入或差分輸入。

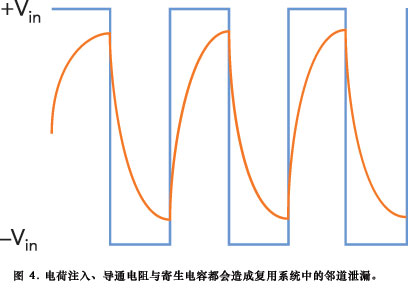

很多數(shù)據(jù)采集系統(tǒng)都用一個(gè)復(fù)用器來(lái)增加通道。復(fù)用器中的電阻與電容會(huì)影響信號(hào)的完整性。例如,來(lái)自復(fù)用器的電荷注入會(huì)將 DC 信號(hào)轉(zhuǎn)變?yōu)?AC 信號(hào)。導(dǎo)通電阻(Ron)與寄生電容相結(jié)合,就形成了一個(gè)低通濾波器,它有一個(gè) RC 時(shí)間常數(shù)。圖 4 表示如果時(shí)間常數(shù)相對(duì)于采樣時(shí)間過(guò)長(zhǎng)將會(huì)發(fā)生的事情。

這個(gè)系統(tǒng)錯(cuò)誤可以很容易被測(cè)試。將一個(gè)復(fù)用數(shù)據(jù)采集系統(tǒng)中的兩個(gè)相鄰?fù)ǖ溃ㄈ缤ǖ?0 和 1)連接到接近系統(tǒng)輸入極限的 DC 電壓上,如 +10V 和 -10V。接下來(lái),在兩個(gè)輸入通道之間進(jìn)行交替采樣。開始對(duì)每個(gè)通道進(jìn)行幾次采樣,并逐漸轉(zhuǎn)為每通道一次采樣,然后切換通道。

如果時(shí)間常數(shù)快于采樣速率,則應(yīng)看到二分之一采樣速率的一個(gè)方波。但如果時(shí)間常數(shù)過(guò)長(zhǎng),則所得到的是一個(gè)類似的三角波,因?yàn)橥ǖ乐g有電荷注入。

Analog Devices 公司的 Hyde 說(shuō):“Ron 應(yīng)不大于幾歐姆。數(shù)百歐的導(dǎo)通電阻對(duì)今天的多數(shù)數(shù)據(jù)采集應(yīng)用而言太大了。”而 National Instruments 的 Orozco 主張,數(shù)百歐并不太大,因?yàn)樯嫌芜\(yùn)放有高輸入阻抗。

Hyde 還指出,復(fù)用器的導(dǎo)通電阻會(huì)根據(jù)系統(tǒng)輸入信號(hào)的幅度而變化。如果將通道從一個(gè)電壓軌變到另一個(gè)電壓軌,就需要了解通道的 RC 時(shí)間常數(shù)。當(dāng) Ron 隨電壓變化時(shí),通道電容會(huì)產(chǎn)生一個(gè)隨頻率變化的阻抗。這些阻抗與電容一起構(gòu)成了一個(gè)可變的低通濾波器,并造成失真。

Hyde 說(shuō):“通道必須落在 ADC 精度極限內(nèi),以防止電荷導(dǎo)致的錯(cuò)誤。”新復(fù)用器的電容小于較老型號(hào),他補(bǔ)充說(shuō)。

技術(shù)數(shù)據(jù)

在設(shè)計(jì)數(shù)據(jù)采集系統(tǒng)時(shí),當(dāng)然要依賴于 ADC、運(yùn)放和電壓基準(zhǔn)的數(shù)據(jù)手冊(cè)。元器件制造商也會(huì)為自己的元件提供其他有價(jià)值的資源,如參考設(shè)計(jì)板(圖 5)。通常情況下,可以購(gòu)買一塊參考設(shè)計(jì)板來(lái)評(píng)估元件,然后再將它們?cè)O(shè)計(jì)到自己的系統(tǒng)里。

數(shù)據(jù)手冊(cè)也提供了設(shè)計(jì)與布局信息,但 Keithley 的 Cawley 發(fā)現(xiàn),數(shù)據(jù)手冊(cè)上的信息和參考設(shè)計(jì)板可能不一致。在設(shè)計(jì)一個(gè) 500 k 采樣/秒、18 位的數(shù)據(jù)采集系統(tǒng)時(shí),Cawley 使用數(shù)據(jù)手冊(cè)中的設(shè)計(jì)信息,不過(guò)發(fā)現(xiàn) ADC 產(chǎn)生的噪聲在 3 與 7 LSB 之間(5 ?V/LSB)。他說(shuō):“當(dāng)我轉(zhuǎn)用參考設(shè)計(jì)推薦的布局時(shí),噪聲跌到了 1 LSB 內(nèi)。該參考設(shè)計(jì)在 QFP 器件下用了四層接地。用 9 個(gè)通孔連接接地層,但數(shù)據(jù)手冊(cè)用了一根從 ADC 到一只旁路電容的走線,而沒(méi)有用接地層。”

模擬 IC 制造商為 ADC 的設(shè)計(jì)提供了豐富的技術(shù)信息,無(wú)需支付費(fèi)用就可以找到應(yīng)用說(shuō)明、數(shù)據(jù)手冊(cè)、在線研討會(huì)、技術(shù)論文,以及仿真軟件等。