摘 要: FPGA" title="FPGA">FPGA可以通過串行接口進行配置。本文對傳統(tǒng)的配置方法進行了研究,并從更新配置文件的方法入手,提出了利用處理機通過網絡更新的方法,給出了一個用CPLD" title="CPLD">CPLD和Flash" title="Flash">Flash對FPGA進行配置的應用實例。

關鍵詞: 現場可編程門陣列 復雜可編程邏輯器件 電子設計自動化 VHDL語言

電子設計自動化EDA(Electronic Design Automation)是指以計算機為工作平臺,以EDA軟件為開發(fā)環(huán)境,以硬件描述語言為設計語言,以可編程邏輯器件PLD為實驗載體(包括CPLD、FPGA、EPLD等),以集成電路芯片為目標器件的電子產品自動化設計過程。該過程目前已廣泛應用于電子電路與系統(tǒng)的設計和產品的開發(fā)中,逐漸取代了傳統(tǒng)的手工硬件電路設計方式。設計的系統(tǒng)具有體積小、重量輕、功耗小、速度快、價格低、可靠性高、設計周期短等優(yōu)點。一個功能完備的EDA設計軟件加上一片普通功能的可編程邏輯芯片就可以構成以前需幾百個集成電路才能構成的電子系統(tǒng)[1]。

目前常用的可編程邏輯器件有CPLD(Complex Programmable Logic Device,復雜可編程邏輯器件)和FPGA(Field Programmable Gate Array,現場可編程門陣列)。常用的EDA軟件包括VHDL、Verilog HDL、ABEL等硬件描述語言。其中,VHDL作為IEEE的工業(yè)標準硬件描述語言,受到眾多EDA工具廠家的支持,在電子工程領域,已成為事實上的通用硬件描述語言。

Xilinx公司和Altera公司的FPGA可編程部分的物理實現方式為RAM。它最大的優(yōu)點是可以多次重復編程,缺點是易失性。因此每次上電后,處理機都需要將用戶設計的FPGA配置文件從外部存儲器中下載到FPGA中。從外部存儲器將FPGA配置文件下載更新的方式有以下三種:

(1)JTAG口下載方式

將配置文件放到一臺主機中,主機通過專用線與單板上的JTAG口硬件相連接。在這種方式下每次下載都需要硬件操作,因此只適用于開發(fā)、調試階段,設備在現場工作時就不能再使用這種方式。

(2)片外串行PROM下載方式

在每片FPGA周圍放置一片或幾片(由FPGA容量決定)串行PROM,在系統(tǒng)上電時,自動將FPGA配置文件從PROM下載到FPGA中。此方式也是Xilinx、Altera等公司重點介紹的方式,適用于比較穩(wěn)定的系統(tǒng)。但隨著FPGA芯片密度的增加,串行PROM已不能適應大容量、高密度的FPGA的配置。而大容量的并行PROM所要求的尋址方式又不能直接與FPGA接口。當系統(tǒng)中的FPGA配置文件需要升級更新時,必須將機箱打開,通過JTAG口首先將PROM中的配置文件更新,然后再重新啟動系統(tǒng),將更新后的配置文件從PROM下載到FPGA中,這樣才能完成一次FPGA配置文件的更新。

以上兩種方案都存在必須進行硬件操作(將機箱打開,使用主機通過JTAG口)的缺點,在主機上必須安裝專業(yè)軟件才能完成FPGA配置文件的更新。

(3)處理機控制Flash下載方式

本文根據Xilinx、Altera公司手冊及以前的工作經驗,提出和完成了一種新的FPGA配置文件下載更新的方式。這種方式適用于支持網絡通信的系統(tǒng)中。在每次系統(tǒng)啟動時,由處理機從Flash中讀出FPGA配置文件,再下載到FPGA中。即當需要升級更新FPGA配置文件時,通過網絡將配置文件發(fā)送給處理機,由處理機更新系統(tǒng)中的Flash。當Flash內容更新后,再由處理機控制將配置文件自動下載到FPGA中。這樣在不需要任何硬件動作和專業(yè)軟件的情況下,只需要進行常規(guī)軟件操作就可以更新FPGA的配置文件。但由于Flash是并行數據線,需要通過一片CPLD將從Flash中讀來的數據轉換成串行數據輸出到FPGA。

1 FPGA下載配置模式

FPGA配置文件的下載模式有五種:主串模式(master serial)、從串模式(slave serial)、主并模式(master selectMAP)、從并模式(slave selectMAP)及JTAG模式。其中,JTAG模式在開發(fā)調試階段使用。為了便于開發(fā)設計階段的調試,本核心路由器設計將JTAG口直接做在信號處理板上。

主、從模式的最大區(qū)別在于:主模式的下載同步時鐘(CCLK)由FPGA提供;從模式的下載同步時鐘(CCLK)由外部時鐘源或者外部控制信號提供。主模式對下載時序的要求比從模式嚴格得多。因此從處理機易于控制下載過程的角度考慮,選擇使用從串模式或從并模式較為合適。本設計采用從串模式進行FPGA配置。從串模式引腳說明如表1所示。

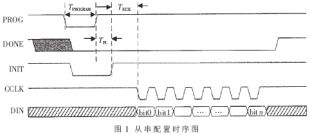

從串配置時序圖如圖1所示。TPROGRAM是配置邏輯的復位時間,對Xilinx VIRTEXE和VIRTEX2系列,最小應大于300ns。TPL為復位延遲時間,表明配置邏輯復位的延續(xù)。對VIRTEXE系列來說,當復位信號PROG變?yōu)楦唠娖綍r,INIT立即變?yōu)楦唠娖剑渲眠壿嬀涂梢越邮张渲脭祿鳎欢鴮τ赩IRTEX2系列,TPL最小有500ns的延遲。TICCK為配置時鐘CCLK的輸出延遲。

當PROG有效(對配置邏輯進行復位)時,FPGA將置低INIT和DONE;PROG變?yōu)楦唠娖綍r,INIT將延遲一段時間用于表明復位狀態(tài)的延續(xù),繼續(xù)置低INIT可以延遲配置的進行。當FPGA正在接收配置數據時,INIT變低,表明CRC校驗錯。當配置完所有的數據時,若配置正確,DONE將會變高。此后FPGA開始啟動序列,繼續(xù)置低DONE可以延遲啟動的進行[2]。

2 具體設計

國家數字交換系統(tǒng)工程技術研究中心承擔的國家863項目高性能IPv6核心路由器采用一片Intel E28F128J3A150 16位Flash作為BootFlash對PowerPC860(MPC860)處理機進行加電配置下載更新的方案,其多余的存儲空間完全可以存放下FPGA所需的配置文件。加電復位、系統(tǒng)啟動后,由處理機與一片 Xilinx XC95288XL CPLD配合,控制FPGA配置文件從Flash下載到FPGA中,完成對FPGA的配置。860處理機支持網絡功能,當配置文件需要更新時,可通過網絡將新的配置文件發(fā)送到處理機,然后再由處理機更新系統(tǒng)中的Flash。采用XC95288 CPLD配置FPGA的具體電路設計結構如圖2所示。

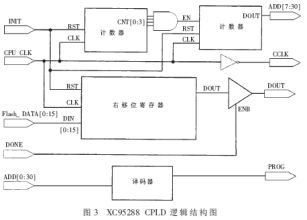

圖2中,CPLD主要功能是把從Flash中讀出的數據轉換成串行輸出,然后再將地址遞增。CCLK信號由CPU時鐘產生。PROG信號則由CPU輸出的地址數據經譯碼模塊產生。XC95288C PLD邏輯結構如圖3所示。

下面分別介紹各功能模塊的具體實現:

(1)數據轉換成串行輸出功能模塊:使用了一個右移寄存器。從16位Flash來的并行數據DIN[0:15]加載到移位寄存器后,依次從DOUT串行輸出到FPGA中。

(2)地址遞增功能模塊:此功能由兩個計數器完成。由于Flash是16位并行數據端口,因此第一個計數器功能是逢16進1,第二個計數器功能是 Flash地址遞增。當移位寄存器的16位數據都輸出到FPGA中后,第一個計數器輸出端口CNT[0:3]都為“1”,經過“與門”邏輯使得第二個計數器加1。Intel E28F128J3A150 Flash為16MB,共需要25根地址線。由于Flash是16位的,因此ADD[31]不連接。所以第二個計數器和地址線ADD[7:30]相連,以完成Flash地址的遞增。

(3)CCLK信號產生模塊:CPU來的時鐘信號將數據信號DOUT輸出,經一個“非門”邏輯延遲半個周期后產生CCLK,CCLK再將DOUT上的數據送到FPGA中。這樣將讀寫DOUT數據的時刻叉開,避免了沖突。

(4)PROG信號產生模塊:當需要下載FPGA程序時,由CPU產生一個地址信號ADD[0:30],經譯碼器譯碼產生PROG控制信號。此地址由用戶自行設定。

以上模塊均采用VHDL語言描述。數據轉換成串行輸出功能模塊是核心部分,它可實現并行數據串行輸出。

本文介紹了通過處理機用CPLD和Flash實現FPGA配置文件下載更新的方法。與傳統(tǒng)的JTAG或PROM串行下載配置方法相比,此方法具有更新配置文件靈活方便、易于操作、適用于大容量FPGA下載的特點。采用此方法可以不用打開機箱即可隨時更新FPGA配置程序,特別適用于需要不斷更新的系統(tǒng)設計中,具有較為廣闊的應用前景。

參考文獻

1 李冬梅. PLD器件與EDA技術.北京廣播學院出版社, 2000

2 Field Programmable Gate Array.Xilinx DS003-1(v2.5), April 2 2001