摘 要: 異步FIFO是一種不同時鐘域之間傳遞數(shù)據(jù)的常用方法。本文提出一種新穎的異步FIFO設(shè)計方案。此方案避免了使用大量的同步寄存器,減小了芯片面積并且提高了工作頻率" title="工作頻率">工作頻率。DC綜合的結(jié)果表明,用此方法設(shè)計的FIFO性能有了顯著提高。

關(guān)鍵詞: 多時鐘域 亞穩(wěn)態(tài) 異步 FIFO Verilog HDL

在現(xiàn)代IC設(shè)計中,特別是在模塊與外圍芯片的通信設(shè)計中,多時鐘域的情況不可避免。當(dāng)數(shù)據(jù)從一個時鐘域傳遞到另一個域,并且目標(biāo)時鐘域與源時鐘域不相關(guān)時,這些域中的動作是不相關(guān)的,從而消除了同步操作的可能性,并使系統(tǒng)重復(fù)地進入亞穩(wěn)定狀態(tài)[1]。在有大量的數(shù)據(jù)需要進行跨時鐘域傳輸且對數(shù)據(jù)傳輸速度要求比較高的場合,異步FIFO是一種簡單、快捷的解決方案。

異步FIFO用一種時鐘寫入數(shù)據(jù),而用另外一種時鐘讀出數(shù)據(jù)。讀寫指針的變化動作由不同的時鐘產(chǎn)生。因此,對FIFO空或滿的判斷是跨時鐘域的。如何根據(jù)異步的指針信號產(chǎn)生正確的空、滿標(biāo)志,是異步FIFO設(shè)計成敗的關(guān)鍵。本文提出一種新穎的異步FIFO設(shè)計方案,它通過先比較讀寫地址并結(jié)合象限檢測法產(chǎn)生異步的空/滿標(biāo)志,再把異步的空/滿標(biāo)志同步到相應(yīng)的時鐘域。通過仿真驗證" title="仿真驗證">仿真驗證,該方法是穩(wěn)定有效的。

1 異步信號傳輸問題的分析

在一個ASIC或FPGA庫中,每種觸發(fā)器都有時序要求。對于使用上升沿" title="上升沿">上升沿觸發(fā)的觸發(fā)器來說,建立時間(Setup Time)是在時鐘上升沿到來之前,觸發(fā)器數(shù)據(jù)保持穩(wěn)定的最小時間;而保持時間(Hold Time)是在時鐘上升沿到來之后,觸發(fā)器數(shù)據(jù)還應(yīng)該保持的最小時間[2]。如圖1所示,在時鐘上升沿前后的這個窗口內(nèi)數(shù)據(jù)應(yīng)該保持不變,否則會使觸發(fā)器工作在一個不確定的狀態(tài),即亞穩(wěn)態(tài)。當(dāng)觸發(fā)器處于亞穩(wěn)態(tài),且處于亞穩(wěn)態(tài)的時間超過了一個時鐘周期時,這種不確定的狀態(tài)將會影響到下一級的觸發(fā)器,最終導(dǎo)致連鎖反應(yīng),從而使整個系統(tǒng)功能失常。當(dāng)一個信號跨越某個時鐘域時,對新時鐘域的電路來說它就是一個異步信號。由于異步信號之間的時序是毫無關(guān)系的,因此必然存在Setup Time/Hold Time沖突。為了避免亞穩(wěn)態(tài)問題,采用如圖2所示的雙鎖存器" title="鎖存器">鎖存器法[3],即在一個信號進入另一個時鐘域前,將該信號用兩個鎖存器連續(xù)鎖存兩次,最后得到的采樣結(jié)果就可以消除亞穩(wěn)態(tài)。

?

消除亞穩(wěn)態(tài)只是保證了信號電平的穩(wěn)定,要在不同時鐘域中準(zhǔn)確傳輸數(shù)據(jù)還需要一個接口電路。異步FIFO就是一種不同時鐘域之間傳遞多位數(shù)據(jù)的常用方法。

2 異步FIFO設(shè)計

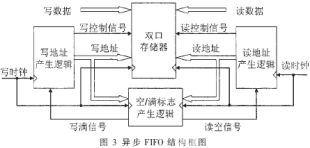

異步FIFO是一種先進先出電路,用在需要實時數(shù)據(jù)接口的部分,用來存儲、緩沖在兩個異步時鐘之間的數(shù)據(jù)傳輸。主要由雙口存儲器、讀地址產(chǎn)生邏輯、寫地址產(chǎn)生邏輯、空/滿標(biāo)志產(chǎn)生邏輯四部分構(gòu)成。圖3是一種常用的異步FIFO設(shè)計方案,其中,讀地址(rptr)和空標(biāo)志(rempty)由讀時鐘(rclk)產(chǎn)生,而寫地址(wptr)和滿標(biāo)志(wfull)由寫時鐘(wclk)產(chǎn)生。把寫地址與讀地址相互比較以產(chǎn)生空/滿標(biāo)志。由于讀寫地址的變化由不同的時鐘產(chǎn)生,所以對FIFO空或滿的判斷是跨時鐘域的。如何避免異步傳輸帶來的亞穩(wěn)態(tài)以及正確地產(chǎn)生空/滿標(biāo)志是設(shè)計異步FIFO的難點。

2.1 讀寫地址產(chǎn)生邏輯

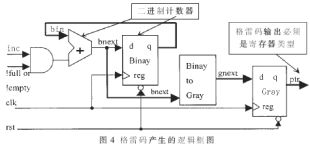

讀寫地址線一般有多位,如果在不同的時鐘域內(nèi)直接同步二進制碼的地址指針,則有可能產(chǎn)生亞穩(wěn)態(tài)。例如,讀指針從011變化到100時,所有位都要變化,讀指針的每一位在讀時鐘的作用下,跳變不一致,即產(chǎn)生毛刺。如果寫時鐘恰好在讀指針的變化時刻采樣,得到的采樣信號可能是000~111中的任何一個,從而導(dǎo)致空/滿信號判斷錯誤。由實踐可知,同步多個異步輸入信號出現(xiàn)亞穩(wěn)態(tài)的概率遠(yuǎn)遠(yuǎn)大于同步一個異步信號的概率[3]。解決這一問題的有效方法是采用格雷碼" title="格雷碼">格雷碼。格雷碼的主要特點是相鄰的兩個編碼之間只有一位變化。圖4是格雷碼產(chǎn)生的邏輯框圖。在讀使能或?qū)懯鼓苄盘栍行А⒉⑶铱?滿標(biāo)志無效的情況下,讀寫指針開始累加,進行FIFO讀或?qū)懖僮鳌6M制碼與格雷碼的轉(zhuǎn)換是一個“異或”運算:gnext=(bnext>>1)^bnext。格雷碼gnext經(jīng)寄存器輸出格雷碼指針ptr。這種方法采用了兩組寄存器,雖然面積較大,但是有助于提高系統(tǒng)的工作頻率。

2.2 空/滿標(biāo)志產(chǎn)生邏輯

正確地產(chǎn)生空/滿標(biāo)志是設(shè)計任何類型FIFO的關(guān)鍵點。空/滿標(biāo)志產(chǎn)生的原則是:寫滿而不溢出,能讀空而不多讀。傳統(tǒng)的異步FIFO把讀寫地址信號同步后再進行同步比較以產(chǎn)生空滿標(biāo)志,由于讀寫地址的每一位都需要兩級同步電路,大量使用寄存器必然要占用很大的面積。這種方法不適合設(shè)計大容量的FIFO。當(dāng)讀、寫指針相等也就是指向同一個內(nèi)存位置時,F(xiàn)IFO可能處于滿或空兩種狀態(tài),必須區(qū)分FIFO是處于空狀態(tài)還是滿狀態(tài)。傳統(tǒng)的做法是把讀、寫地址寄存器擴展一位,最高位設(shè)為狀態(tài)位,其余低位作為地址位。當(dāng)讀寫指針的地址位和狀態(tài)位全部吻合時,F(xiàn)IFO處于空狀態(tài);當(dāng)讀寫指針的地址位相同而狀態(tài)位相反時, FIFO處于滿狀態(tài)。傳統(tǒng)的異步FIFO工作頻率低、面積大。下面將介紹一種產(chǎn)生空/滿標(biāo)志的新方法。

通過異步比較讀寫指針ptr以及讀寫指針的最高兩位進行判斷,產(chǎn)生兩個異步的空/滿標(biāo)志信號(aempty/afull)送入讀寫模塊進行同步,最后向外部輸出兩個同步的空/滿信號(rempty/wfull)。空/滿信號的產(chǎn)生過程:如圖5所示,對于深度是2n的異步FIFO,按照其讀指針rptr[n:0]和寫指針wptr[n:0]最高兩位的不同取值,可把地址空間分為四個像限[4]。當(dāng)寫指針比讀指針落后一個像限時,意味著寫指針即將從后面追上讀指針,F(xiàn)IFO處于“可能將滿”狀態(tài),在圖6所示的空滿信號產(chǎn)生邏輯框圖中聲明一個direction信號并把它置為1;當(dāng)讀寫指針完全相等并且direction為1時,則FIFO處于滿狀態(tài)并且把滿信號afull置為0(低電平有效);當(dāng)讀指針比寫指針落后一個像限時,意味著讀指針即將追上寫指針,F(xiàn)IFO處于“可能將空”狀態(tài),或者當(dāng)寫操作復(fù)位信號wrst有效時,再進行讀操作,則FIFO也處于“可能將空”狀態(tài),此時把direction信號置為0;當(dāng)讀寫指針完全相等并且direction為0時,則FIFO處于空狀態(tài),空標(biāo)志信號aempty置為0。

?

讀寫地址異步相比較產(chǎn)生低電平有效的空/滿標(biāo)志,其中異步滿信號(afull)要同步到寫時鐘域(wclk),異步空信號(aempty)要同步到讀時鐘域(rclk),以消除亞穩(wěn)態(tài)的影響,并向外界輸出同步的空/滿信號。下面以滿信號(wfull)為例說明同步信號的產(chǎn)生過程:滿信號afull是因為寫地址追上了讀地址并比讀地址多循環(huán)一次所產(chǎn)生,此時不能再向FIFO中寫入數(shù)據(jù),否則會造成FIFO寫溢出。由于寫地址(wptr)的變化產(chǎn)生FIFO滿標(biāo)志afull,即afull的下降沿與wptr同屬于寫時鐘域。當(dāng)讀地址增加時,表明已經(jīng)從FIFO中讀走了一個數(shù)據(jù),afull由有效的低電平變?yōu)闊o效的高電平,即afull的上升沿與rptr同屬于讀時鐘域。可見,afull由高變低與寫時鐘(wclk)同步,而由低變高則與讀時鐘(rclk)同步。由于滿標(biāo)志afull只影響FIFO的寫入,故將其同步到寫時鐘域。如圖6所示,采用雙鎖存器法將afull過渡到寫時鐘域,最后得到的滿信號wfull就屬于寫時鐘域。同理可以得到空標(biāo)志信號rempty。用Verilog代碼實現(xiàn)如下:

wire dirset=~((wptr[n]^rptr[n-1]) & ~(wptr[n-1]^rptr[n]));

wire dirrst=~((~(wptr[n]^rptr[n-1]) & (wptr[n-1]^rptr[n])) |~wrst);

always @(posedge high or negedge dirset or negedge dirrst)

if (!dirrst) direction <= 1′b0;

else if (!dirset) direction <= 1′b1;

else direction <= high;

assign aempty=~((wptr==rptr) && !direction);

assign afull=~((wptr==rptr) && direction);

always @(posedge rclk or negedge aempty)

if (!aempty) {rempty,rempty2} <= 2′b11;

else {rempty,rempty2} <= {rempty2,~aempty};

always @(posedge wclk or negedge afull)

if (!afull) {wfull,wfull2} <= 2′b11;

else {wfull,wfull2} <= {wfull2,~afull };

異步比較法的關(guān)鍵是用異步比較結(jié)果的信號的下降沿作為最終比較結(jié)果的復(fù)位信號,而其上升沿則用傳統(tǒng)的雙鎖存器法進行同步[5]。最終得到的信號的上升沿與下降沿都屬于同一個時鐘域。與傳統(tǒng)的先將地址信號同步再進行同步比較的方法相比,異步比較法避免了使用大量的同步寄存器,而效率則更高,實現(xiàn)也更簡單。

2.3 保守的空/滿標(biāo)志

設(shè)計中FIFO空/滿標(biāo)志的設(shè)置是保守的,即FIFO空/滿標(biāo)志的置位是立即有效的,而其失效則是在一段時間之后。例如一旦讀指針追上寫指針,就會立即聲明一個低電平有效的異步空信號aempty。此信號會立即把圖6所示的set觸發(fā)器置位,使觸發(fā)器輸出為1,即向外部輸出同步的空信號rempty,并且保證了FIFO一旦為空,讀指針就不增加,避免了FIFO的讀溢出。當(dāng)寫地址增加時,表明FIFO已經(jīng)非空,空標(biāo)志aempty由低變高,此時可以進行安全的讀操作。aempty信號的失效與寫時鐘同步。空信號rempty是在讀時鐘域中同步aempty信號得到的。由于同步器使用了兩個觸發(fā)器,因此空信號rempty的失效要經(jīng)過至少兩個時鐘周期的延遲。所以,空信號的聲明是及時的,而空信號的失效是保守的。也就是說,雖然FIFO已經(jīng)非空了,但是空信號rempty要經(jīng)過幾個周期的延遲才能變?yōu)闊o效。滿信號也有類似的情況。

雖然空/滿標(biāo)志的設(shè)置是保守的,但這并不影響FIFO功能的正確性,經(jīng)驗證保守的空/滿標(biāo)志能夠滿足FIFO的設(shè)計要求。

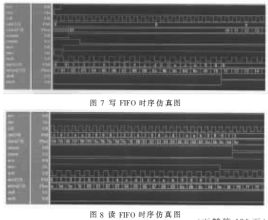

3 仿真驗證和綜合

根據(jù)以上分析,以深度為16、數(shù)據(jù)寬度為8位的異步FIFO為例,用Verilog HDL編寫了各個模塊,并采用Synopsys公司的仿真工具VCS進行了仿真驗證。設(shè)寫時鐘(wclk)周期為100MHz,讀時鐘(rclk)周期為133MHz,F(xiàn)IFO寫、讀時序仿真結(jié)果分別如圖7、圖8所示。當(dāng)FIFO寫滿時,滿標(biāo)志wfull馬上由0變1,禁止寫數(shù)據(jù)并且寫地址也不再增加,F(xiàn)IFO只讀不寫;當(dāng)FIFO讀空時,空標(biāo)志rempty馬上由0變1,禁止讀數(shù)據(jù)并且讀地址也不再增加,F(xiàn)IFO只寫不讀。空/滿信號的變化情況滿足設(shè)計要求。

仿真驗證通過后,采用Synopsys公司的Design Compiler工具進行綜合。把采用異步比較法設(shè)計的FIFO與傳統(tǒng)的先將地址信號同步再進行比較設(shè)計的FIFO相比較,在中芯國際0.35μm庫上DC綜合結(jié)果如表1所示。可見相對于傳統(tǒng)的異步FIFO,改進后的異步FIFO電路速度快、面積小,從而降低了功耗,提高了系統(tǒng)的穩(wěn)定性。

為了解決數(shù)據(jù)在不同時鐘域間傳遞所產(chǎn)生的亞穩(wěn)態(tài)問題,本文討論了一種新穎的異步FIFO設(shè)計方案。采用Verilog HDL以及由頂向下的模塊設(shè)計方法實現(xiàn)了這種方案。經(jīng)驗證該方案能安全地實現(xiàn)數(shù)據(jù)跨時鐘域的傳遞,并且性能比傳統(tǒng)方案有了明顯的改善。

參考文獻(xiàn)

1 Ciletti MD. Advanced digital design with the verilog HDL[M].影印版.北京:電子工業(yè)出版社,2004:1l5~ll9

2 朱永峰,陸生禮,茆邦琴.SoC設(shè)計中的多時鐘域處理[J].電子工程師,2003;(11):60~61

3 Cummings C E, Alfke P. Simulation and synthesis techniques for asynchronous FIFO design with asynchronous pointer comparisons [Z]. SNUG, 2002;1~18

4 Cummings C E. Synthesis and scripting techniques for designing multi-asynchronous clock designs[Z]. SNUG,2001:1~26

5 楊宗凱.數(shù)字專用集成電路的設(shè)計與驗證[M].北京:電子工業(yè)出版社,2004:214~225