隨著手機與其他便攜式電子設備變得日益先進,處于工作與待機狀態(tài)的系統(tǒng)消耗的電量也越來越大。因此,便攜式設備的電源管理設計在核心電壓、能量管理以及電池使用壽命等方面面臨著新的挑戰(zhàn)。

硬件設計人員已經(jīng)開始采用先進的高集成度電源管理器件,其具備核心電壓縮放及各種穩(wěn)壓器,可為其他軌提供電力(如存儲器、I/O等)。不過這些復雜的解決方案不一定能為系統(tǒng)設計人員提供足夠的靈活性。

本文將在TI第一代高頻降壓轉(zhuǎn)換器的基礎上,概括性地介紹解決動態(tài)電壓管理問題的一種創(chuàng)新方法。

系統(tǒng)概覽

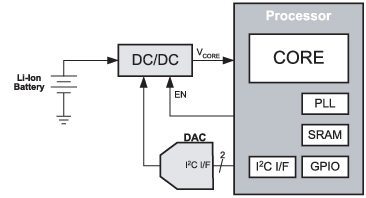

針對便攜式應用的現(xiàn)代處理器大部分都有著集成的I2C接口,連接至外部電源管理單元。(圖1)顯示了生成自適應核心電源的可選解決方案。處理器核心消耗的功率與工作頻率以及VCORE2成正比。

圖1,自適應電壓縮放系統(tǒng)概覽

基于 TPS62300 (3MHz同步降壓轉(zhuǎn)換器)和 DAC6571(10位數(shù)模轉(zhuǎn)換器)的雙芯片解決方案將高準確度和超小電壓步進結合在了一起。

根據(jù)處理器的工作頻率,核心電壓可非常準確地動態(tài)調(diào)節(jié)至較低限值,從而最小化功耗。使用該原則不僅可降低活動模式下的功耗,還可通過減少深度睡眠模式下的漏電流來延長待機時間。

核心電壓的中心

德州儀器(TI)近期發(fā)布了TPS62300,它是新一代高頻降壓轉(zhuǎn)換器的旗艦產(chǎn)品,工作在3MHz的交換頻率上。先進的求和比較器電壓模式控制拓撲提升了穩(wěn)壓性能的新層次。最佳的瞬態(tài)響應和輸出電壓準確度可滿足現(xiàn)代核心所要求的最嚴格電壓規(guī)范。

TPS62300 可與低至 1.0uH的電感以及低至4.7礔的輸出電容共同工作,這就可以使用微型低成本的芯片電感。該器件還采用芯片級小型封裝(2mm x 1mm x 0.65mm),從而在小巧外觀解決方案的尺寸成為關鍵因素時,能夠滿足移動電話制造商的需求。

方便的動態(tài)電壓縮放

圖2顯示了簡化的TPS62300塊示意圖。其目的在于說明器件的增益架構和控制回路設計。我們注意到,其不同于傳統(tǒng)穩(wěn)壓器的一個地方是輸出電壓的設置方式。

圖2,TPS62300簡化的結構示意圖

就傳統(tǒng)而言,參考電壓作用于故障放大器的正極,我們通過傳感輸出電壓并通過外部電阻器將其拆分為參考電壓,從而對所需的輸出電壓進行編程。

TPS62300通過內(nèi)部低功率低偏移運算放大器和外部電阻器編程放大參考電壓(VREF = 400mV)至所需輸出電壓的三分之二,從而生成輸出電壓。該電壓成為“動力系”的參考,其DC封閉回路增益(APT)為1.5。

功率放大器中的固定封閉回路增益不僅提供不變的“小信號”瞬變響應(不管編程輸出電壓如何),而且在L/C組合方面還實現(xiàn)了很嚴格的穩(wěn)壓誤差率和穩(wěn)健性。

圖3,TPS62300參考電壓放大器

(圖3)詳細給出了用于放大帶隙參考電壓的運算放大器的實施情況。該低偏移運算放大器可視為一個帶有A類輸出級的理想放大器,其特點是能夠提供電流,但不會吸收電流。

為了實現(xiàn)帶有負反饋的線性系統(tǒng),帶隙緩沖放大器需用低于VREF (400mV)的DAC電壓操作。只有這樣電流才能流出ADJ引腳,并通過R1和R2電阻器流向GND。

假定DAC電壓高于VREF,則VREF允許電流通過R 1 和R 2 的另一循環(huán)進入ADJ引腳。由于運算放大器輸出級(MOS1)只能提供電流,因此它不能再以線性模式工作。在這種情況下,用于電壓跟隨器配置的MOS1晶體管阻抗很高。實際上,為了“越過”ADJ電壓,我們只需將FB電壓保持高于內(nèi)部參考電壓(VREF)即可。

如果DAC電壓高于ADJ,參考進入ADJ引腳的電阻,則應考慮配備外部默認電壓設置電阻器R 1 和R 2 (1M ±30%)。

事實上,R1和R2串聯(lián)和進入ADJ引腳的電阻形成了分壓器。為了在溫度、線路和負載差異情況下實現(xiàn)誤差不超過1%的DC準確度,我們建議R 1 + R 2 的阻值在 20k 的范圍內(nèi)選擇。

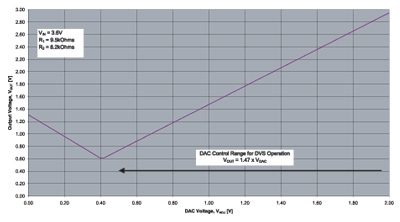

(圖4)顯示了TPS62300輸出電壓響應和DAC電壓的關系。為了實現(xiàn)動態(tài)電壓管理應用的最佳性能,我們建議工作時的DAC電壓高于450mV。

圖4,輸出電壓和DAC控制電壓的關系

I2C控制的自適應電壓縮放

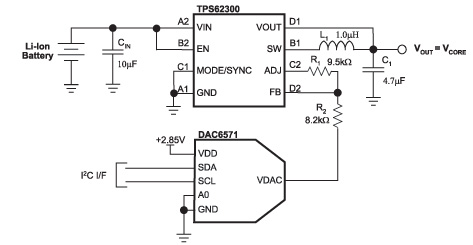

(圖5)顯示了基于TPS62300和DAC6571的電路實施。TPS62300可提供高達500mA的輸出電流和低至0.6V的輸出電壓。

圖5,動態(tài)電壓管理的應用電路

10位D/A轉(zhuǎn)換器DAC6571采用小型6引腳SOT23封裝。該設備是TI單通道D/A轉(zhuǎn)換器系列DAC7571/6571/5571的一部分,可提供12/10/8位的解析度。上述產(chǎn)品集成了一個I2C接口,可支持標準/快速模式(最大400 kbps)和高速模式(最大3.4 Mbps)。上電時,集成的重置上電電路系統(tǒng)將輸出電壓設置為0V。

在此應用中,TPS62 300直接由單個鋰離子電池供電。DAC6571采用穩(wěn)壓電源,本例為2.85V。該電源電壓可由另一系統(tǒng)軌得出。D/A轉(zhuǎn)換器的架構建立在R/2R電阻器串的基礎之上,由設計指定為單調(diào)。

就核心電源電壓而言,我們需要考慮兩種不同的操作模式:

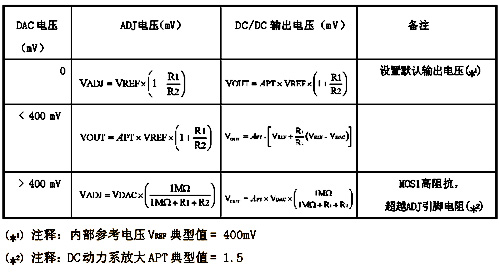

● 默認輸出電壓:

該電壓在啟動時DAC重置上電后有效。只要DAC未通過I2C接口編程,其輸出電壓將保持在0V。在此階段,核心電壓可由電阻器R1和R2根據(jù)表1(設置默認輸出電壓)中給出的方程式計算得出。

● DAC控制的輸出電壓:

在此模式下,D/A轉(zhuǎn)換器輸出電壓應高于0.45V,以利用“超越”功能。在此模式下,核心電壓可根據(jù)表1(MOS1高阻抗)中給出的方程式計算得出。

表1,總結了電源轉(zhuǎn)換器的操作:

DAC6571的輸出電壓計算如下:

![]()

D:二進制代碼的十進制等效值,加載到DAC寄存器中,其范圍可從0到1023。

VDD:DAC電源電壓

DAC控制模式中的核心電壓V OUT 可按如下公式計算:

![]()

DC動力系放大 APT 典型值= 1.5

(圖6)顯示了V DAC (DAC 輸出電壓)與 V OUT (核心電壓),其取決于 DAC 編程值。

圖6,VDAC 和 VOUT 電壓以及 DAC 值對照

在此應用中,我們選擇了1.3V的默認核心電壓。因此,R1 和 R2 必需的電阻器值應為:

R1:9.5k R2:8.2k

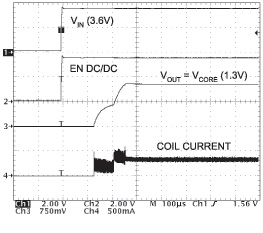

(圖 7)顯示了上電過程中的默認核心電壓調(diào)節(jié)。TPS62300 為 3.9Ω的電阻性負載供電,這就在 1.3V 默認輸出電壓上形成 330mA 的負載電流。在(圖7) 中,DC/DC 轉(zhuǎn)換器的啟動引腳 (EN) 與 VIN 一起驅(qū)動升高。核心電壓以最小延遲進行斜坡上升。不過,新型處理器可生成控制信號來自行啟動外部核心電源電路。在這種情況下,處理器將控制TPS62300的啟動引腳。

圖7,默認核心電壓VOUT在上電時設為1.3V

核心電壓呈斜坡狀上升至其系統(tǒng)設定值而處理器工作后,核心電壓可進行動態(tài)調(diào)節(jié)。為了降低功耗并延長電池使用壽命,處理器時鐘與核心電壓可調(diào)節(jié)至最佳。

結論

動態(tài)電壓管理解決方案能夠支持現(xiàn)有及下一代處理器內(nèi)核所要求的、快速而準確的電壓縮放。我們可通過 I2C 串行接口進行控制,該接口是用于此目的的通用接口。TPS62300 與 DAC6571 的小型封裝以及較少的外部組件數(shù)實現(xiàn)了超小型的解決方案尺寸。TPS62300 擁有出眾的負載與線路瞬態(tài)性能,這使該器件理想適用于新一代處理器的核心電源。