摘 要: 簡要介紹了一種基于事務(wù)的用于SoC系統(tǒng)芯片驗證的RVM驗證方法" title="驗證方法">驗證方法學(xué),以及應(yīng)用該方法學(xué)搭建的具有分層結(jié)構(gòu)的測試平臺" title="測試平臺">測試平臺,該測試平臺具有良好的可重用性" title="可重用性">可重用性。為了對該方法進行示范,驗證了TD-SCDMA手機芯片中的I2C模塊的RTL級實現(xiàn),并給出了相應(yīng)的測試平臺模型及其在系統(tǒng)級" title="系統(tǒng)級">系統(tǒng)級上的重用。

關(guān)鍵詞: RVM 可重用性測試平臺 基于事務(wù)的驗證 寄存器傳輸級驗證

隨著芯片復(fù)雜度的上升,驗證工作的復(fù)雜度和工作量呈指數(shù)形式上升。芯片系統(tǒng)要想盡快推向市場,驗證已經(jīng)成為極其重要的一環(huán),甚至是最重要的一環(huán),這就迫使系統(tǒng)芯片驗證工程師要盡可能多地重用已有的驗證資源。和設(shè)計重用類似,驗證的重用可以大大提高驗證的效率,減小驗證代價,得到高質(zhì)量的設(shè)計。

本文介紹的Synopsys的RVM(Reference Verification Methodology)驗證方法學(xué),是采用Vera硬件驗證語言建立目標模型環(huán)境、激勵自動生成、含錯誤指示的自核對式測試、覆蓋狀況分析能力[1]。通過簡化問題和建立復(fù)雜的測試平臺,為驗證工程師提供了更高的設(shè)計生產(chǎn)率,并使測試平臺具有良好的可重用性。

1 搭建可重用測試平臺的關(guān)鍵技術(shù)

在傳統(tǒng)驗證方法的許多情況下,測試平臺是在信號級(Signal Level)的接口上直接與可驗證性" title="可驗證性">可驗證性設(shè)計(Design Under Test,DUT)相通信的,即使用激勵直接驅(qū)動DUT的引腳,并通過檢查接口信號的值和變化,達到驗證設(shè)計功能的目的。這種驗證方法的抽象層次較低,平臺的開發(fā)與設(shè)計的接口協(xié)議緊密相關(guān),從而使得測試平臺的重用變得十分困難。所以測試平臺要想在不同的項目之間重復(fù)使用,至少是部分重用,首先測試平臺的結(jié)構(gòu)要被有效地模塊化,使得構(gòu)成平臺的各個模塊的改變和重用變得容易;其次測試平臺必須有明確的層次化定義,并要清晰地定義層和層之間的接口,使得各層之間具有一定的獨立性,改變底層并不會影響上層的重用[2]。

基于上述考慮,在驗證過程中提出了基于事務(wù)的驗證思想[3]。基于事務(wù)的驗證:可以在一個更高的層次上進行驗證,可以明顯地減少測試工作量,簡化調(diào)試,并有助于統(tǒng)計測量功能覆蓋率。所謂事務(wù)[4](Transaction)是指設(shè)計對象與事務(wù)處理器(Transactor)之間通過接口所做的一次數(shù)據(jù)或控制的傳輸。事務(wù)可以是一個簡單事務(wù),如讀取某個存儲器單元,也可以是一個復(fù)雜事務(wù),如傳輸整個結(jié)構(gòu)式數(shù)據(jù)報文;同時可以把單獨信號的特殊性、比特和字節(jié)的繁瑣性都模型化并且包裝起來,這樣把驗證提高到更高的抽象的層次上,這個層就是事務(wù)層,這樣能夠更有效地完成更多的功能。具體在RTL級的驗證中,可以設(shè)計一個用戶定義的事務(wù)處理器[5],將可驗證性設(shè)計(DUT)與所構(gòu)建的測試平臺連接起來,其中用戶定義的事務(wù)處理器能夠?qū)⑹聞?wù)級的測試激勵與RTL級的信號(Singal)進行相互轉(zhuǎn)換。

基于事務(wù)的驗證工具讓驗證工程師除了可以在信號/引腳級上進行驗證,還可以在事務(wù)級上進行驗證,從而提高了驗證工程師的設(shè)計效率,同時驗證的模塊化也大大地提高了驗證的可重用性。

2 RVM驗證方法學(xué)

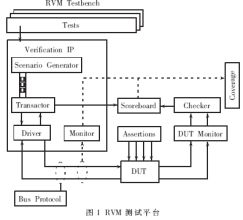

RVM驗證方法學(xué)主要是基于事務(wù)驗證的思想,結(jié)合隨機化驗證和覆蓋率驅(qū)動技術(shù),幫助驗證工程師快速建立一個可重用的驗證環(huán)境。RVM采用了易于驗證重用的分層測試平臺結(jié)構(gòu),同時它還具有全面的采用面向?qū)ο蠹夹g(shù)的庫,從而使RVM驗證環(huán)境模塊化、實用化。從基于事務(wù)驗證思想的角度來分析,RVM可以分為三層:信號層、事務(wù)層和測試層。RVM測試平臺結(jié)構(gòu)如圖1[6]所示。

其中,信號層是與被測設(shè)計對象(DUT)直接聯(lián)系的,主要起到事務(wù)層和DUT連通的作用。事務(wù)層則包括了Scenario Generator、Driver、Monitor、Transactor、Scoreboard和Checker,它將根據(jù)上層測試層的請求,將測試層協(xié)議映射到信號層。測試層(Tests)用于在系統(tǒng)中協(xié)調(diào)事務(wù)層的處理。

RVM的分層結(jié)構(gòu)使驗證的抽象層次從信號層提升到了事務(wù)層,很好地利用了事務(wù)級驗證的思想。這樣驗證工程師就可以不用太關(guān)心DUT內(nèi)部的具體實現(xiàn)過程,只需根據(jù)設(shè)計工程師提供的設(shè)計文檔,提取出DUT工作所需的激勵和輸入輸出的端口信息以及相應(yīng)的時序關(guān)系,就可以進行測試平臺的設(shè)計和驗證代碼的編寫工作了,設(shè)計出的測試平臺具有明顯的模塊化特征,易于重用。

為了更好地構(gòu)建RVM驗證環(huán)境,完成層與層之間的通訊,RVM還可以直接調(diào)用RVM驗證基類函數(shù)庫,里面定義了很多標準的函數(shù)類[7]。主要包括構(gòu)造事務(wù)對象的RVM_DATA類、構(gòu)造處理事務(wù)對象的處理器(Transactor)的RVM_XACTOR類、構(gòu)造傳輸事物對象的通道(Channel)的RVM_CHANNEL類、構(gòu)造控制整個驗證環(huán)境的RVM_ENV類和反饋信息的消息類RVM_LOG等。有了這些基類后,驗證工程師很容易實現(xiàn)各個組件間的同步關(guān)系和事物對象在組件間的傳輸?shù)龋粌H使得驗證工程師能很容易地編寫一些較復(fù)雜的測試平臺,而且還使得編寫出的驗證環(huán)境更容易理解、調(diào)試和重用。

3 RVM驗證方法學(xué)在芯片驗證中的應(yīng)用

筆者在重郵信科TD-SCDMA手機芯片的驗證中運用了RVM驗證方法學(xué)來搭建測試平臺,提高了驗證的效率,同時也大大提高了驗證資源的可重用性。本文重點介紹芯片中I2C總線的寄存器傳輸級(Register Transfer Level,RTL)驗證及相應(yīng)測試平臺的搭建。I2C總線(即IIC總線,Inter Integrated Circuit Bus)是一種用于IC控制的簡單的雙向兩線串行總線,系統(tǒng)中每個I2C器件都有一個唯一的地址。發(fā)送器或接收器可以在主模式或從模式下操作。I2C總線最重要的特征就是只要求兩條總線線路:一條串行數(shù)據(jù)線SDA,一條串行時鐘線SCL。簡單的兩線串行I2C總線將IC間互聯(lián)減到最小。

?

3.1 I2C的RTL級驗證

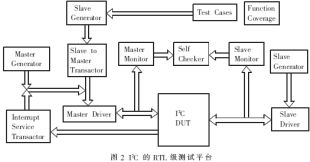

在驗證過程中,需要對邏輯功能、模塊行為、波形定時關(guān)系等進行檢查,如果不滿足要求,會輸出仿真錯誤信息,以引起驗證人員注意。其中,I2C的RTL級測試平臺的結(jié)構(gòu)如圖2所示。

3.1.1測試平臺中的主要模塊

(1)可驗證性設(shè)計模塊(DUT):即被測試設(shè)計模塊,在測試中提供給信號層端口信息,實現(xiàn)與整個驗證模塊的正常通訊。本文中的I2C DUT主要支持三種工作方式:寫、連續(xù)讀(直接讀取)和復(fù)合讀(先寫后讀)。DUT對外的主要通信端口如表1所示。

(2)測試例模塊(Testcases):Testcase是頂層模塊,控制著整個環(huán)境的運行。主要是驗證工程師根據(jù)設(shè)計人員提供的設(shè)計分析文檔編寫隨機測試例,限制底層模塊激勵的產(chǎn)生和驅(qū)動,驗證工程師可以根據(jù)需要編寫的多個測試例來完成模塊所有功能的測試。I2C模塊共寫了四個測試例,分別是寫、連續(xù)讀、復(fù)合讀和隨機產(chǎn)生錯誤ACK的測試例。

(3)激勵產(chǎn)生模塊(Generator):這個模塊主要是產(chǎn)生驗證DUT的隨機激勵。這些激勵被封裝在一個數(shù)據(jù)對象(data object)或事務(wù)(transaction)中,Generator將產(chǎn)生的這些數(shù)據(jù)對象或者事務(wù)通過輸出通道傳到下層模塊。I2C包括兩個Generator:Master Generator和Slave Generator。Master Generator主要是隨機產(chǎn)生DUT的配置數(shù)據(jù),如:寄存器的地址配置信息等。Slave Generator主要是隨機產(chǎn)生讀、寫的數(shù)據(jù)和類型等事務(wù)序列。

(4)驅(qū)動模塊(Driver):包括主機驅(qū)動(Master Driver)、從機驅(qū)動(Slave Driver)和中斷服務(wù)程序(Interrupt Service Transactor)。在Master Driver中定義了寫、讀兩個任務(wù)(task),將寫或讀過程中的所有激勵都封裝在任務(wù)(task)中。Master Driver模仿外圍設(shè)備(APB)通過對DUT與APB的外部接口進行驅(qū)動,將產(chǎn)生的數(shù)據(jù)傳給DUT。Slave Driver主要是模仿Master要訪問的外設(shè),通過Slave Generator隨機產(chǎn)生一些讀時需要的數(shù)據(jù),根據(jù)端口i2c_scl和i2c_sda_o來判斷何時主機開始讀數(shù)據(jù),然后驅(qū)動i2c_sda_i來輸出數(shù)據(jù)并送到DUT的讀寄存器。Interrupt Service Transactor是一個中斷服務(wù)程序,當接收到中斷時,會把中斷信息傳給Master Driver。

(5)監(jiān)控器(Monitor)和自檢器(Checker):I2C共有兩個Monitor:Master Monitor和Slave Monitor,分別負責監(jiān)測主機和從機的端口信息。Monitor時刻監(jiān)測DUT的端口信息,將DUT端口變化的數(shù)據(jù)信息記錄在一個事務(wù)中,通過相應(yīng)的事務(wù)通道將這個事務(wù)送到Checker中。Checker將從兩個Monitor中接收到的事務(wù)進行自動比較,檢查DUT是否存在bugs。

(6)功能覆蓋(Function Coverage):功能覆蓋模塊和測試平臺中的所有模塊都有聯(lián)系,使用功能覆蓋可以幫助找出功能上的缺陷,主要用來衡量模塊設(shè)計是否符合設(shè)計需求的所有功能。在I2C模塊中主要考察了寄存器配置、中斷和使能等覆蓋的情況。

3.1.2 測試結(jié)果

通過編寫隨機測試例使DUT的驗證達到了代碼覆蓋率96.65%和功能覆蓋率100%。根據(jù)驗證的要求,代碼覆蓋率應(yīng)該達到100%。通過和設(shè)計工程師的交流,找出沒有覆蓋到的代碼,查找原因,發(fā)現(xiàn)了一些驗證中的不足和源程序中的冗余及缺陷(bug),通過修改源代碼,同時增加一些直接的測試例,使代碼達到了完全的覆蓋。

在驗證中采用了含錯誤指示的自核對式測試技術(shù),在生成的.log文件中根據(jù)是否有錯誤報警來判斷模塊設(shè)計或驗證代碼是否存在缺陷,免去了直接從仿真波形上查找錯誤的繁瑣性。但在測試中,通過仿真出來的波形來檢驗驗證的過程及結(jié)果也是非常必要的,特別是牽涉到時序方面的驗證時,仿真波形更顯示出其在驗證過程中的作用;從波形上可以直接獲取信號的信息,對驗證代碼進行修改完善,同時也能觀察到存在于DUT內(nèi)部的信號,查找出更多的bug。在驗證I2C模塊中仿真出來的寫操作部分波形如圖3所示。

通過采用RVM設(shè)計的測試平臺,I2C模塊的RTL級驗證很成功,達到了預(yù)期的效果,設(shè)計的測試平臺模塊性強,易于理解和重用。

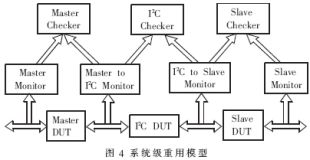

3.2 I2C驗證模塊在整個系統(tǒng)級驗證中的重用

進行完RTL級的驗證后,需要把SoC芯片中的各個模塊通過接口連接起來,進行整個系統(tǒng)級的驗證。在系統(tǒng)級驗證時,驗證工程師需要對自己的驗證模塊進行監(jiān)控,檢查各個模塊的輸入和輸出端口,進行輸入輸出結(jié)果的比較。此時,可以將模塊級測試平臺中的部分模塊重用到系統(tǒng)級驗證中來。由于此時的激勵是由系統(tǒng)產(chǎn)生的,所以驗證工程師只需要把各自模塊里面的Monitor、Checker及Functional Coverage模塊重用到系統(tǒng)級即可。系統(tǒng)級中I2C驗證模型如圖4所示。

圖2中的Master Monitor、Self checker和Slave Monitor分別被重用到圖4中的Master to I2C Monitor、I2C Checker和I2C to Slave Monitor,同時功能覆蓋模塊也可以重用到系統(tǒng)級,為系統(tǒng)級的驗證節(jié)省了很多重新編寫新代碼的工作和寶貴的時間。

通過實際驗證設(shè)計,與傳統(tǒng)的測試平臺比較,基于RVM的可重用性SoC測試平臺具有更高的抽象性、更清晰的層次性和結(jié)構(gòu)的模塊化,易于驗證的重用,提高了驗證的效率,加快了產(chǎn)品設(shè)計和面市時間。

參考文獻

1孫海平,丁 健.系統(tǒng)芯片(SoC)驗證方法與技術(shù)[M].北京:電子工業(yè)出版社,2005

2 Keating M, Bricaud P. Reuse methodology manual for system on a chip designs(third edition).[M] Kluwer Academic Pub-lishers,2002

3 詹文法. 測試平臺的可重用性研究.合肥工業(yè)大學(xué)碩士學(xué)位論文[D],2004:22~35

4 孟 慶,何樂年等.基于事務(wù)的SoC驗證策略.半導(dǎo)體技術(shù)[J],2002;27(6):29~32

5 王錦程,李德識等.SCV及其在SoC驗證中的應(yīng)用.武漢大學(xué)學(xué)報[J],2004;37(5):116~119

6 SYNOPSYS data sheet. VCS verificaton library. Printed in the U.S.A,2005

7 SYNOPSYS. Reference verification methodology user guild. Version 8.5.11, December 2004