新興的無線連接技術(shù)促使更多產(chǎn)品向新一代商務(wù)及家庭網(wǎng)絡(luò)應(yīng)用方向發(fā)展。因此,網(wǎng)絡(luò)市場中的用戶終端設(shè)備(CPE:customer premises equipment)部分,也正朝著消費市場的狀態(tài)轉(zhuǎn)變。

CPE產(chǎn)品的成功,需要由一個設(shè)計平臺及靈活的產(chǎn)品開發(fā)流程來支撐,以滿足各種新興網(wǎng)絡(luò)協(xié)議的性能需求,加快研發(fā)進程,最終提供經(jīng)濟而節(jié)能的終端產(chǎn)品。

圖1網(wǎng)絡(luò)市場中設(shè)備數(shù)量分布

技術(shù)發(fā)展動力

對網(wǎng)絡(luò)設(shè)備而言,日益增長的帶寬需求是最為顯著的技術(shù)發(fā)展動力。曾有人指出帶寬正以類似于摩爾定律的方式增長,如:客戶端的帶寬每18-24個月增加一倍,而核心/光纖帶寬約每8月增長一倍[2]。

然而,日益增長的帶寬需求并不是唯一促進技術(shù)發(fā)展的原因。對CPE的功能及智能性需求的增長也是另一種驅(qū)動因素,因此,單單采用更大更快的處理器并不是最為有效的方案。

更多功能的集成、增強的安全性和多種協(xié)議的發(fā)展等都將使CPE產(chǎn)品越來越復(fù)雜。不同協(xié)議的交換處理是眾多CPE應(yīng)用產(chǎn)品的普遍需求。如:無線局域網(wǎng)接口設(shè)備中的核心功能是在以太網(wǎng)和多種IEEE802.11接口標(biāo)準(zhǔn)間進行轉(zhuǎn)換。產(chǎn)品需求中可能會需要接口設(shè)備能夠提供多種接入點,以支持管理多種格式數(shù)據(jù)流的需求。

即使網(wǎng)絡(luò)產(chǎn)品不是便攜式的,低功耗也非常重要。低功耗設(shè)計可以降低對外殼及印刷電路板(PCB)制造的限制,也無需電扇散熱。除去了這些問題,設(shè)計的可靠也將大大提高。

圖2將各類產(chǎn)品集中使用的思路促使應(yīng)用產(chǎn)品往集成化方向發(fā)展

為了達到優(yōu)良的實時性能,處理器應(yīng)能有效地管理中斷,并同時具備足夠的數(shù)據(jù)處理能力。上下文的切換也是關(guān)鍵的需求,具有在中斷服務(wù)程序和任務(wù)模式編碼之間有效切換的能力會帶來更佳的性能。當(dāng)然,還應(yīng)盡量減少中斷服務(wù)和進行上下文切換的延時。

這類產(chǎn)品中的存儲器管理是個需要仔細(xì)考慮的問題。完全的嵌入式系統(tǒng)通常運行在固定的程序集中,無需加入新的程序。這樣的應(yīng)用產(chǎn)品并不需要帶有地址轉(zhuǎn)換的完整存儲器管理單元(MMU)。更簡單的存儲器保護單元(MPU)通常可以高效地運行實時操作系統(tǒng)(RTOS),允許多程序運行,進行上下文切換時開銷更少。含有 MMU的內(nèi)核進行中斷服務(wù)時可能比基于MPU的內(nèi)核要低效一些,同時還需要為地址轉(zhuǎn)換設(shè)置更大的外部存儲器。

CPE產(chǎn)品正朝著家用消費品市場進軍。目前,市場競爭激烈,終端設(shè)備的價格便成為主要的競爭優(yōu)勢。同樣地,縮短產(chǎn)品上市時間,也是提高市場占有率的重要優(yōu)勢。客制化終端網(wǎng)絡(luò)設(shè)備將真正縮短推出系列產(chǎn)品的上市時間。市場需要一種既能節(jié)約開發(fā)費用,又能縮短研發(fā)時間,并且能簡便地開發(fā)系列產(chǎn)品的技術(shù)方案。

無論從商務(wù)或技術(shù)角度出發(fā)考察一個片上系統(tǒng),都需要處理器方案能滿足多種網(wǎng)絡(luò)應(yīng)中的特殊控制和信號處理需求。設(shè)計的技術(shù)需求表明,若處理器性能遠(yuǎn)遠(yuǎn)高于實際需求,即設(shè)計了太多不需要的功能,意味著將無端地增加產(chǎn)品成本;但一定的性能冗余和靈活性可以支持產(chǎn)品的后續(xù)發(fā)展,而無需進行更本性的重新設(shè)計。

總結(jié)上述兩個驅(qū)動因素,開發(fā)人員應(yīng)能夠從技術(shù)和商業(yè)兩方面來衡量實現(xiàn)一個具體設(shè)備。

ARM在網(wǎng)絡(luò)設(shè)備中的應(yīng)用

為了增加帶寬并擁有更復(fù)雜的協(xié)議數(shù)據(jù)交換能力,許多設(shè)計人員正考慮在設(shè)計中使用雙核。

CPE系統(tǒng)需要滿足多重的復(fù)雜控制需求。許多系統(tǒng)體系結(jié)構(gòu)建立于單內(nèi)核基礎(chǔ)上,管理高級別的功能,如進行系統(tǒng)配置操作和運行實時操作系統(tǒng),而后與專用的狀態(tài)機集成,進行如數(shù)據(jù)包處理等操作。然而,這樣做使得設(shè)計和調(diào)試非常復(fù)雜,特別是設(shè)計含有多重私有狀態(tài)機時。

嵌入式軟件技術(shù)方案相較于復(fù)雜的私有硬件技術(shù)方案更易維護和推廣運用。嵌入式軟件技術(shù)方案能使用高級語言進行編程,使用眾所周知的程序員模式,并擁有大量具有豐富經(jīng)驗的工程師作為后盾。

ASIC的集成度已經(jīng)非常高,因而,CPU內(nèi)核的面積非常小。用第二個或第三個處理器來代替以往用多重的獨立硬件模塊顯得更加經(jīng)濟和實際。

在此種趨勢的推動下,ARM推出了集成了雙ARM946E-S微處理器內(nèi)核的PrimeXsys雙內(nèi)核平臺(946DCP)。

ARM946E-S特點

ARM946E-S內(nèi)含有ARM9E-S?內(nèi)核,為運行實時操作系統(tǒng)的嵌入式產(chǎn)品提供指令(I)、數(shù)據(jù)(D)高速緩存、緊密耦合存儲器(TCM)、寫緩沖器、存儲器保護單元(MPU)。指令和數(shù)據(jù)緩存和TCM緩存都是可配置的。存儲器體系結(jié)構(gòu)令設(shè)計者可依據(jù)實際情況調(diào)整緩存和TCM大小。

ARM9E-S微處理體系結(jié)構(gòu)提供了快速中斷響應(yīng)和上下文切換功能。該體系結(jié)構(gòu)非常合適用于如Wind River的VxWorks或Mentor Graphics Nucleus等小型實時操作系統(tǒng)(RTOS),非常適合于CPE設(shè)計。增強型DSP指令集可直接在CPU內(nèi)核上運行,滿足一些DSP需求,不需要另外一個獨立的DSP處理器。

EDN嵌入式微 處理器基準(zhǔn)協(xié)會(EEMBC,www.eembc.org)提供了一套完整的嵌入式處理器測試標(biāo)準(zhǔn)。EEMBC Netmark?網(wǎng)絡(luò)基準(zhǔn)是一套路由測試標(biāo)準(zhǔn)。其包含開路最短路徑第一(OSPF/Dijkstra)算法,數(shù)據(jù)包流路由基準(zhǔn),路

由表算法等。該基準(zhǔn)對處理器在網(wǎng)絡(luò)運用時實現(xiàn)的功能進行了模擬。

這套測試基準(zhǔn)中包含壓縮的路由測試基準(zhǔn),用實際的IP幀結(jié)構(gòu)執(zhí)行數(shù)據(jù)打包和路由表查詢。該基準(zhǔn)可使用不止一個長度的路由表,因而更為高效。這避免了合成測試基準(zhǔn)中單一尺寸路由表的缺陷。ARM為ARM946E-S內(nèi)核提供Netmark基準(zhǔn)。在與ARM簽訂了NDA之后,您可獲得該基準(zhǔn)。

PrimeXsys雙核平臺

PrimeXsys雙核平臺(圖3)提供了可擴展、預(yù)集成的基礎(chǔ)級IP,支持RTOS的直接運行。946 DCP采用多層AMBA?片上總線體系結(jié)構(gòu),在交叉型AHB總線矩陣中支持多重總線管理,并提供非常高的帶寬。在946DCP中添加IP,可以用主、從方式訪問系統(tǒng)總線。相應(yīng)地,AMBA外設(shè)總線(APB)為速度較慢的外設(shè)提供了更節(jié)能的片上系統(tǒng)連接方式。

每個內(nèi)核內(nèi)都含有向量中斷控制器(VIC)和嵌入式跟蹤宏單元(ETM?)。當(dāng)內(nèi)核全速工作時,ETM監(jiān)控ARM指令和數(shù)據(jù)總線,在與跟蹤調(diào)試工具進行數(shù)據(jù)交換前,將數(shù)據(jù)暫存到MultiTrace?分析器中。

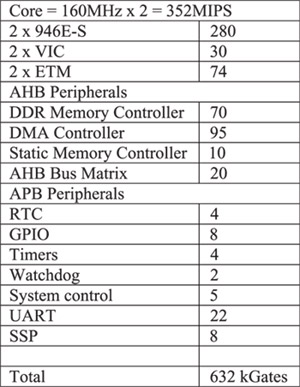

表1為946 DCP中IP主要模塊的性能指標(biāo)。

表1. 雙核平臺模塊門數(shù)(單位:千門)

半導(dǎo)體合作伙伴或系統(tǒng)集成商在946 DCP基礎(chǔ)上可進行自身產(chǎn)品的開發(fā),非常簡便,各公司可根據(jù)各種不同的需求制造各種產(chǎn)品。為硬件與其它IP集成提供多種總線主、從端口,PrimeXsys平臺負(fù)責(zé)處理軟硬件開發(fā)過程。ARM的PrimeCell庫中還包括了其他外設(shè)許多外設(shè)IP。

PrimeXsys平臺的另一個關(guān)鍵價值為:在CPU內(nèi)核之上設(shè)立了新的IP標(biāo)準(zhǔn),使第三方合作伙伴可以為PrimeXsys平臺提供不同的軟、硬件IP技術(shù)方案。

PrimeXsys技術(shù)基礎(chǔ)(圖3)提供了子系統(tǒng)級設(shè)計,包括CPU內(nèi)核和其他預(yù)集成的部件,為開發(fā)特殊應(yīng)用平臺提供穩(wěn)定的基礎(chǔ)設(shè)計。預(yù)集成部件至少應(yīng)使內(nèi)核具有裝載操作系統(tǒng)的能力。在以雙核技術(shù)為基礎(chǔ)的情況下,在預(yù)集成模塊中添加邏輯功能,是實現(xiàn)如內(nèi)核通信和調(diào)試等功能的必須條件。在其它基礎(chǔ)部件中綜合其他功能,適于創(chuàng)建子系統(tǒng)體系結(jié)構(gòu),無需將該基礎(chǔ)部件建為特殊用途的產(chǎn)品。

與硬件子系統(tǒng)相同,技術(shù)基礎(chǔ)包括子系統(tǒng)的軟件部分--并不只是指預(yù)移植的操作系統(tǒng),也指驅(qū)動程序和軟件庫(對于特殊硬件模塊在基礎(chǔ)部件中的驅(qū)動非常必要)。

ARM PrimeXsys技術(shù)基礎(chǔ)將作為特殊應(yīng)用的PrimeXsys平臺技術(shù)方案基礎(chǔ)。

雙核平臺刺激第三方公司開發(fā)軟硬件IP、提供如TCP/IP等功能(通過軟件協(xié)議堆棧)、安全處理如編/解碼運算法則、提供關(guān)鍵技術(shù)方案和許多其他應(yīng)用軟件。

圖3. ARM PrimeXsys 946雙核平臺

雙核性能

決定系統(tǒng)性能的一些主要的參數(shù)包括CPU性能、存儲器帶寬、系統(tǒng)總線帶寬、中斷響應(yīng)延時等。

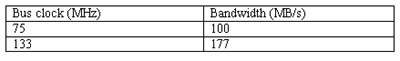

PrimeXsys雙核平臺體系結(jié)構(gòu)可為多種CPE產(chǎn)品提供充足的存儲帶寬。表2所示為946 DCP的存儲帶寬情況。

表2:PrimeXsys 946 DCP存儲帶寬。

*表2假設(shè):

32位SDRAM

AHB存取模式--70%讀、30%寫

所有存取以字進行

50%為四次觸發(fā),30%為八次觸發(fā),20%為16次觸發(fā)

存儲器存取:

50% bank open, correct page

30% bank closed

20% bank open, incorrect page

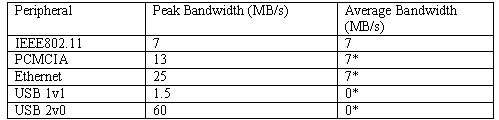

表3. 應(yīng)用產(chǎn)品帶寬需求。

*表3條件:

平均帶寬采用PCMCIA和USB接口,或Ethernet和USB接口,并不需要并口。

應(yīng)用產(chǎn)品帶寬需求如表3所述,提供了CPE接口的評估值。例如:存取點在802.11上,PCMCIA/USB1v1 轉(zhuǎn)接口需要21.5MB/s的峰值帶寬,以太網(wǎng)和USB2v0接口需要平臺提供至少為92MB/s的峰值存儲帶寬。

PrimeXsys開發(fā)

PrimeXsys平臺的目的是為了將預(yù)集成的IP優(yōu)勢發(fā)揮到極至。系統(tǒng)公司若要最大限度地體現(xiàn)平臺的價值,就必須提供在平臺上又快又準(zhǔn)確地建立其他技術(shù)方案的方法。為了達到此上目的,PrimeXsys系統(tǒng),包括其他一些測試基準(zhǔn),將保證開發(fā)進程非常快速,并能最終開發(fā)出高質(zhì)量的設(shè)計產(chǎn)品。

AMBA的各項測試基準(zhǔn)將確保把IP加載到AMBA總線的同時可完全連接并符合AMBA片上總線標(biāo)準(zhǔn)。測試基準(zhǔn),通常基于Verisity的測試基準(zhǔn)自動控制語言E,迅速自動生成功能測試、數(shù)據(jù)檢測、功能覆蓋分析、HDL仿真控制。PrimeXsys測試基準(zhǔn)提供系統(tǒng)集成和系統(tǒng)確認(rèn)。

同時也 提供軟件開發(fā)模型(SDM)。該開發(fā)模型包括:內(nèi)核的指令集模擬器(ISS)、運行在ARMulator?測試環(huán)境下的附加IP模型(C語言)。雖然此種模式可運行RTOS,但模擬速度限制了ARMulator在實際應(yīng)用產(chǎn)品測試時的速度。該環(huán)境對于驗證寄存器的完整性、驅(qū)動初始化和操作系統(tǒng)移植具有非常大的意義。

為了進一步加快系統(tǒng)對基于FPGA的開發(fā)板的仿真速度,在得到硅芯原型前應(yīng)提供應(yīng)用開發(fā)和測試的環(huán)境。

調(diào)試多核系統(tǒng)

對于應(yīng)用產(chǎn)品來說,獲得雙核體系結(jié)構(gòu)具有非凡的意義,但是,對許多設(shè)計人員來說,調(diào)試雙核系統(tǒng)仍將遇到許多難題。

無論何時,RTOS將執(zhí)行若干線程。典型的應(yīng)用產(chǎn)品將執(zhí)行許多任務(wù),如:編解碼、數(shù)據(jù)包處理等。若系統(tǒng)管理兩個通道,這將導(dǎo)致有一、兩個任務(wù)同時運行,可能在同核上,也可能在異核上。因此,RTOS可能在兩個核之間切換運行。

無論系統(tǒng)配置如何,成功的調(diào)試便是在各個階段都能跟蹤編碼執(zhí)行情況,從開始執(zhí)行任務(wù),到發(fā)生中斷、上下文切換、數(shù)據(jù)處理。以不同的獨立調(diào)試系統(tǒng)調(diào)試獨立運行在不同核上的編碼是非常困難的。

PrimeXsys 946 DCP提供了針對復(fù)雜的多線程應(yīng)用軟件進行聯(lián)合調(diào)

試的方法。946 DCP可在由多源(包括雙核、附加的IP等)產(chǎn)生的斷點處進行交叉觸發(fā)。設(shè)計者可使用觸發(fā)器設(shè)置觸發(fā)點和單步運行,調(diào)試非常簡單,就如同在調(diào)試一個單核系統(tǒng)。ARM RealView多核調(diào)試器結(jié)合了一個仿真器和一個調(diào)試器,可對ARM的多核系統(tǒng)進行內(nèi)核的同步調(diào)試。

小結(jié)

CPE產(chǎn)品中的片上系統(tǒng)應(yīng)具有優(yōu)異的性能和低功耗特性,并能快速上市且開發(fā)費用低廉。CPE產(chǎn)品只有具有上述特性,產(chǎn)品才能獲得成功。ARM的PrimeXsys雙核平臺將能縮短產(chǎn)品上市時間、降低投資風(fēng)險、帶來更具競爭力的片上系統(tǒng)技術(shù)方案基礎(chǔ)平臺。

通過類似于ARM體系結(jié)構(gòu)的方法,把PrimeXsys平臺建立為業(yè)界標(biāo)準(zhǔn),將使ARM的合作伙伴們通過與ARM的合作關(guān)系受益,同時可以從第三方持續(xù)獲得各類創(chuàng)新的軟、硬件IP。