MIL-STD-1553B是一種時(shí)分制,命令/響應(yīng),集中控制式多路傳輸?shù)陌腚p工串行數(shù)據(jù)總線,其傳輸速度為1Mb/s,字長(zhǎng)為20b,數(shù)據(jù)有效長(zhǎng)度為16b,信息量最大的長(zhǎng)度為32個(gè)字。其信息格式有總線控制器BC(Bus Controller)到遠(yuǎn)程終端RT(Remote Terminal),RT到RC,RT到RT,廣播式和系統(tǒng)控制式。

MIL-STD-1553B總線協(xié)議已經(jīng)發(fā)展成為國(guó)際公認(rèn)的數(shù)據(jù)總線標(biāo)準(zhǔn),廣泛地應(yīng)用于航空電子綜合系統(tǒng)中,目前國(guó)內(nèi)外開(kāi)發(fā)的各種1553B總線采集卡,大多采用的是美國(guó)DDC公司生產(chǎn)的BU-6150接口芯片,但是該芯片價(jià)格比較昂貴,開(kāi)發(fā)成本較高,另許多商家望而興嘆。本文介紹的基于DSP的1553B總線通訊模塊的設(shè)計(jì),采用TI公司TMS320F206DSP芯片進(jìn)行數(shù)字信號(hào)處理,用FPGA進(jìn)行現(xiàn)場(chǎng)反復(fù)編程,降低了設(shè)計(jì)成本,滿足了1553B通訊模塊的開(kāi)發(fā)需求。

1 TMS320F206的簡(jiǎn)介

該1553B總線通訊模塊的DSP采用TI公司的TMS320F206,用來(lái)實(shí)現(xiàn)1553B總線協(xié)議的主體部分,實(shí)現(xiàn)字和消息的處理等功能,TMS320F206是TI公司近年來(lái)推出的一種性價(jià)比較高的定點(diǎn)DSP芯片,采用靜態(tài)CMOS集成電路工藝制造而成,DSP芯片先進(jìn)的哈佛結(jié)構(gòu)允許程序存儲(chǔ)器和數(shù)據(jù)存儲(chǔ)器獨(dú)立編址、獨(dú)立訪問(wèn),兩條總線可允許數(shù)據(jù)與指令的讀取同時(shí)進(jìn)行,從而使數(shù)據(jù)的吞吐率提高了一倍;專用的指令集提供了功能強(qiáng)大的信號(hào)處理操作。TMS320F206主要特點(diǎn)如下:

(1)5V工作電壓,20MHz主頻時(shí),指令周期50ns;3個(gè)外部引腳中斷;8級(jí)內(nèi)部硬件堆棧,存放調(diào)用/中斷返回地址;硬件等待;休眠的IDLE模式,低功耗;標(biāo)準(zhǔn)的IEEE1149.1仿真口。

(2)片內(nèi)64k程序空間,64k數(shù)據(jù)空間,64kI/O空間,32k全局存儲(chǔ)空間,片內(nèi)544×16b雙尋址RAM,32k×16b用戶可編程FLASH,作為程序空間,4k×16b單尋址RAM,程序空間和數(shù)據(jù)空間之前可以進(jìn)行數(shù)據(jù)搬移。

(3)片內(nèi)16b定時(shí)器,片上軟等待產(chǎn)生器,可以分別為程序空間,數(shù)據(jù)空間,I/O空間產(chǎn)生0-7個(gè)等待,片上振蕩器和鎖相環(huán)有倍頻和分頻功能,32b算術(shù)邏輯單元/累加器,16×16b乘法器,全雙工異步串口UART,增強(qiáng)的同步串口,帶4級(jí)FIFO。

2 系統(tǒng)的組成框圖和工作原理

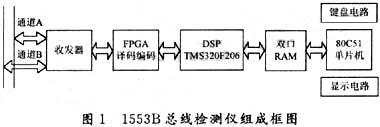

檢測(cè)儀采用單片機(jī)技術(shù),可編程邏輯器件(FPGA)技術(shù),數(shù)字信號(hào)處理(DSP)技術(shù),結(jié)合1553B總線收發(fā)技術(shù)研制而成。既可以對(duì)單個(gè)航空電子設(shè)備進(jìn)行離線檢測(cè),也可對(duì)飛機(jī)的整個(gè)總線的運(yùn)行和各個(gè)記載設(shè)備的數(shù)據(jù)傳輸進(jìn)行在線檢測(cè)。檢測(cè)儀整體采用個(gè)人數(shù)字助理(PDA)技術(shù),數(shù)據(jù)輸入、輸出、處理、控制、顯示等均集中在檢測(cè)儀。

系統(tǒng)組成框圖如圖1所示。

從數(shù)據(jù)信號(hào)流程方面:收數(shù)據(jù)時(shí),外部數(shù)據(jù)送到收發(fā)器進(jìn)行電壓轉(zhuǎn)換后,成為一組20b的串行數(shù)據(jù),經(jīng)過(guò)FPGA芯片EP20K200處理成16b并行數(shù)據(jù)經(jīng)擴(kuò)展口送到DSP處理,然后經(jīng)雙口RAM進(jìn)行數(shù)據(jù)緩存,需要顯示數(shù)據(jù)時(shí),單片機(jī)CPU對(duì)雙口RAM送來(lái)的16b并行數(shù)據(jù)進(jìn)行分析存儲(chǔ),按要求轉(zhuǎn)換成十六進(jìn)制,二進(jìn)制或者工程單位制送顯示器顯示,發(fā)數(shù)據(jù)時(shí),CPU將鍵盤輸入的數(shù)據(jù)按照十六進(jìn)制、二進(jìn)制或者工程單位制經(jīng)轉(zhuǎn)換后送雙口RAM緩存,DSP從雙口RAM讀入數(shù)據(jù),預(yù)處理后送EP20K200,EP20K200再進(jìn)行轉(zhuǎn)換處 理,輸出一組20b的串行數(shù)據(jù)到收發(fā)器,經(jīng)變壓耦合成符合1553B標(biāo)準(zhǔn)要求的串行數(shù)據(jù),再經(jīng)收發(fā)接口發(fā)送到數(shù)據(jù)總線上。

3 硬件電路設(shè)計(jì)

3.1 接收器和發(fā)送器

1553B航空電子系統(tǒng)中,各終端設(shè)備與總線之間采用的是耦合的方式,分為變壓器耦合和直接耦合,采用的美國(guó)DDC公司的BU-63152芯片,具有兩個(gè)完全獨(dú)立的雙余度端口,完全滿足1553B總線收、發(fā)的要求,接收器操作模式下,在引腳STROMB控制下,數(shù)據(jù)被變成雙向的TTL電平,從RX DATA OUT和其非腳輸出到下一級(jí)譯碼電路,發(fā)送器操作模式下,在引腳INHIBIT控制下,發(fā)送器部分從編碼電路接收數(shù)據(jù),發(fā)送到數(shù)據(jù)總線上。

3.2 FPGA模塊

將FPGA技術(shù)與數(shù)字信號(hào)處理DSP技術(shù)相結(jié)合是現(xiàn)代電子設(shè)計(jì)中常用的方法,該模塊中的FPGA芯片接口主要實(shí)現(xiàn)以下功能:

(1)將總線上的串行信息流轉(zhuǎn)換成處理機(jī)可以處理的并行信息或者與之相反;

(2)接收或發(fā)送信息時(shí),能夠識(shí)別或生成標(biāo)準(zhǔn)的1553B信息字和消息。

(3)完成與處理機(jī)之間的信息交換,包括1553B信息地址的分配,命令字(或狀態(tài)字)的譯碼或返回狀態(tài)字、發(fā)送數(shù)據(jù)字等。

用FPGA實(shí)現(xiàn)編解碼器,其基本功能與前面提到的BU-61580芯片相似,是該1553B總線檢測(cè)儀的關(guān)鍵技術(shù)。

3.3 DSP模塊

TMS320F206是TI公司近年推出的一款設(shè)計(jì)成本最低,結(jié)構(gòu)功能復(fù)雜度也較低的定點(diǎn)DSP,片內(nèi)32k FLASH,4.5k RAM可以滿足處理規(guī)模適中的任務(wù),該檢測(cè)儀中DSP模塊的設(shè)計(jì)主要是對(duì)時(shí)鐘電路,中斷以及數(shù)據(jù)和地址總線的接口技術(shù)的把握,其主要接口電路如圖2所示。

由DSP接口電路圖可以看出,DSP模塊為整個(gè)系統(tǒng)提供了時(shí)鐘電路,DSP芯片的中斷由EP20K200產(chǎn)生,一方面通知F206讀取數(shù)據(jù),一方面通知DSP進(jìn)行錯(cuò)誤處理,由于DSP芯片的流水線操作方式,數(shù)字信號(hào)處理速度功能強(qiáng)大,滿足了1553B協(xié)議傳輸速率大的特點(diǎn)。

3.4 雙口RAM和顯示模塊

由于在高速數(shù)據(jù)處理和采集系統(tǒng)中容易造成數(shù)據(jù)堵塞現(xiàn)象,高速數(shù)據(jù)接口的設(shè)計(jì)對(duì)整個(gè)系統(tǒng)數(shù)據(jù)傳輸?shù)臅惩ㄆ鹬匾淖饔茫撛O(shè)計(jì)中采用的美國(guó)DDC公司的8k雙口靜態(tài)RAM IDT7025解決了數(shù)據(jù)堵塞的問(wèn)題。

在該設(shè)計(jì)中顯示模塊采用了一種內(nèi)存接顯示模塊的硬件連接方式。DSP將欲顯示的數(shù)據(jù)送入雙口RAM,51單片機(jī)不斷掃描內(nèi)存,根據(jù)內(nèi)存中的數(shù)據(jù)做出相應(yīng)的處理,不斷刷新顯示屏上的內(nèi)容,雙口RAM的BUSY信號(hào)線為避免左右端口同時(shí)對(duì)同一存儲(chǔ)單元寫操作提供了硬件支持。設(shè)計(jì)中液晶顯示模塊采用16×16點(diǎn)陣的中文顯示模塊。

4 系統(tǒng)軟件設(shè)計(jì)

該1553B航空電子總線檢測(cè)儀軟件設(shè)計(jì)主要包括3大部分,用以驅(qū)動(dòng)數(shù)據(jù)采集板卡,完成對(duì)各寄存器的配置,實(shí)現(xiàn)數(shù)據(jù)的收發(fā)檢測(cè)。

4.1 FPGA控制程序

該部分采用硬件描述語(yǔ)言VHDL進(jìn)行編程,用Synplify進(jìn)行綜合,以及采用Max+Plus II進(jìn)行時(shí)序仿真,在FPGA上實(shí)現(xiàn)的MIL-STD-1553B總線接口中的曼徹斯特碼編碼、解碼器,該邏輯可由狀態(tài)機(jī)實(shí)現(xiàn),可劃分為4個(gè)狀態(tài)進(jìn)行;第1個(gè)狀態(tài)行是空閑狀態(tài),當(dāng)檢測(cè)到數(shù)據(jù)跳變沿時(shí),進(jìn)入第2個(gè)狀態(tài);第2個(gè)狀態(tài)為有效同步字頭檢測(cè)狀態(tài);當(dāng)檢測(cè)到有效同步字頭時(shí),啟動(dòng)第3個(gè)狀態(tài),用鎖相環(huán)分離時(shí)鐘,進(jìn)行碼型轉(zhuǎn)換;當(dāng)數(shù)據(jù)有效時(shí)進(jìn)入第4個(gè)狀態(tài),進(jìn)行并/串轉(zhuǎn)換及奇偶校驗(yàn)。FPGA接收數(shù)據(jù)流程如圖3所示。

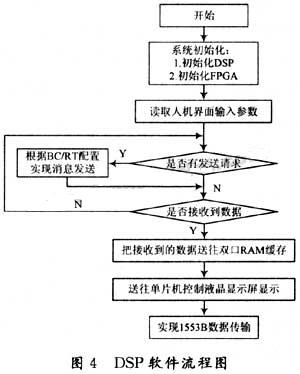

4.2 DSP模塊控制程序

DSP部分的軟件采用C語(yǔ)言和匯編語(yǔ)言混合編程,即具有C語(yǔ)言可移植性強(qiáng)的特點(diǎn),又具有匯編語(yǔ)言執(zhí)行速率快和直觀的特點(diǎn),該設(shè)計(jì)中DSP軟件設(shè)計(jì)主要完成對(duì)FPGA和其內(nèi)部通訊寄存器初始化;向FPGA發(fā)送數(shù)據(jù)時(shí)的控制命令操作,接受數(shù)據(jù)時(shí)命令字,狀態(tài)字的處理,以及通知FPGA接受數(shù)據(jù)等,是整個(gè)系統(tǒng)控制的核心部分。圖4給出DSP軟件控制流程圖。

5 結(jié)語(yǔ)

基于1553B總線的航空電子檢測(cè)儀主要用于部隊(duì)航空電子設(shè)備在線和離線檢測(cè),同時(shí)滿足BC和RT的功能,PDA的設(shè)計(jì)對(duì)檢測(cè)也提供了極大便利,當(dāng)然由于設(shè)計(jì)處于樣機(jī)階段,還存在一些不完善的地方,今后的改進(jìn)空間還比較大。