自適應(yīng)濾波器已經(jīng)廣泛應(yīng)用于信道均衡、回聲取消、系統(tǒng)識(shí)別、頻譜估計(jì)等各個(gè)方面。基于子帶分解的自適應(yīng)濾波在提高收斂性能的同時(shí)又節(jié)省了一定的計(jì)算量。基于子帶分解的自適應(yīng)濾波是先將輸入信號(hào)與參考信號(hào)經(jīng)過(guò)分解濾波器組進(jìn)行子帶分解、抽取、子帶自適應(yīng)濾波、內(nèi)插、通過(guò)合成濾波器組得到輸出信號(hào)。基于子帶分解的自適應(yīng)濾波器的優(yōu)點(diǎn):

(1)由于對(duì)信號(hào)的抽取,使完成自適應(yīng)濾波所需的計(jì)算量得以減少;

(2)在子帶進(jìn)行自適應(yīng)濾波使收斂性能有所提高。

l 基于子帶分解的自適應(yīng)濾波結(jié)構(gòu)

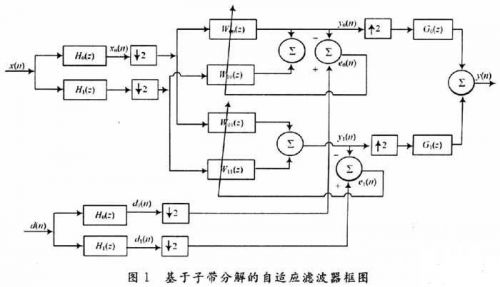

基于子帶分解的自適應(yīng)濾波,其時(shí)域結(jié)構(gòu)如圖1所示。將輸入信號(hào)x(n)和參考信號(hào)d(n)分別進(jìn)行子帶分解,抽取,在子帶上進(jìn)行自適應(yīng)濾波,再將子帶上的估計(jì)信號(hào)y0(n)和y1(n)經(jīng)內(nèi)插和合成濾波器組得到最后的合成信號(hào)。其中濾波器W00(n)和W11(n)是兩個(gè)子帶上的自適應(yīng)濾波器,而W01(n)和W10(n)表示子帶間自適應(yīng)濾波器。這是由于濾波器組均是FIR濾波器,不可能有銳截止的理想特性,只能以長(zhǎng)度為代價(jià)來(lái)?yè)Q取近似的特性;這時(shí)在嚴(yán)格采樣下得到的子帶信號(hào)必然有混疊,需加入子帶間濾波以消除其影響。這里的子帶自適應(yīng)濾波器采用基于NLMS算法自適應(yīng)濾波器。NLMS算法和LMS算法相比。雖然計(jì)算量稍有增加,但可使得自適應(yīng)濾波器收斂速度大大提高。

2 雙通道濾波器組的設(shè)計(jì)

本文采用的分析和綜合濾波器之間的關(guān)系如下:

H1(z)=H0(-z),G1(z)=-2H0(-z),G0(z)=2H1(-z)。由上述表達(dá)式可知設(shè)計(jì)的關(guān)鍵是設(shè)計(jì)H0(z),只要H0(z)確定,H1(z),G0(z),G1(z)也可確定。本文采用等波紋逼近設(shè)計(jì)法進(jìn)行濾波器設(shè)計(jì)。該方法設(shè)計(jì)的濾波器呈現(xiàn)等波紋頻響特性。等波紋逼近設(shè)計(jì)法設(shè)計(jì)的濾波器具有如下優(yōu)點(diǎn):

(1)由于誤差均勻分布于整個(gè)頻帶,對(duì)固定的階數(shù)N,可以得到最優(yōu)良的濾波特性;

(2)通帶最平坦,阻帶最小衰減達(dá)到最大。

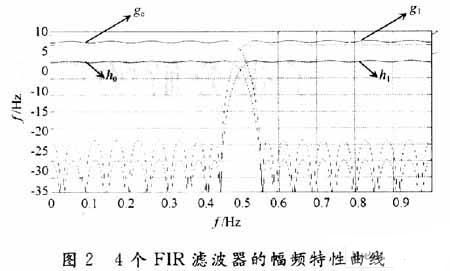

Matlab集成了一套強(qiáng)大的濾波器設(shè)計(jì)工具FDATOOL,可以完成多種濾波器的設(shè)計(jì)、分析和性能*估。本文中FPGA硬件實(shí)現(xiàn)部分用到的4個(gè)FIR濾波器的頻率特性曲線見(jiàn)圖2。

3 系統(tǒng)建模與仿真

DSP Builder是Altera公司推出的一個(gè)面向DSP開(kāi)發(fā)的系統(tǒng)級(jí)工具,它是作為Matlab的一個(gè)Simulink工具箱(ToolBox)出現(xiàn)的。DSP Bui-lder作為Simulink中的一個(gè)工具箱,使得在使用FPGA設(shè)計(jì)DSP系統(tǒng)時(shí)完全可以通過(guò)Simulink的圖形化界面進(jìn)行,只需簡(jiǎn)單地進(jìn)行DSP Builder工具箱中的模塊調(diào)用即可。

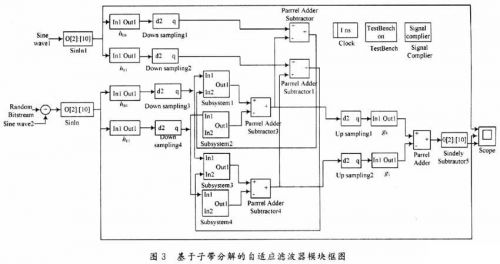

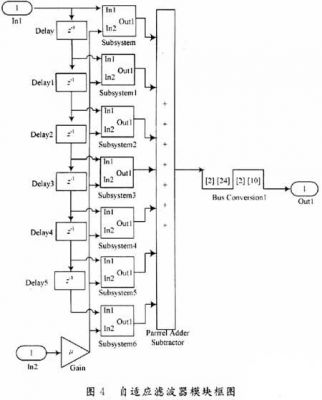

圖3中的基于子帶分解的自適應(yīng)濾波器模塊框圖系統(tǒng)由分析濾波器子系統(tǒng)h00,h01,h10,h11,綜合濾波器子系統(tǒng)g00,g01、抽取,插值,加法,減法器,自適應(yīng)濾波器等模塊組成。h00和h10是完全一模一樣的低通濾波器,h01和h11是完全一模一樣的高通濾波器。h00,h01,g00,g01的幅頻特性曲線見(jiàn)圖2。h00對(duì)應(yīng)圖2中的h0,h01對(duì)應(yīng)圖中的h1,g00對(duì)應(yīng)圖中的g0,g01對(duì)應(yīng)圖中的g1。Subysteml,Subyst-em2,Subystem3,Subystem4是自適應(yīng)濾波器。Subystem2,Subystem3自適應(yīng)濾波器的階數(shù)是Subysteml,Subystem4階數(shù)的1/20。期望信號(hào)由sine wavel模塊提供,輸入信號(hào)由Sine wave2和Random Bitstream疊加在一起的信號(hào)組成。系統(tǒng)所需的模塊都是直接調(diào)用DSP builder中的模塊。Subystem2是7階NLMS算法自適應(yīng)濾波器,其框圖見(jiàn)圖4。如果調(diào)高提高收斂速度,則可增加延遲模塊、自適應(yīng)子系統(tǒng)模塊,加法器模塊即可,但需消耗更多的硬件資源。

自適應(yīng)濾波器模塊主要由延遲單元,權(quán)值更新子系統(tǒng)、加法器模塊,乘法器模塊組成。它是將抽取過(guò)后的信號(hào)進(jìn)行自適應(yīng)濾波。

FIR濾波器的單位沖激響應(yīng)是有限長(zhǎng)的,其z變換為。分析和綜合濾波器系統(tǒng)主要由延遲單元、加法器、加法器模塊組成。分析和綜合濾波器不可能有銳截止的理想特性,必須通過(guò)增加階數(shù)來(lái)逼近。分析濾波器子系統(tǒng)h00,h01,h10,h11,綜合濾波器子系統(tǒng)g00,g01均采用橫截型結(jié)構(gòu)。

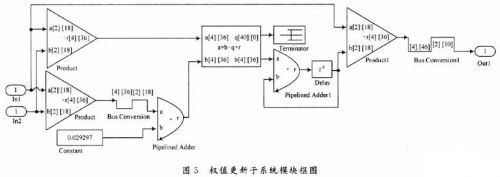

權(quán)值更新子系統(tǒng)模塊主要由乘法器、除法器、加法器、延遲單元、總線類型轉(zhuǎn)換等模塊組成。該子系統(tǒng)主要完成濾波器的權(quán)值更新。w(k+1)=w(k)+μ/γ+xT(k)x(k)e(k)x(k)運(yùn)算和wi(k)xi(k)運(yùn)算。

4 仿真

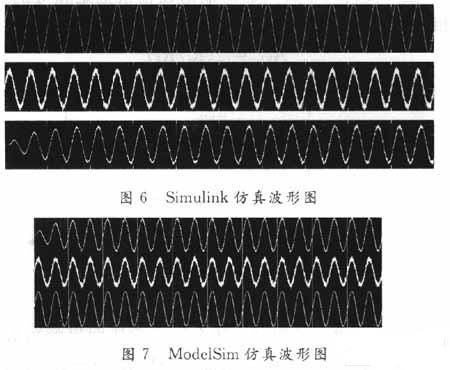

Matlab的Simulink環(huán)境具有強(qiáng)大的圖形化仿真驗(yàn)證功能,用DSP Builder模塊設(shè)計(jì)好一個(gè)新的模型后,可以直接在Simulink中進(jìn)行算法級(jí)、系統(tǒng)級(jí)仿真驗(yàn)證。該設(shè)計(jì)的Simulink仿真如圖6所示,輸出信號(hào)含有毛刺,這說(shuō)明輸出信號(hào)與期望信號(hào)還有一定的穩(wěn)態(tài)誤差。可以通過(guò)增加濾波器的階數(shù),或修改步長(zhǎng)控制參數(shù)μ,以達(dá)到更好的效果。

運(yùn)行Signal complier可將通過(guò)Simulink的模塊文件(.mdl)轉(zhuǎn)換成通過(guò)的硬件描述語(yǔ)言VHDL文件;運(yùn)行Testbench(測(cè)試平臺(tái))可將Sine wavel、Sinewavel+noise、Clock轉(zhuǎn)換成針對(duì)HDL仿真器ModelSim的測(cè)試文件。由圖7可知輸出信號(hào)Sine out逐漸趨于穩(wěn)定,逼近與期望信號(hào)sine wavel,因此設(shè)計(jì)結(jié)果滿足要求,能夠?qū)崿F(xiàn)自適應(yīng)過(guò)程。

5 結(jié)語(yǔ)

本文只是從硬件的角度出發(fā)設(shè)計(jì)兩個(gè)子帶自適應(yīng)濾波器的FPGA實(shí)現(xiàn)。由于分解濾波器組的非理想特性,有必要采取子帶間濾波,子帶間的濾波可大大提高收斂速度。子帶自適應(yīng)濾波器的設(shè)計(jì)和研究過(guò)程是比較復(fù)雜的,這里就主要的設(shè)計(jì)研究思想做了一個(gè)闡述,鑒于設(shè)計(jì)中的自適應(yīng)濾波器的階數(shù)選取相對(duì)較小,因而對(duì)自適應(yīng)濾波器的穩(wěn)態(tài)誤差有一定的影響,通過(guò)增加自適應(yīng)濾波器的階數(shù),分析和綜合濾波器的階數(shù)、數(shù)據(jù)的位數(shù)來(lái)提高精度。