引 言

自適應(yīng)濾波器一直是信號(hào)處理領(lǐng)域的研究熱點(diǎn)之一,經(jīng)過多年的發(fā)展,已經(jīng)被廣泛應(yīng)用于數(shù)字通信、回聲消除、圖像處理等領(lǐng)域。自適應(yīng)濾波算法的研究始于20世紀(jì)50年代末,Widrow和Hoff等人最早提出最小均方算法(LMS)。算法由于結(jié)構(gòu)簡(jiǎn)單,計(jì)算量小,易于實(shí)時(shí)處理,因此在噪聲抵消,譜線增強(qiáng),系統(tǒng)識(shí)別等方面得到了廣泛的應(yīng)用。為了克服定步長(zhǎng)LMS算法中收斂速度、收斂精度及跟蹤速度等對(duì)步長(zhǎng)大小選取相互矛盾的缺點(diǎn),人們提出了許多變步長(zhǎng)LMS算法,但是,當(dāng)輸入信號(hào)具有強(qiáng)相關(guān)性時(shí),例如語(yǔ)音信號(hào),LMS算法及NLMS算法的收斂速度將急劇下降。因此,本文對(duì)進(jìn)入自適應(yīng)濾波器的輸入信號(hào)首先進(jìn)行解相關(guān)預(yù)處理,再對(duì)自適應(yīng)濾波器進(jìn)行歸一化LMS。

很多自適應(yīng)濾波器是在通用DSP處理器上通過編寫軟件代碼實(shí)現(xiàn)。這種濾波器在系統(tǒng)實(shí)時(shí)性要求不高的情況下,能很好地滿足濾波要求,但在實(shí)時(shí)性要求較高的場(chǎng)合(如3G移動(dòng)通信,網(wǎng)絡(luò)會(huì)議等),這種濾波器在處理速度和抗干擾性能等方面已不能滿足要求。而用FPGA硬件實(shí)現(xiàn)的數(shù)字濾波器就能很好的解決并行性和速度問題,而且其具有靈活的可配置特性和優(yōu)良的抗干擾能力,因而自適應(yīng)濾波器的FPGA實(shí)現(xiàn)成為近年來數(shù)字濾波器中研究的熱點(diǎn)。Altera公司開發(fā)的DSP Builder可以完成FPGA的DSP系統(tǒng)設(shè)計(jì),它結(jié)合Matlab/Simulink提供的庫(kù)元件和強(qiáng)大的計(jì)算仿真能力,進(jìn)行圖形建模和仿真,還可以完成從Simulink模塊文件向VHDL語(yǔ)言的自動(dòng)轉(zhuǎn)換。

1 算法概述

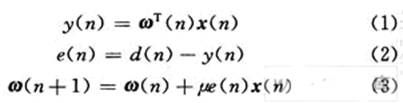

在標(biāo)準(zhǔn)LMS算法中,其迭代公式如下:

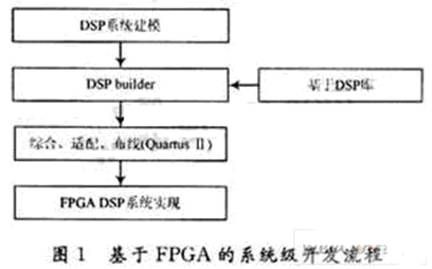

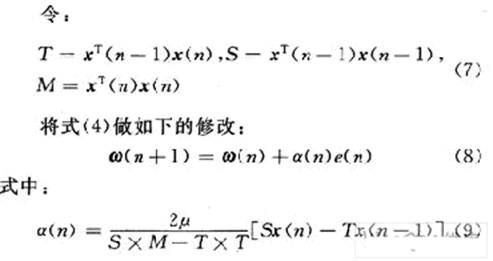

式中:ω(n)為自適應(yīng)濾波器在時(shí)刻n的權(quán)矢量;x(n)為時(shí)刻n的輸入信號(hào)矢量;d(n)為參考信號(hào);e(n)是誤差信號(hào);μ是步長(zhǎng)迭代因子,為了增加LMS算法的收斂速度,文獻(xiàn)[1-4]提出了不同的變步長(zhǎng)算法代替定步長(zhǎng)因子μ,但是很多變步長(zhǎng)因子的計(jì)算量大,存在開方和指數(shù)運(yùn)算,故在能滿足要求的情況下,歸一化LMS (NLMS)依然是一個(gè)很好的選擇,即用μn/[xT(n)x(n)]代替定步長(zhǎng)因子μ為了控制失調(diào),在更新公式中引入一個(gè)固定的收斂因子μn,這是因?yàn)樗械牡箶?shù)都是基于平方誤差的瞬時(shí)值而不是均方誤差(MSE)。對(duì)于NLMS算法,當(dāng)輸入信號(hào)具有強(qiáng)相關(guān)性時(shí),LMS算法及NLMS算法的收斂速度將急劇下降。因此對(duì)進(jìn)入自適應(yīng)濾波器的輸入信號(hào)首先進(jìn)行解相關(guān)預(yù)處理,再對(duì)自適應(yīng)濾波器進(jìn)行歸一化LMS,便得解相關(guān)歸一化LMS(DNLMS)即用式(4)代替式(3):

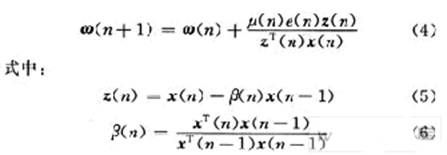

2 基于FPGA的系統(tǒng)開發(fā)流程

在早期PFGA的DSP系統(tǒng)設(shè)計(jì)過程中,DSP開發(fā)者直接使用VHDL或Verilog HDL語(yǔ)音進(jìn)行開發(fā)。這種開發(fā)難度較大,開發(fā)效率較低,為了克服這些問題,出現(xiàn)了許多新的基于FPGA的DSP開發(fā)工具,如Altera公司的DSP Builder、Xilinx公司的System Generator等。圖1是Altera公司的FPGA系統(tǒng)級(jí)開發(fā)流程。

DSP Builder是Altera公司推出的一個(gè)面向DSP開發(fā)的系統(tǒng)級(jí)工具。它是作為Matlab/Simuli-nk的一個(gè)工具箱出現(xiàn)的。它從利用Matlab建立DSP電路模型開始。電路模型可方便地利用Simulink與DSPBuilder中提供的功能模塊和IP核進(jìn)行設(shè)計(jì)。電路中的功能模塊和IP的技術(shù)參數(shù)、數(shù)據(jù)格式、數(shù)據(jù)類型和總線寬度等都能直接設(shè)置。電路模型建立后就能進(jìn)行系統(tǒng)級(jí)的仿真。仿真通過后可以運(yùn)行Signal Compiler,將模型轉(zhuǎn)化成RTL級(jí)的VHDL代碼和Tcl(工具命令語(yǔ)言)腳本語(yǔ)言。調(diào)用QuartusⅡ進(jìn)行編譯,QuartusⅡ根據(jù)網(wǎng)表文件及設(shè)置的優(yōu)化約束條件進(jìn)行布線布局和優(yōu)化設(shè)計(jì)的適配,最后生成編程文件和仿真文件。

3 系統(tǒng)建模與仿真

根據(jù)DNLMS算法的思想,結(jié)合FPGA硬件設(shè)計(jì)的特點(diǎn)。

NLMS算法主要包括延時(shí)模塊,乘法模塊,加法模塊,除法模塊等。為了讓整個(gè)系統(tǒng)看起來清晰,降低原理圖的復(fù)雜性,也便于多次應(yīng)用,本文將幾個(gè)多次使用的模塊封裝成子模塊。下面將對(duì)各個(gè)子模塊作簡(jiǎn)單的介紹。

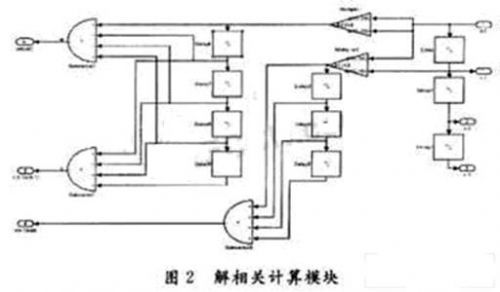

根據(jù)算法的要求,每次新的數(shù)據(jù)x(n)輸入,數(shù)據(jù)T,S,M都需要重新更新一次,計(jì)算量大,消耗的乘法塊多。為了解決這個(gè)問題。根據(jù)T,S,M的運(yùn)算特點(diǎn),每次更新只需要一個(gè)乘法塊和一次加法,就能完成8次乘法和一次加法的運(yùn)算。具體子模塊如圖2所示。

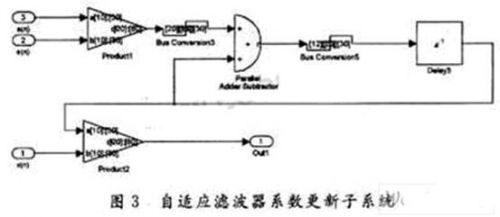

通過圖2的優(yōu)化,對(duì)于8階濾波器,乘法塊的使用從24個(gè)減少到2個(gè),計(jì)算速度將得到很大的提高。ω的迭代運(yùn)算通過圖3實(shí)現(xiàn)。

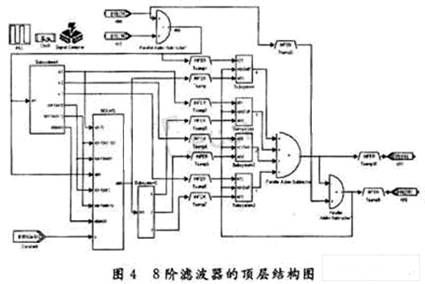

在頂層模塊的設(shè)計(jì)中,加入了PLL模塊和SignalComplier,根據(jù)各模塊仿真周期,在PLL模塊中設(shè)置好不同的周期,利用Simulink中的顏色標(biāo)識(shí)采樣頻率的高低。頂層文件的設(shè)計(jì)如圖4所示。

在頂層結(jié)構(gòu)圖中,子模塊8為方程(9)的實(shí)現(xiàn)過程。

4 計(jì)算機(jī)仿真

為了充分模擬相關(guān)性較強(qiáng)的信號(hào),在輸入端加如下的信號(hào)源:

x(n)=0.99x(n-1)+v(n)

式中:v(n)為高斯白噪聲;x(n)的初始值為500,具體的產(chǎn)生電路如圖5所示。

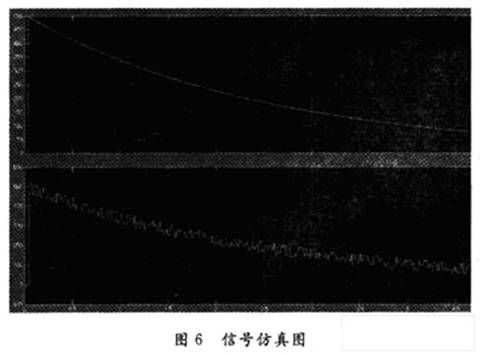

信號(hào)產(chǎn)生波形以及加噪后的仿真波形如圖6所示。

通過濾波器濾波的結(jié)果如圖7所示。

在圖7的信號(hào)依次為參考信號(hào)、加噪聲信號(hào)、誤差信號(hào)和濾波信號(hào)。濾波效果良好,對(duì)于強(qiáng)相關(guān)的信號(hào),也有很好的濾波效果。通過QuartusⅡ編譯,濾器器的速度為35.24 MHz,編譯后生產(chǎn)如圖8所示的塊,它作為一個(gè)符號(hào)模塊可供更高級(jí)系統(tǒng)設(shè)計(jì)時(shí)調(diào)用,通過對(duì)該塊的修改和增加濾波器的階數(shù),可以實(shí)現(xiàn)對(duì)語(yǔ)音的回聲消除。

5 結(jié) 語(yǔ)

自適應(yīng)濾波器的研究是近年來研究的熱門方向,在PFGA中實(shí)現(xiàn)高速的自適應(yīng)濾波器的設(shè)計(jì)更是一個(gè)熱點(diǎn),在此采用DSP Builder系統(tǒng)建模的方法,在FPGA中實(shí)現(xiàn)了歸一化LMS算法,實(shí)驗(yàn)結(jié)果表明:用DSPBuilder設(shè)計(jì)的8階DNLMS算法比用底層的VHDL代碼設(shè)計(jì)效率更高,靈活性更大,速度更快。同樣比通用的DSP芯片設(shè)計(jì)的8階NLMS濾波器處理速度快了20多倍。如果將8階NLMS濾波器擴(kuò)展到512階或者1 024階,可以很好地應(yīng)用于自適應(yīng)回聲消除等很多自適應(yīng)濾波的領(lǐng)域。故有一定的參考價(jià)值。