l 引 言

由于GMSK調(diào)制方式具有很好的功率頻譜特性,較優(yōu)的誤碼性能,能夠滿足移動(dòng)通信環(huán)境下對(duì)鄰道干擾的嚴(yán)格要求,因此成為GSM、ETS HiperLANl以及GPRS等系統(tǒng)的標(biāo)準(zhǔn)調(diào)制方式。

目前GMSK調(diào)制技術(shù)主要有兩種實(shí)現(xiàn)方法,一種是利用GMSK ASIC專用芯片來(lái)完成,典型的產(chǎn)品如FX589或CMX909配合MC2833或FX019來(lái)實(shí)現(xiàn)GMSK調(diào)制。這種實(shí)現(xiàn)方法的特點(diǎn)是實(shí)現(xiàn)簡(jiǎn)單、基帶信號(hào)速率可控,但調(diào)制載波頻率固定,沒(méi)有可擴(kuò)展性。另外一種方法是利用軟件無(wú)線電思想采用正交調(diào)制的方法在FPGA和DSP平臺(tái)上實(shí)現(xiàn)。其中又包括兩種實(shí)現(xiàn)手段,一種是采用直接分解將單個(gè)脈沖的高斯濾波器響應(yīng)積分分成暫態(tài)部分和穩(wěn)態(tài)部分,通過(guò)累加相位信息來(lái)實(shí)現(xiàn);另一種采用頻率軌跡合成,通過(guò)采樣把高斯濾波器矩形脈沖響應(yīng)基本軌跡存入ROM作為查找表,然后通過(guò)FM調(diào)制實(shí)現(xiàn)。這種利用軟件無(wú)線電思想實(shí)現(xiàn)GMSK調(diào)制的方法具有調(diào)制參數(shù)可變的優(yōu)點(diǎn),但由于軟件設(shè)計(jì)中涉及到高斯低通濾波、相位積分和三角函數(shù)運(yùn)算,所以調(diào)制器參數(shù)更改困難、實(shí)現(xiàn)復(fù)雜。綜上所述,本文提出一種基于CMX589A和FPGA的GMSK調(diào)制器設(shè)計(jì)方案。與傳統(tǒng)實(shí)現(xiàn)方法比較具有實(shí)現(xiàn)簡(jiǎn)單、調(diào)制參數(shù)方便可控和軟件剪裁容易等特點(diǎn),適合于CDPD、無(wú)中心站等多種通信系統(tǒng),具有重要現(xiàn)實(shí)意義。

2 系統(tǒng)硬件設(shè)計(jì)

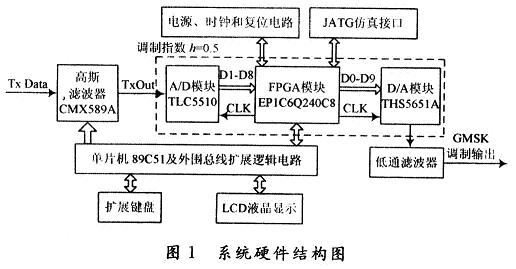

系統(tǒng)的硬件主要包括三部分:?jiǎn)纹瑱C(jī)控制器及其外圍擴(kuò)展鍵盤和液晶顯示模塊、高斯濾波器模塊,以及FPGA調(diào)制器模塊,系統(tǒng)硬件結(jié)構(gòu)圖如圖1所示。

系統(tǒng)工作過(guò)程如下:系統(tǒng)加電后,F(xiàn)PGA完成初始化,LCD界面提示用戶輸入控制信息,同時(shí)系統(tǒng)輸出固定頻率的正弦載波,表明系統(tǒng)正常工作;用戶通過(guò)控制菜單的提示,從鍵盤輸入控制信息(例如基帶信號(hào)的碼元速率,高斯濾波器的系統(tǒng)參數(shù),BT值以及調(diào)制器的載波頻率等);控制信息通過(guò)主控制器發(fā)送給高斯濾波模塊及調(diào)制器模塊;FPGA調(diào)制器模塊根據(jù)接收到A/D轉(zhuǎn)換器的輸入信號(hào)的幅度值控制頻率字從而完成對(duì)于基帶信號(hào)的調(diào)制。

2.1 高斯濾波器模塊設(shè)計(jì)

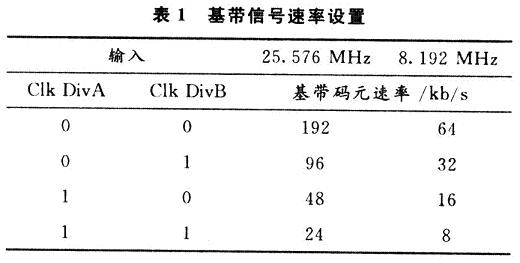

高斯濾波器模塊采用CML公司生產(chǎn)的CMX589A專用集成芯片,具有較寬的基帶信號(hào)接收速率。在本設(shè)計(jì)中,為CMX589A提供兩種頻率的外部晶振,分別為25.576 MHz和8.192 MHz,通過(guò)跳線控制。CMX589A的控制引腳與單片機(jī)的P2口相連來(lái)控制濾波器的參數(shù),其中ClkDivA、ClkDivB與外部時(shí)鐘配合共同決定高斯濾波器的基帶碼元速率,設(shè)置如表1所示。BT引腳控制高斯濾波器的系統(tǒng)帶寬,當(dāng)設(shè)置為“l”時(shí),系統(tǒng)BT值為O.5;當(dāng)設(shè)置為“O”時(shí),BT值為O.3。高斯濾波器的工作過(guò)程為:首先根據(jù)不同系統(tǒng)的需要來(lái)設(shè)置濾波器的基帶碼元速率和帶寬BT值,然后在Tx Data引腳接入需要調(diào)制的基帶碼元信號(hào),同時(shí)給Tx Enable置高電平,通過(guò)TxOut就可以接收到高斯濾波基帶信號(hào)。

2.2 調(diào)制指數(shù)為O.5的FM發(fā)射機(jī)設(shè)計(jì)

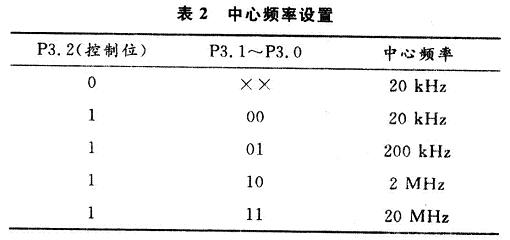

調(diào)頻發(fā)射機(jī)由FPGA配合A/D、D/A來(lái)實(shí)現(xiàn)。FPGA選用Cyclone系列EPlC6Q240C8,它是采用SRAM工藝制造的混合低電壓FPGA芯片。A/D采用TI公司生產(chǎn)的8位模數(shù)轉(zhuǎn)換器TLC5510,D/A則采用10位數(shù)模轉(zhuǎn)換器THS5651A,用以完成高速率數(shù)據(jù)轉(zhuǎn)換。調(diào)頻發(fā)射機(jī)的系統(tǒng)時(shí)鐘為20 MHz,同時(shí)提供給D/A THS565lA作為轉(zhuǎn)換時(shí)鐘。A/D轉(zhuǎn)換時(shí)鐘由FPGA提供,系統(tǒng)時(shí)鐘經(jīng)過(guò)分頻提供給A/D轉(zhuǎn)換器1 MHz的工作時(shí)鐘。同時(shí)單片機(jī)的P3口通過(guò)2 b的頻率控制位與1 b的“使能”控制位與FPGA相連來(lái)控制調(diào)制器的4種中心頻率,分別為20 kHz,200 kHz,2 MHz和20 MHz,中心頻率設(shè)置如表2所示。當(dāng)載波的中心頻率設(shè)置為20 MHz的時(shí)候,系統(tǒng)工作時(shí)鐘需要通過(guò)FPGA內(nèi)部的PLL倍頻實(shí)現(xiàn)。

2.3 單片機(jī)控制器設(shè)計(jì)

控制器采用AT89C51單片機(jī),外擴(kuò)LCD,4*4矩陣鍵盤,并通過(guò)接口與單片機(jī)的P0和P1相連,單片機(jī)的P2口與高斯濾波器的控制線相連,P3口與FPGA相連控制發(fā)射機(jī)的中心頻率。

鍵盤處理及LCD顯示模塊:利用鍵盤實(shí)現(xiàn)人機(jī)接口,該模塊包括鍵盤的掃描、去抖、連擊以及功能鍵的信號(hào)處理。用戶根據(jù)需要來(lái)調(diào)整系統(tǒng)參數(shù),并通過(guò)與LCD顯示器的結(jié)合來(lái)顯示當(dāng)前調(diào)制信號(hào)的各種參數(shù),從而使系統(tǒng)更具可操作性。

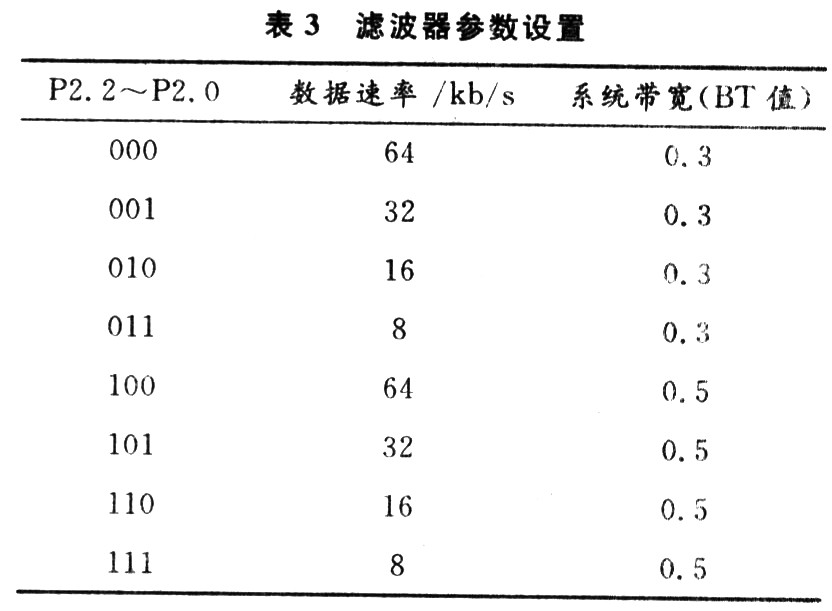

功能參數(shù)設(shè)置模塊:此模塊負(fù)責(zé)處理鍵盤的輸入數(shù)據(jù),根據(jù)用戶指令選擇相應(yīng)的系統(tǒng)參數(shù)(例如基帶信號(hào)的碼元速率、FM調(diào)制器的中心頻率等)。表3表示在高斯濾波器模塊工作時(shí)鐘為8.192 MHz時(shí),單片機(jī)控制濾波器系統(tǒng)參數(shù)設(shè)置。

3 系統(tǒng)軟件設(shè)計(jì)

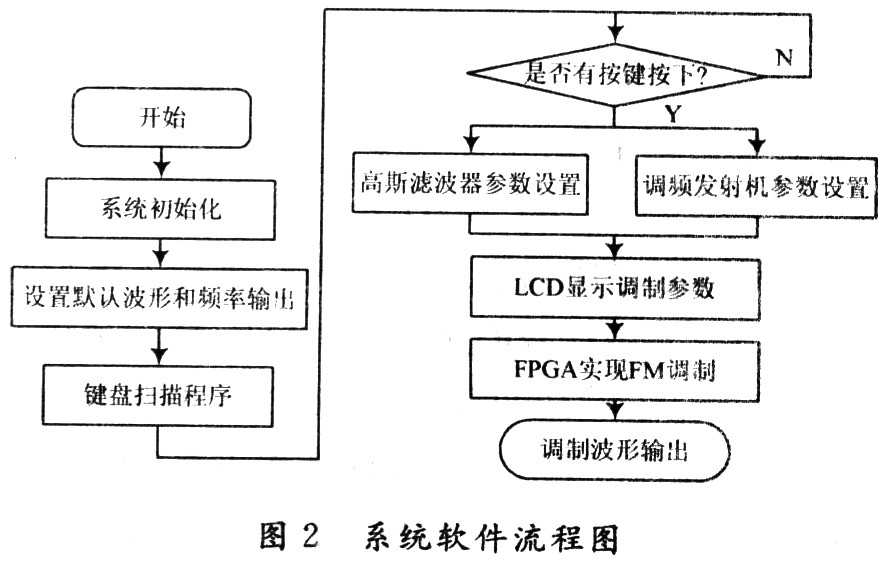

系統(tǒng)的軟件編程主要包括兩部分:?jiǎn)纹瑱C(jī)控制模塊和FPGA實(shí)現(xiàn)調(diào)制指數(shù)為O.5的FM調(diào)制器模塊。系統(tǒng)的軟件流程圖如圖2所示。

3.1 單片機(jī)軟件設(shè)計(jì)

控制模塊主要包括擴(kuò)展矩陣鍵盤、LCD液晶顯示、調(diào)制器參數(shù)控制。

單片機(jī)控制器的系統(tǒng)工作過(guò)程如下:

單片機(jī)初始化,LCD顯示開(kāi)始菜單,包括“高斯濾波器參數(shù)設(shè)置”和“FM調(diào)制器參數(shù)設(shè)置”兩個(gè)選項(xiàng);

進(jìn)入“高斯濾波器參數(shù)設(shè)置”子菜單,包括“系統(tǒng)帶寬設(shè)置”和“基帶碼元速率設(shè)置”,分別可以設(shè)置2種不同的濾波器帶寬和8種基帶碼元速率,單片機(jī)根據(jù)系統(tǒng)設(shè)置在P2端口輸出控制信息;

進(jìn)入“調(diào)制器參數(shù)設(shè)置”的子菜單以設(shè)置“調(diào)制載波的中心頻率”,可以設(shè)定四種不同的載波中心頻率,并通過(guò)單片機(jī)P3口控制FPGA的調(diào)制載波的中心頻率。

3.2 調(diào)制器的系統(tǒng)實(shí)現(xiàn)

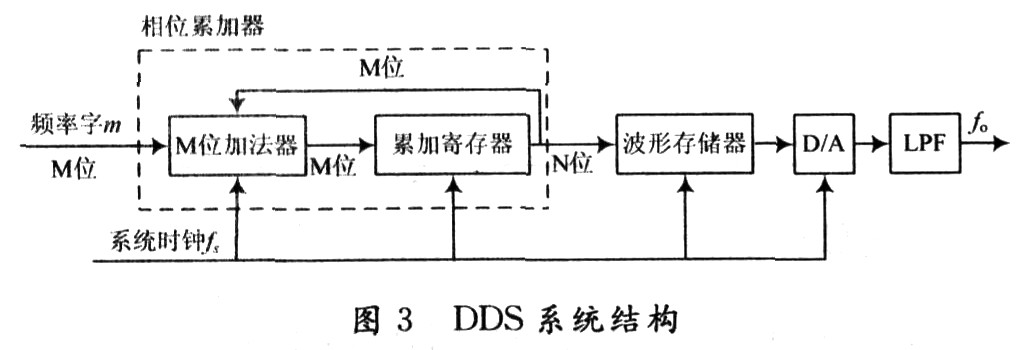

FM調(diào)制器采用DDS思想在FPGA平臺(tái)上實(shí)現(xiàn)。DDS(Direct Digital Frequency Synthesizer,直接數(shù)字頻率合成)是一種新型的頻率合成技術(shù),具有較高的頻率分辨率,可以實(shí)現(xiàn)快速的頻率切換。DDS系統(tǒng)主要由系統(tǒng)時(shí)鐘源、相位累加器、正弦波查找表、D/A轉(zhuǎn)換器和低通補(bǔ)償濾波器組成,系統(tǒng)結(jié)構(gòu)如圖3所示。其中相位累加器是DDS系統(tǒng)的核心,它由N位加法器和N位相位寄存器組成。每來(lái)一位參考時(shí)鐘脈沖,N位加法器將頻率控制字和累積器的相位輸出相加,把相加的結(jié)果送到相位寄存器的輸入端。相位寄存器一方面將輸出的相位數(shù)據(jù)反饋到加法器的輸入端,以使加法器繼續(xù)在時(shí)鐘脈沖的作用下繼續(xù)與頻率控制字相加,另一方面又將輸出的相位數(shù)據(jù)又作為波形存儲(chǔ)表的地址輸入。波形存儲(chǔ)表把輸入的地址相位信息映射成波形數(shù)據(jù),最后經(jīng)過(guò)DAC和低通濾波器得到模擬信號(hào)。

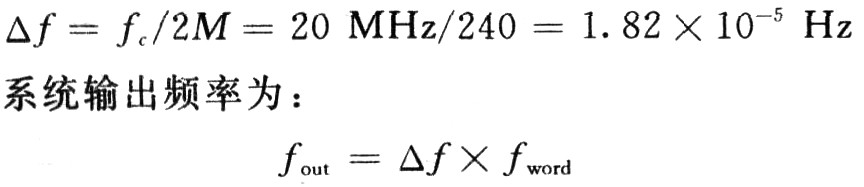

本設(shè)計(jì)采用20 MHz外部晶振作為時(shí)鐘源,系統(tǒng)采用40位相位累加器,故頻率字也取40位,所以系統(tǒng)的頻率分辨率如下式所示:

FM調(diào)制器完成幅度到頻率的轉(zhuǎn)換是系統(tǒng)設(shè)計(jì)的關(guān)鍵。例如設(shè)定基帶信號(hào)的速率為8 kHz,載波的中心頻率為200 kHz(fword=“10995116277”),為了實(shí)現(xiàn)調(diào)制指數(shù)為0.5的FM調(diào)制器,F(xiàn)M調(diào)制器的頻率差為4 kHz。FPGA根據(jù)8位A/D轉(zhuǎn)換器輸入的信號(hào)幅度值選擇相應(yīng)的頻率字,從而控制輸出信號(hào)的頻率完成調(diào)頻功能。載波的中心頻率對(duì)應(yīng)的A/D轉(zhuǎn)換器中心幅值a in=“10000 0000”;當(dāng)A/D轉(zhuǎn)換器輸入為O V(即a in=“0000 0000”)時(shí),對(duì)應(yīng)的調(diào)制信號(hào)的輸出頻率為198 kHz(fword=“10885165114”);當(dāng)A/D轉(zhuǎn)換器的輸入為滿刻度2 V(ain=“1111 1111”)時(shí),調(diào)制輸出頻率為202 kHz(fword=“11105067440”)。把頻率從198 kHz到202 kHz等分成255份,把相應(yīng)的頻率轉(zhuǎn)換成40位頻率字,則A/D轉(zhuǎn)換器的256個(gè)幅值與256個(gè)頻率字一一對(duì)應(yīng)。在每一個(gè)系統(tǒng)時(shí)鐘周期,頻率控制字與40位的相位累加器的值相加結(jié)果存入相位累加器。由于選用的ROM查找表的地址線為10位,所以取相位累加器的高10位作為正弦查找表的地址。正弦查找表利用Cyclone內(nèi)部的ROM模塊完成查找表的設(shè)計(jì),字長(zhǎng)為10位,與所選用的DAC的數(shù)據(jù)位數(shù)相匹配。

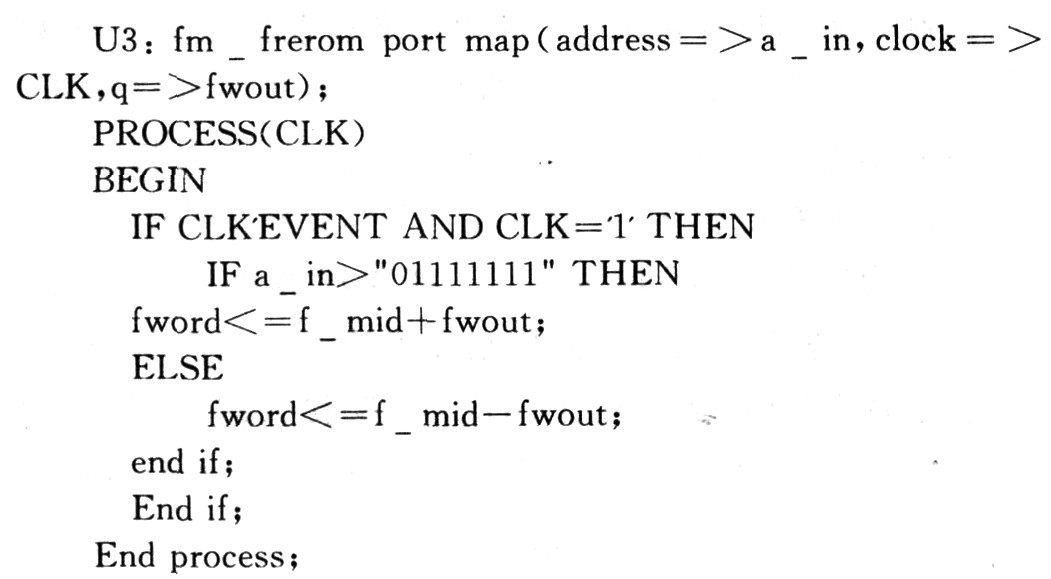

系統(tǒng)輸入信號(hào)的幅度與頻率字轉(zhuǎn)換的核心代碼如下:

其中,f_mid為調(diào)制信號(hào)的中心頻率,fm_frerom為A/D輸入的信號(hào)幅度值與頻偏之間的映射關(guān)系,系統(tǒng)根據(jù)接收到信號(hào)的幅度值相應(yīng)改變調(diào)制信號(hào)的頻偏從而完成調(diào)制功能。

4 系統(tǒng)軟件仿真及測(cè)試

4.1 軟件仿真

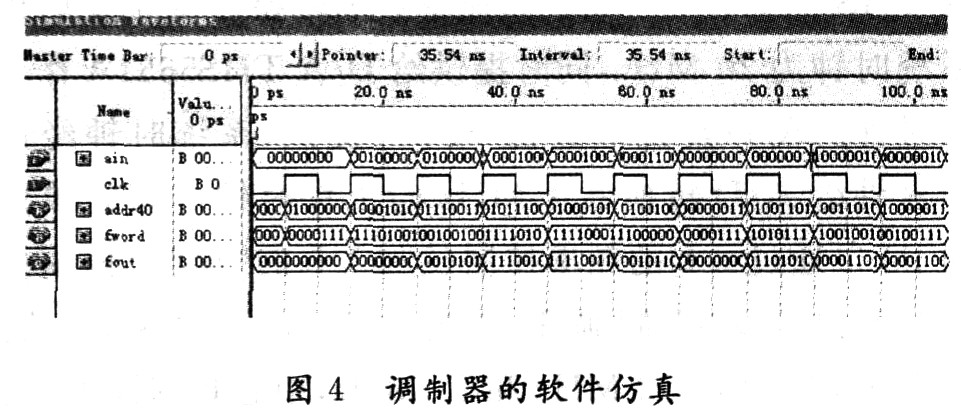

本設(shè)計(jì)利用EDA工具QuartusⅡ6.O完成調(diào)制器軟件編程,通過(guò)編譯環(huán)境進(jìn)行軟件仿真如圖4所示,其中clk為系統(tǒng)晶振時(shí)鐘,addr40為相位累加器,a_in為A/D的轉(zhuǎn)換器的8位輸出信號(hào),fword為系統(tǒng)頻率字,fout為波表輸出的調(diào)制信號(hào)幅度值。

4.2 系統(tǒng)測(cè)試與分析

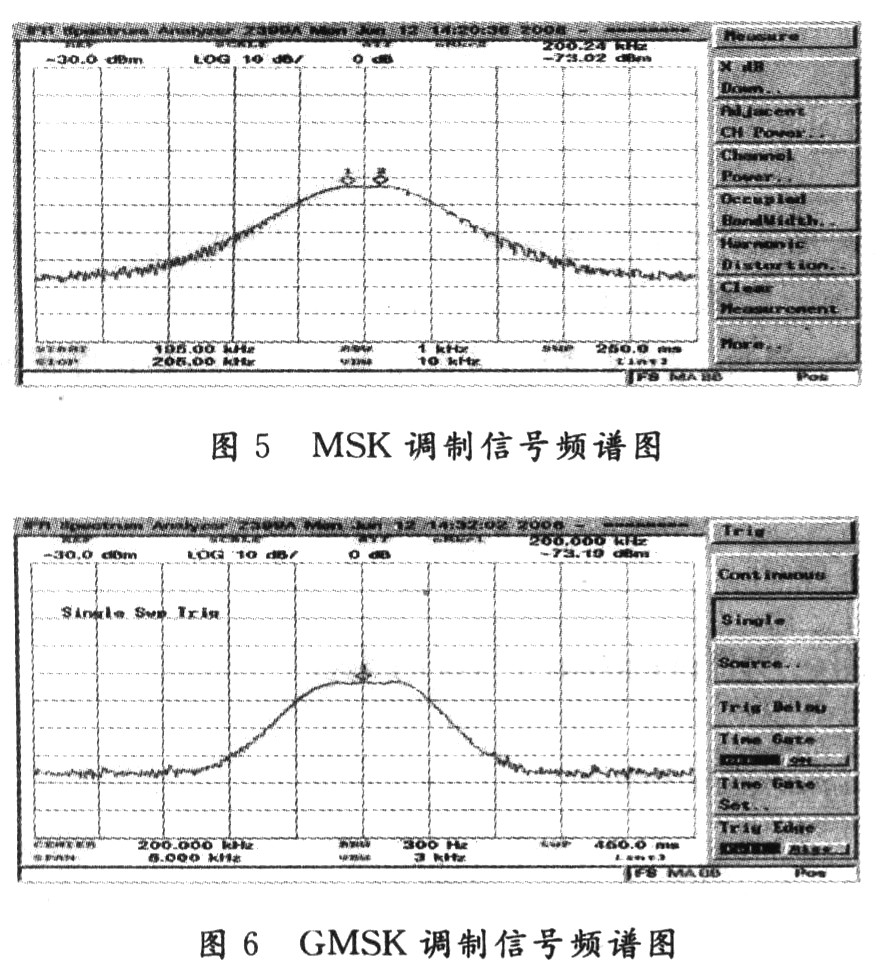

系統(tǒng)測(cè)試通過(guò)IFR2399A頻譜儀來(lái)完成系統(tǒng)的硬件測(cè)試。圖5表示在相同的硬件平臺(tái)上實(shí)現(xiàn)MSK調(diào)制的頻譜圖,圖6表示GMSK調(diào)制的頻譜圖。對(duì)比兩個(gè)圖可以發(fā)現(xiàn),由于加入了高斯濾波器,GMSK的頻譜更加緊湊,帶外衰減也要快于MSK。同時(shí)由測(cè)試結(jié)果可以看出,中頻載波為200 kHz,主瓣寬度以及衰減狀況等與理論分析結(jié)果相符。

5 結(jié) 語(yǔ)

本文實(shí)現(xiàn)了一種基于CMX589A和FPGA的GMSK調(diào)制器。系統(tǒng)采用了主從式的結(jié)構(gòu),主控機(jī)由單片機(jī)實(shí)現(xiàn)對(duì)于GMSK調(diào)制器系統(tǒng)參數(shù)的控制,CMX589A模塊完成基帶信號(hào)高斯濾波,F(xiàn)M調(diào)制器采用直接數(shù)字頻率合成技術(shù)(DDS)在FPGA硬件平臺(tái)上實(shí)現(xiàn)、系統(tǒng)最高輸出頻率為25 MHz。同時(shí)系統(tǒng)具有很寬的基帶信號(hào)數(shù)據(jù)和調(diào)制參數(shù)靈活可控等特點(diǎn),并且克服了正交調(diào)制方案中嚴(yán)格正交載波產(chǎn)生困難的缺陷。測(cè)試結(jié)果表明,已調(diào)信號(hào)包絡(luò)恒定,頻譜滿足設(shè)計(jì)要求,適用于CDPD,無(wú)中心站等多種通信系統(tǒng)。