RFID技術(shù)(radio frequency identification)是一種非接觸式智能識別技術(shù),它通過射頻信號自動識別目標對象并獲得相關(guān)信息。整個識別過程無需人工介入,可同時識別多個對象并可以識別高速運動的物體,操作簡單,廣泛應(yīng)用在車輛自動識別系統(tǒng)、物流管理與監(jiān)控、倉庫管理、門禁系統(tǒng)以及軍事等領(lǐng)域。

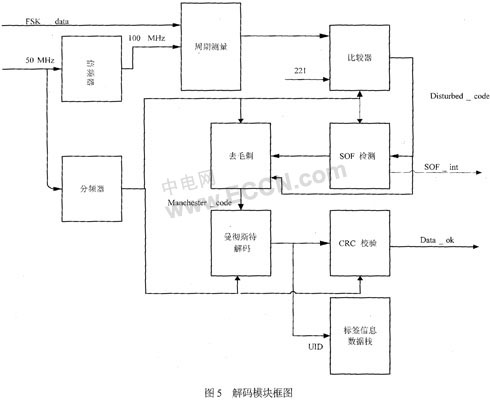

RFID系統(tǒng)由三部分組成:讀頭、天線和電子標簽,如圖1所示。

其中讀頭是整個系統(tǒng)的核心部分,控制整個識別過程中與標簽之間的通信,并提供與后臺計算機的接口。天線用來發(fā)送射頻信號給電子標簽,并把電子標簽響應(yīng)的數(shù)據(jù)接收回來。電子標簽存儲著目標的信息,它進入識別區(qū)域時被天線發(fā)送的射頻信號激活,然后向讀頭返回應(yīng)答,從而完成一次識別。

本文要介紹的解碼模塊是基于ISO/IEC15693標準設(shè)計的,實現(xiàn)了從帶干擾的返回信號(此信號已經(jīng)去掉載波)中精確的提取標簽信息的功能。此設(shè)計直接影響識別的準確性。

1 ISO/IEC15693協(xié)議

ISO/IEC15693協(xié)議是國際化標準組織制定的關(guān)于射頻識別技術(shù)的一項標準,工作頻率為13.56MHz,電子標簽屬于無源標簽。協(xié)議詳細描述了射頻識別技術(shù)的信號調(diào)制方式、讀頭向標簽發(fā)送數(shù)據(jù)的編碼方式、標簽返回數(shù)據(jù)的編碼方式以及各種指令包格式和應(yīng)答包格式。協(xié)議還介紹了電子標簽的防沖撞機制。本文中的標簽返回數(shù)據(jù)的解碼模塊就是以此協(xié)議為基準設(shè)計的,下面詳細介紹標簽向讀頭返回數(shù)據(jù)的格式。

電子標簽首先將原始數(shù)據(jù)(digital bits,即要返回的標簽信息)進行曼徹斯特編碼(manchester bits),然后再用編碼后的數(shù)據(jù)信息以FSK方式調(diào)制到低速率的子載波423.75kHz和484.28kHz信號上(RF Bits FSK),即曼徹斯特碼的高電平部分使用484.28kHz方波信號表示,低電平部分使用423.75kHz方波信號表示。最后再由子載波調(diào)制到13.56MHz的載波上,以此方式回傳給讀頭。返回信號編碼及子載波形式如圖2所示。

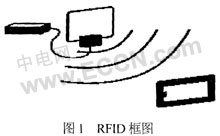

為了達到數(shù)據(jù)的傳輸同步,電子標簽在曼徹斯特碼的起始和結(jié)尾分別加入幀頭和幀尾,幀頭部分為11100010,用423.75kHz和484.28kHz信號調(diào)制后如圖3所示。幀尾部分為01000111,與幀頭的順序完全相反,調(diào)制后如圖4所示。

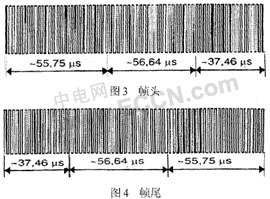

2 解碼模塊的結(jié)構(gòu)及其實現(xiàn)原理

整個讀頭的結(jié)構(gòu)由模擬電路部分和數(shù)字電路部分組成。模擬電路的作用是產(chǎn)生13.56MHz的載波信號、調(diào)制發(fā)送信號和解調(diào)返回信號。數(shù)字電路部分負責數(shù)字信號的編解碼。FPGA是數(shù)字電路部分的核心,理想情況下返回信號經(jīng)過模擬電路解調(diào)到達FPGA后,其數(shù)據(jù)格式如圖2中RF Bits FSK所示。但在射頻信號傳輸過程中和模擬電路的解測過程中都難免有噪聲干擾,進入FPGA的信號實際上是帶干擾FSK信號。因此必須在解碼模塊中對干擾加以消除,否則會大大降低電子標簽的識別成功率。解碼模塊共分為八個部分,如圖5所示,下面將對這些模塊的功能進行具體介紹。