??? 摘 要: 針對(duì)某型脈沖對(duì)多普勒雷達(dá)的信號(hào)處理要求,設(shè)計(jì)了一種全數(shù)字化信號(hào)處理機(jī)" title="信號(hào)處理機(jī)">信號(hào)處理機(jī)。該信號(hào)處理機(jī)采用“ADC+FPGA+DSP+存儲(chǔ)器”結(jié)構(gòu),具有體積小、重量輕、功耗低、可靠性高等優(yōu)點(diǎn)。重點(diǎn)討論了信號(hào)處理中數(shù)據(jù)采集、脈沖積累及目標(biāo)檢測(cè)的方法和實(shí)現(xiàn)。

??? 關(guān)鍵詞: 脈沖多普勒雷達(dá);信號(hào)處理機(jī);數(shù)據(jù)采集;恒虛警檢測(cè)

?

??? 多普勒雷達(dá)的主要功能就是在雜波背景下測(cè)量運(yùn)動(dòng)目標(biāo)" title="運(yùn)動(dòng)目標(biāo)">運(yùn)動(dòng)目標(biāo)[1]。其基本原理是利用運(yùn)動(dòng)目標(biāo)和背景雜波相對(duì)于雷達(dá)的徑向速度不同而產(chǎn)生的多普勒頻率不同,從而在雷達(dá)回波中區(qū)分運(yùn)動(dòng)目標(biāo)。脈沖多普勒雷達(dá)發(fā)射信號(hào)為脈沖串,其回波信號(hào)也為脈沖串。雷達(dá)信號(hào)處理機(jī)實(shí)現(xiàn)目標(biāo)檢測(cè)和目標(biāo)多普勒信號(hào)的提取。隨著大規(guī)模集成電路的發(fā)展,高速高精度的ADC轉(zhuǎn)換器件、大規(guī)模FPGA以及高性能數(shù)字信號(hào)" title="數(shù)字信號(hào)">數(shù)字信號(hào)處理器(DSP)日益普及,采用數(shù)字技術(shù)實(shí)現(xiàn)雷達(dá)信號(hào)處理得到了廣泛應(yīng)用。雷達(dá)數(shù)字信號(hào)處理機(jī)通常采用ADC轉(zhuǎn)換器將雷達(dá)回波信號(hào)轉(zhuǎn)換為數(shù)字信號(hào),利用FFT運(yùn)算實(shí)現(xiàn)多普勒濾波器組,然后利用恒虛警檢測(cè)" title="恒虛警檢測(cè)">恒虛警檢測(cè)原理實(shí)現(xiàn)運(yùn)動(dòng)目標(biāo)的檢測(cè)[2]。

1 信號(hào)處理機(jī)設(shè)計(jì)要求和基本組成

??? 本文設(shè)計(jì)的脈沖多普勒雷達(dá)數(shù)字信號(hào)處理機(jī)為某型號(hào)對(duì)海矢量脫靶量測(cè)量雷達(dá)專用信號(hào)處理機(jī),其性能直接影響雷達(dá)的測(cè)量精度。信號(hào)處理機(jī)設(shè)計(jì)不僅要滿足信號(hào)處理的精度和實(shí)時(shí)性要求,還要綜合考慮整個(gè)信號(hào)處理機(jī)的低功耗、可重構(gòu)性及可靠性。

??? 本文設(shè)計(jì)的信號(hào)處理機(jī)的基本功能是:將多路雷達(dá)接收機(jī)輸出的I、Q視頻信號(hào)按距離波門進(jìn)行模數(shù)轉(zhuǎn)換變?yōu)閿?shù)字信號(hào)并進(jìn)行脈沖積累提高信噪比,然后從中檢測(cè)運(yùn)動(dòng)目標(biāo),根據(jù)檢測(cè)結(jié)果錄取目標(biāo)過靶前后的回波信號(hào),通過數(shù)據(jù)傳輸接口將錄取的數(shù)據(jù)傳輸?shù)綌?shù)據(jù)處理計(jì)算機(jī),還能接收遙控指令,控制處理機(jī)的工作模式。

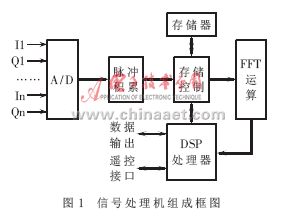

??? 信號(hào)處理機(jī)采用“ADC+FPGA+DSP+存儲(chǔ)器”結(jié)構(gòu)實(shí)現(xiàn),由ADC轉(zhuǎn)換、脈沖積累、存儲(chǔ)控制" title="存儲(chǔ)控制">存儲(chǔ)控制、FFT運(yùn)算、DSP以及遙控接口和數(shù)據(jù)傳輸接口等部分電路組成,如圖1所示。其中脈沖積累、存儲(chǔ)控制、FFT運(yùn)算由FPGA實(shí)現(xiàn)。DSP處理器除了完成恒虛警目標(biāo)檢測(cè)功能外,還作為整個(gè)處理機(jī)的總控制器控制處理機(jī)各部分的工作。信號(hào)處理機(jī)采用的數(shù)據(jù)流驅(qū)動(dòng)方式進(jìn)行流水處理,各組成部分也分別采用流水方式工作,保證了信號(hào)處理機(jī)的實(shí)時(shí)性。

?????????????????????

????這種實(shí)現(xiàn)方案既能滿足信號(hào)處理的高速度和高精度的要求,且具有一定的靈活性和可擴(kuò)展性,同時(shí)還能滿足系統(tǒng)的功耗、體積、重量和可靠性要求。

2 信號(hào)處理機(jī)的設(shè)計(jì)與實(shí)現(xiàn)

2.1 ADC轉(zhuǎn)換電路設(shè)計(jì)

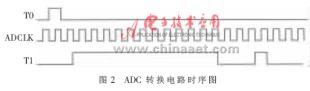

??? ADC轉(zhuǎn)換電路負(fù)責(zé)將雷達(dá)接收機(jī)輸出的目標(biāo)回波I/Q視頻信號(hào)轉(zhuǎn)換為數(shù)字信號(hào)。雷達(dá)采用脈沖多普勒體制,雷達(dá)發(fā)射脈沖寬度為200ns,為了保證在每個(gè)距離波門都能采到一點(diǎn),ADC轉(zhuǎn)換時(shí)鐘至少為5MHz,且與發(fā)射脈沖嚴(yán)格同步,以保證各距離波門的采樣位置相對(duì)發(fā)射脈沖的延時(shí)一致。采樣時(shí)鐘的相位可以在一定范圍內(nèi)調(diào)整,以控制采樣時(shí)刻相對(duì)發(fā)射脈沖的延時(shí)。本雷達(dá)作用距離為360m,另外為了進(jìn)行接收機(jī)狀態(tài)在線監(jiān)測(cè)和校準(zhǔn),還在有效作用距離外發(fā)送參考信號(hào),因此在進(jìn)行數(shù)據(jù)鎖存時(shí),需要將發(fā)射脈沖后12個(gè)采樣脈沖以及參考信號(hào)所在波門的數(shù)據(jù)進(jìn)行鎖存。ADC轉(zhuǎn)換電路時(shí)序如圖2所示。其中T0為發(fā)射脈沖同步信號(hào),ADCLK為采樣時(shí)鐘,T1為數(shù)據(jù)鎖存控制信號(hào)。T1信號(hào)前一個(gè)脈沖寬2 400ns,用于鎖存有效作用距離內(nèi)的回波采樣信號(hào);后一個(gè)脈沖寬200ns,用于鎖存參考信號(hào)采樣。ADCLK和T1由接收機(jī)輸出60MHz時(shí)鐘分頻產(chǎn)生,該時(shí)鐘與T0嚴(yán)格同步。ADCLK與T1相對(duì)于T0的延時(shí)通過控制分頻器的起始相位進(jìn)行調(diào)整,以確定距離波門的采樣位置。

?

2.2 脈沖積累電路設(shè)計(jì)

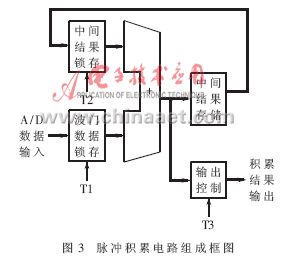

?? ?脈沖積累電路負(fù)責(zé)將ADC轉(zhuǎn)換的結(jié)果按距離波門進(jìn)行可變次數(shù)的積累,以提高回波信號(hào)的信噪比。由于雷達(dá)脈沖重復(fù)頻率遠(yuǎn)大于目標(biāo)多普勒信號(hào)頻率,在不發(fā)生模糊的條件下,脈沖積累不但提高回波信號(hào)的信噪比,而且能降低實(shí)際輸出數(shù)據(jù)的采樣率,從而降低信號(hào)處理的速度和存儲(chǔ)量要求。脈沖積累電路功能為:在每個(gè)脈沖積累周期內(nèi),對(duì)每個(gè)發(fā)射脈沖回波信號(hào)按距離波門將ADC轉(zhuǎn)換數(shù)據(jù)依次進(jìn)行累加,并將累加結(jié)果輸出到存儲(chǔ)控制電路。脈沖積累電路由數(shù)據(jù)輸入控制器、累加器、中間結(jié)果存儲(chǔ)器以及輸出控制器組成。其組成如圖3所示。

?

??? 脈沖積累時(shí)序如圖4所示。其中T1為距離波門鎖存信號(hào),負(fù)責(zé)按距離波門鎖存ADC轉(zhuǎn)換數(shù)據(jù),讀取中間結(jié)果,并將累加結(jié)果存儲(chǔ)至中間結(jié)果存儲(chǔ)器;T2為累加起始控制信號(hào),用于清零中間結(jié)果鎖存器,開始新的積累過程;T3為輸出控制信號(hào),用于積累結(jié)束后將累加輸出至存儲(chǔ)控制器。通過調(diào)整T2和T3的位置則可獲得不同的積累次數(shù)。

2.3 存儲(chǔ)控制電路設(shè)計(jì)

??? 存儲(chǔ)控制電路負(fù)責(zé)將經(jīng)過ADC轉(zhuǎn)換和脈沖積累的雷達(dá)回波信號(hào)分別送入數(shù)據(jù)存儲(chǔ)器和FFT處理器,且能在DSP處理器的控制下將存儲(chǔ)器中的存儲(chǔ)結(jié)果輸出。存儲(chǔ)控制電路由用于產(chǎn)生存儲(chǔ)數(shù)據(jù)地址的存儲(chǔ)地址產(chǎn)生器和用于控制數(shù)據(jù)存儲(chǔ)器總線控制權(quán)的總線切換電路組成。

??? 數(shù)據(jù)存儲(chǔ)階段,存儲(chǔ)地址產(chǎn)生器控制數(shù)據(jù)存儲(chǔ)器的總線,將輸出進(jìn)行存儲(chǔ)。數(shù)據(jù)輸出階段,則通過總線切換將數(shù)據(jù)存儲(chǔ)器的總線控制權(quán)交由DSP控制,DSP將數(shù)據(jù)讀出并通過數(shù)據(jù)輸出接口輸出。

??? 為了正確保存目標(biāo)過靶前后的回波數(shù)據(jù),數(shù)據(jù)存儲(chǔ)采用循環(huán)存儲(chǔ)方式,即在檢測(cè)到目標(biāo)前,數(shù)據(jù)在存儲(chǔ)器中按一定格式順序存儲(chǔ),存儲(chǔ)到存儲(chǔ)器末地址后,則回到存儲(chǔ)器首地址繼續(xù)存儲(chǔ)數(shù)據(jù);當(dāng)檢測(cè)到目標(biāo)后,繼續(xù)存儲(chǔ)一定數(shù)量的數(shù)據(jù),然后結(jié)束存儲(chǔ)。這樣不但能存儲(chǔ)檢測(cè)到目標(biāo)后的回波數(shù)據(jù),而且能夠保存一定數(shù)量的檢測(cè)到目標(biāo)前的回波數(shù)據(jù),從而能夠適當(dāng)提高檢測(cè)門限,降低虛警概率,而在事后數(shù)據(jù)處理過程中,利用更復(fù)雜的檢測(cè)算法完整得到目標(biāo)過靶前后的回波數(shù)據(jù),計(jì)算脫靶量測(cè)量結(jié)果。

2.4 FFT處理器設(shè)計(jì)

??? FFT處理器用于將脈沖積累后的雷達(dá)回波數(shù)據(jù)以512點(diǎn)為一幀完成去直流、加窗、FFT、求模平方以及累加運(yùn)算。信號(hào)處理器的存儲(chǔ)單元保證了整個(gè)信號(hào)處理器的流水工作方式,提高了整體處理速度。其功能框圖如圖5所示。

??? 去直流運(yùn)算用于去除回波信號(hào)的直流成分,以便充分利用FFT處理器的動(dòng)態(tài)范圍,減少固定雜波的影響。加窗運(yùn)算則用于以降低頻譜泄漏。加窗運(yùn)算器由窗函數(shù)存儲(chǔ)器和乘法器組成,窗函數(shù)存儲(chǔ)器存儲(chǔ)窗函數(shù)的量化值。將數(shù)據(jù)和窗函數(shù)值讀出送至乘法器的輸入端,完成乘法運(yùn)算后,將結(jié)果截?cái)嗨椭罠FT運(yùn)算器,完成加窗運(yùn)算。兩個(gè)乘法器并行處理,以便同時(shí)對(duì)I、Q數(shù)據(jù)進(jìn)行加窗運(yùn)算。

??? FFT運(yùn)算用于將數(shù)據(jù)轉(zhuǎn)換到頻域以實(shí)現(xiàn)多普勒濾波器組。折中運(yùn)算精度和速度,本設(shè)計(jì)FFT運(yùn)算器采用逐級(jí)流水結(jié)構(gòu)的16位塊浮點(diǎn)結(jié)構(gòu)實(shí)現(xiàn)按時(shí)間抽取基2(DIT-2)FFT運(yùn)算。塊浮點(diǎn)算法相對(duì)定點(diǎn)運(yùn)算有較高的精度,相對(duì)浮點(diǎn)運(yùn)算硬件結(jié)構(gòu)簡單,是定點(diǎn)和浮點(diǎn)運(yùn)算的折衷,從而保證了信號(hào)處理機(jī)的高速和高精度要求[3]。

??? 模平方運(yùn)算用于將FFT運(yùn)算結(jié)果就模平方獲得雷達(dá)回波信號(hào)的功率譜以便進(jìn)行目標(biāo)檢測(cè)。模平方運(yùn)算由乘法器和加法器組成,其工作過程為首先將FFT結(jié)果的實(shí)部和虛部分別讀入兩個(gè)乘法器的輸入端與自己相乘,然后將兩個(gè)乘法器的輸入相加即得模平方結(jié)果。

??? 累加運(yùn)算用于將多路接收機(jī)的回波共功率譜按距離波門進(jìn)行累加,從而減小功率譜的方差,降低恒虛警檢測(cè)的虛警概率。

??? FFT處理器在每幀時(shí)間段內(nèi)要對(duì)所有4路接收機(jī)12個(gè)距離波門的雷達(dá)回波數(shù)據(jù)進(jìn)行處理,處理完畢后,F(xiàn)FT處理器自動(dòng)通知DSP將結(jié)果讀出進(jìn)行恒虛警檢測(cè)。

2.5 恒虛警檢測(cè)器設(shè)計(jì)

??? 恒虛警檢測(cè)器用于在回波中檢測(cè)目標(biāo),采用單元平均恒虛警檢測(cè)方案,由DSP處理器實(shí)現(xiàn)。

??? FFT處理器完成一幀處理結(jié)果后,發(fā)送中斷給DSP處理器,DSP處理器按距離波門讀取FFT處理結(jié)果,在目標(biāo)可能出現(xiàn)的頻率范圍內(nèi)進(jìn)行選大處理,獲得目標(biāo)功率的估計(jì)值,計(jì)算功率譜的均值作為噪聲功率估計(jì)值(計(jì)算平均時(shí)剔除目標(biāo)所在頻點(diǎn)附近幾點(diǎn)以及存在雜波的低頻分量),再計(jì)算兩者的比值并與給定門限進(jìn)行比較。如果超過門限則認(rèn)為存在目標(biāo),否則認(rèn)為沒有目標(biāo)。

??? 為進(jìn)一步降低虛警概率,在進(jìn)行恒虛警檢測(cè)時(shí)采用二元檢測(cè)方案,在連續(xù)4幀中如果有3幀檢測(cè)到目標(biāo)才給出目標(biāo)出現(xiàn)信號(hào)。

2.6 信號(hào)處理機(jī)的實(shí)現(xiàn)

??? 本文設(shè)計(jì)的雷達(dá)數(shù)字信號(hào)處理機(jī)為基于DSP和FPGA的單板機(jī),根據(jù)以上設(shè)計(jì),該信號(hào)處理機(jī)有8路ADC轉(zhuǎn)換電路、2片F(xiàn)PGA、數(shù)據(jù)存儲(chǔ)器、DSP處理和外圍電路以及對(duì)外接口電路組成。

??? ADC轉(zhuǎn)換器件選用TI公司的ADS2806,它為雙路ADC轉(zhuǎn)換器件,可以保證I、Q兩路信號(hào)的一致性,采樣率為36MS/s,轉(zhuǎn)換位寬為12位,滿足系統(tǒng)要求。

??? 脈沖積累和存儲(chǔ)控制采用一片F(xiàn)PGA實(shí)現(xiàn),F(xiàn)FT處理器采用一片F(xiàn)PGA實(shí)現(xiàn)。FPGA選用了Xilinx公司的Virtex II系列FPGA實(shí)現(xiàn)。脈沖積累和存儲(chǔ)控制FPGA選用XC2V250-6FG456,F(xiàn)FT處理FPGA選用XC2V1000-6FG456。兩片F(xiàn)PGA均采用VHDL語言按自頂向下的方法進(jìn)行設(shè)計(jì)。設(shè)計(jì)文件經(jīng)過仿真、綜合、映射、布局、布線及仿真,達(dá)到設(shè)計(jì)要求。

??? 數(shù)據(jù)存儲(chǔ)器采用有掉電保護(hù)功能的NOVSRAM。NOVSRAM的讀寫控制時(shí)序與普通SRAM一樣,其內(nèi)部含有鋰電池和保護(hù)電路,可以在斷電情況下保存數(shù)據(jù)。

??? DSP處理器選用ADI公司32位浮點(diǎn)處理器ADSP21060(SHARC)。其外圍電路有FLASH存儲(chǔ)器,用于存儲(chǔ)固化程序;上電復(fù)位和看門狗電路,用于監(jiān)測(cè)程序的運(yùn)行等。

??? 信號(hào)處理機(jī)對(duì)外接口有數(shù)據(jù)傳輸接口和遙控接口。數(shù)據(jù)傳輸接口用于輸出存儲(chǔ)器存儲(chǔ)的目標(biāo)回波數(shù)據(jù),采用USB2.0接口,其傳輸速度可達(dá)480Mb/s,可以滿足數(shù)據(jù)高速傳輸?shù)囊蟆SB2.0接口芯片采用Philips生產(chǎn)的ISP1581實(shí)現(xiàn)。遙控接口用于接收遙控指令并返回處理機(jī)工作狀態(tài)信息,采用并行接口實(shí)現(xiàn),由中斷信號(hào)實(shí)現(xiàn)握手。

3 恒虛警檢測(cè)算法分析

??? 恒虛警檢測(cè)算法為整個(gè)雷達(dá)信號(hào)處理機(jī)的核心算法,算法采用單元平均恒虛警及二元檢測(cè)方案,在FFT處理結(jié)果上以頻率分辨單元為基礎(chǔ)進(jìn)行檢測(cè)[4]。

??? 由于雜波多普勒頻率比目標(biāo)多普勒頻率低,F(xiàn)FT處理結(jié)果中雜波數(shù)據(jù)主要集中在低頻部分,需檢測(cè)的運(yùn)動(dòng)目標(biāo)多普勒頻率范圍位于頻域無雜波區(qū),因此在FFT處理結(jié)果中剔除存在雜波分量的低頻部分即可降低雜波對(duì)目標(biāo)檢測(cè)的影響。

??? 接收機(jī)噪聲可以看作高斯白噪聲,無目標(biāo)回波數(shù)據(jù)則為高斯白噪聲的采樣,假設(shè)其方差為σ2。如果數(shù)據(jù)中存在目標(biāo)回波信號(hào),回波信號(hào)幅度為A,則其信噪比為:

???

??? 經(jīng)N點(diǎn)FFT運(yùn)算后,信號(hào)分量幅度為NA,噪聲方差為Nσ2,信噪比為:

???

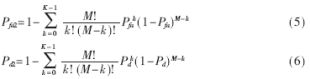

??? 這樣利用R個(gè)頻率分辨單元以閾值T進(jìn)行目標(biāo)檢測(cè)的虛警概率和檢測(cè)概率分別為[4]:

???

??? 本文測(cè)量雷達(dá)目標(biāo)為過靶段的反艦導(dǎo)彈,其回波在連續(xù)數(shù)幀內(nèi)都應(yīng)該存在,為了進(jìn)一步降低虛警概率,提高檢測(cè)概率,可以采用二元檢測(cè)方案,即在連續(xù)M幀內(nèi)如果有多于K幀檢測(cè)到目標(biāo),則判斷為目標(biāo)存在。采用二元檢測(cè)方案的檢測(cè)概率和虛警概率如下[5]:

???

??? 實(shí)際設(shè)計(jì)中,設(shè)定單次檢測(cè)虛警概率小于10-5,二元檢測(cè)策略為在連續(xù)4幀內(nèi)有3幀檢測(cè)到目標(biāo),F(xiàn)FT點(diǎn)數(shù)N為512,頻率分辨單元個(gè)數(shù)R為100。由(3)式可得檢測(cè)閾值T為0.194,由(5)式可得二元檢測(cè)的虛警概率為4×10-15,由(4)式可得目標(biāo)信噪比為0dB時(shí)單次檢測(cè)的檢測(cè)概率0.96,由(6)式可得相應(yīng)的二元檢測(cè),檢測(cè)概率為0.99。

??? 本文討論了一種脈沖多普勒雷達(dá)信號(hào)處理機(jī)的設(shè)計(jì)與實(shí)現(xiàn),用于在雷達(dá)回波中自動(dòng)檢測(cè)運(yùn)動(dòng)目標(biāo)并錄取目標(biāo)回波數(shù)據(jù)。該處理機(jī)采用“ADC+FPGA+DSP+存儲(chǔ)器”結(jié)構(gòu)實(shí)現(xiàn),降低了電路設(shè)計(jì)的復(fù)雜度以及信號(hào)處理機(jī)的體積、重量、功耗等,有效提高了系統(tǒng)可靠性,且具有一定的靈活性和可擴(kuò)展性。該信號(hào)處理機(jī)已經(jīng)在某型對(duì)海矢量脫靶量測(cè)量雷達(dá)上得到應(yīng)用,取得了很好的效果。

參考文獻(xiàn)

[1] MERRILL I S.Introduction to Radar System(Third Edition)[M].Boston,McGraw-Hill,2001.

[2] 趙保軍.可適用于多種模式的雷達(dá)視頻信號(hào)處理研究[R].北京:北京理工大學(xué)博士后研究工作報(bào)告,1998.

[3] 韓穎.高速專用FFT處理器的設(shè)計(jì)與實(shí)現(xiàn)[R].北京:北京理工大學(xué)碩士學(xué)位論文,2003.

[4] DILLARD G M,SUMMERS B F.Mean-level detection in? frequency domain[J].IEE Proc-Radar Sonar Navigation,

1996,143(5):307-312.

[5] 何友.雷達(dá)自動(dòng)檢測(cè)與恒虛警處理[M].北京:清華大學(xué)出版社,1999.