摘 要: 分析了等精度測頻" title="測頻">測頻在實(shí)現(xiàn)時存在的問題,介紹了一種基于自適應(yīng)分頻" title="分頻">分頻法的頻率測量技術(shù),可達(dá)到簡化測量電路、提高系統(tǒng)可靠性、實(shí)現(xiàn)高精度和寬范圍測量的目的。由于PC104總線、FPGA等嵌入式技術(shù)的使用,使得整個測量系統(tǒng)具有體積小、功耗低、便于攜帶等特點(diǎn)。

關(guān)鍵詞: 等精度 自適應(yīng) 分頻 FPGA

在電子測量中,頻率是最基本的測量量之一。目前采用比較廣泛的是等精度測頻" title="等精度測頻">等精度測頻法(多周期同步測量法),這種方法具有測量精度" title="測量精度">測量精度高、測量精度不隨被測信號的變化而變化的特點(diǎn)[1]。但這種方法需要的硬件開銷大,且同步電路結(jié)構(gòu)復(fù)雜,易造成誤觸發(fā),可靠性不高。本文針對等精度測頻法的不足,采用自適應(yīng)的分頻方法對被測信號進(jìn)行連續(xù)分頻,從而產(chǎn)生可靠的閘門控制信號" title="控制信號">控制信號,簡化了電路結(jié)構(gòu);同時根據(jù)實(shí)際需要,在設(shè)計(jì)中加入了頻率信號的預(yù)處理電路,并結(jié)合PC104總線以及FPGA等技術(shù),實(shí)現(xiàn)了對頻率信號寬范圍、高速度、高精度的測量。該系統(tǒng)作為某型號計(jì)量校準(zhǔn)裝置的一部分,已很好地應(yīng)用于實(shí)際使用中。

1 等精度測頻原理及其改進(jìn)

等精度測頻是在直接測頻的基礎(chǔ)上發(fā)展而來的。等精度測頻的最大特點(diǎn)就是在整個頻率范圍內(nèi)都能達(dá)到同樣的測量精度,且與被測信號頻率大小無關(guān)。其基本原理如圖1所示[1~2]。

在測量過程中,預(yù)置閘門信號的上升沿啟動測量過程,但此時對被測信號計(jì)數(shù)的計(jì)數(shù)器1和對基準(zhǔn)時鐘計(jì)數(shù)的計(jì)數(shù)器2并沒有開始計(jì)數(shù)。預(yù)置閘門信號變?yōu)楦唠娖胶螅粶y信號的第一個上升沿使得實(shí)際閘門信號變?yōu)楦唠娖接行盘枺?jì)數(shù)器1和2開始計(jì)數(shù)。當(dāng)預(yù)置閘門信號變?yōu)榈碗娖叫盘枙r,計(jì)數(shù)器1和2并沒有立即停止計(jì)數(shù),而是要等到緊接在其后的被測信號的上升沿到來時,實(shí)際閘門信號變?yōu)榈碗娖綗o效信號時才停止計(jì)數(shù)。若記計(jì)數(shù)器1的計(jì)數(shù)值為N1,計(jì)數(shù)器2的計(jì)數(shù)值為N2,基準(zhǔn)頻率為f0,被測頻率為fx,則有fx=f0·N2/N1。

等精度測頻方法除了需要兩個計(jì)數(shù)器分別對被測信號和基準(zhǔn)時鐘進(jìn)行計(jì)數(shù)外,還需要附加一個額外的計(jì)數(shù)器來產(chǎn)生預(yù)置閘門控制信號,而且由于預(yù)置閘門控制信號的引入,增加了同步電路的復(fù)雜度。當(dāng)被測信號頻率較高時,被測信號的上升沿和預(yù)置閘門信號的下降沿可能會出現(xiàn)競爭冒險(xiǎn)的問題,從而造成誤觸發(fā),影響了測量精度,降低了系統(tǒng)的可靠性。

針對這一問題,改進(jìn)以后的等精度測頻原理如圖2所示。

其工作過程分為粗測和精測兩步。粗測時,將被測信號的預(yù)分頻數(shù)設(shè)置為2,對其進(jìn)行分頻,分頻后信號的上升沿啟動計(jì)數(shù)器1對基準(zhǔn)頻率進(jìn)行計(jì)數(shù),其后緊接著的下降沿使計(jì)數(shù)停止,根據(jù)計(jì)數(shù)值的大小估算出被測信號的頻率。精測時,根據(jù)此前估算的頻率和預(yù)先設(shè)定的測量時間,調(diào)整被測信號的預(yù)分頻數(shù)(譬如預(yù)先設(shè)定的測量時間為1s,估算的被測信號頻率為6000Hz,那么調(diào)整后預(yù)分頻數(shù)為1/(1/6000)=6000),再重復(fù)對基準(zhǔn)頻率的計(jì)數(shù)過程,完成頻率測量。

這種改進(jìn)既實(shí)現(xiàn)了等精度測量的基本思想——被測信號的測量時間為整數(shù)個周期,又可根據(jù)被測信號頻率的不同,自動調(diào)整被測信號的預(yù)分頻數(shù),直接利用分頻后的信號作為閘門控制信號。這樣就將對被測信號的計(jì)數(shù)和分頻合二為一,從而簡化了電路結(jié)構(gòu),減少了硬件開銷,避免了誤觸發(fā),提高了測量系統(tǒng)的可靠性,達(dá)到了寬范圍、等精度測量的要求。

2 誤差分析

設(shè)被測信號頻率為fx,基準(zhǔn)信號頻率為f0,對基準(zhǔn)信號頻率的計(jì)數(shù)值為N0,精測時被測信號的分頻數(shù)為Nx,則依據(jù)改進(jìn)后的等精度測頻原理,被測信號頻率fx=2·f0·Nx/N0。

測量結(jié)果的相對不確定度為:

預(yù)分頻數(shù)Nx不存在±1誤差,所以根號中的第二項(xiàng)為0;在實(shí)際中,采用高穩(wěn)晶振,其相對不確定度可達(dá)1×10-7;而由于采用對被測頻率連續(xù)進(jìn)行分頻,使閘門時間足夠長(如1s),這樣填充的基準(zhǔn)脈沖數(shù)可達(dá)107,N0的最大誤差就是±1,所以N0的相對不確定度也可達(dá)到1×10-7。綜合起來,頻率測量結(jié)果的相對不確定度可達(dá)10-7數(shù)量級,實(shí)現(xiàn)了高精度測量。同時,對于頻率越低的信號,N0會越大,其相對不確定度會更小,但由于晶振的相對不確定性的影響,它仍然只能達(dá)到10-7數(shù)量級,要想進(jìn)一步提高測量精度,就必須使用更高精度的晶振。

3 硬件設(shè)計(jì)

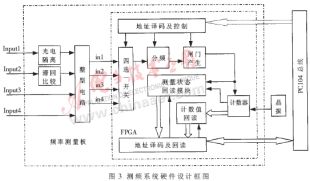

測頻系統(tǒng)的硬件設(shè)計(jì)如圖3所示。

作為一個實(shí)際的頻率校準(zhǔn)系統(tǒng),測量的頻率信號不僅有標(biāo)準(zhǔn)的TTL電平信號,也有正弦信號以及需要隔離的頻率信號,所以在測頻系統(tǒng)中,對不同類型的頻率信號進(jìn)行預(yù)處理(光電隔離、滯回比較、信號整型等),這樣便使整個測頻系統(tǒng)能夠得到更廣泛的應(yīng)用。

PC104嵌入式處理器具有體積小、集成度高、可靠性高、功耗低、便于攜帶等特點(diǎn),可作為測頻系統(tǒng)的控制器,完成頻率測量的控制和運(yùn)算任務(wù)。

現(xiàn)場可編程門陣列FPGA由于具有集成度高、高速度和高穩(wěn)定性的特點(diǎn),而被廣泛應(yīng)用到數(shù)字邏輯電路的設(shè)計(jì)中。本測頻系統(tǒng)的核心就是一塊FPGA芯片——Altera公司的EPF10K10,所有的邏輯模塊均在FPGA中實(shí)現(xiàn)。

測頻工作原理如下:由四選一選擇開關(guān)選擇一路信號作為當(dāng)前的測量通道;被測信號進(jìn)入分頻模塊,按預(yù)置分頻數(shù)進(jìn)行分頻;分頻后的信號通過閘門信號產(chǎn)生模塊產(chǎn)生閘門控制信號,當(dāng)閘門控制信號為高電平有效信號時,基準(zhǔn)時鐘被測量計(jì)數(shù)器模塊計(jì)數(shù);測量停止后,產(chǎn)生相應(yīng)的停止標(biāo)志位和溢出標(biāo)志位,以供軟件進(jìn)行查詢;當(dāng)軟件查詢到測量停止時,讀取計(jì)數(shù)器數(shù)值,計(jì)算后得到頻率值。

4 軟件設(shè)計(jì)

根據(jù)測頻過程的思路,可編寫相應(yīng)的軟件。測頻程序流程圖如圖4所示。

本文設(shè)計(jì)的等精度測頻系統(tǒng),從原理上對傳統(tǒng)的等精度測頻方法進(jìn)行了一些改進(jìn),采用自適應(yīng)分頻方法,簡化了電路結(jié)構(gòu),提高了系統(tǒng)可靠性;測量精度可達(dá)10-7數(shù)量級,測量范圍從0.1Hz到50MHz,實(shí)現(xiàn)了高精度、寬范圍的測量。而在實(shí)際設(shè)計(jì)中,通過使用PC104總線和FPGA芯片等技術(shù),使整個系統(tǒng)具有體積小、功耗低、便于攜帶等特點(diǎn),可以方便地應(yīng)用到野外條件下的頻率測量和校準(zhǔn)中。

參考文獻(xiàn)

1 喬長安,陳運(yùn)濤,張富平等.等精度頻率測量方法.火力與指揮控制, 2003(28)

2 張志明,李蓉艷.基于PC總線的高精度頻率測量卡設(shè)計(jì). 微型機(jī)與應(yīng)用,1999(2)

3 宋萬杰,羅 豐,吳順君. CPLD技術(shù)及其應(yīng)用. 西安:西安電子科技大學(xué)出版社, 2001

4 夏宇聞. 復(fù)雜數(shù)字電路與系統(tǒng)的Verilog HDL設(shè)計(jì)技術(shù). 北京:北京航空航天大學(xué)出版社, 1998