1 引言

數(shù)據(jù)采集處理技術(shù)是現(xiàn)代信號處理的基礎(chǔ),廣泛應(yīng)用于雷達、通信、遙測遙感等領(lǐng)域。隨著信息科學(xué)的飛速發(fā)展,人們面臨的信號處理任務(wù)愈來愈繁重,對數(shù)據(jù)采集處理系統(tǒng)的要求也愈來愈高。特別是在圖像處理、瞬態(tài)信號檢測、軟件無線電等領(lǐng)域,更是要求高速度、高精度、高實時性的數(shù)據(jù)采集與處理技術(shù)。

在傳統(tǒng)高速信號處理中,數(shù)字信號處理算法一般是通過專門優(yōu)化的數(shù)字信號處理器實現(xiàn)的,目前主要有TI公司的DSP和AD公司的ADSP用于高端信號處理器應(yīng)用。當這些處理器仍無法滿足高速信號處理要求時,可以使用專用的信號處理ASIC芯片,然而使用ASIC在設(shè)計上受ASIC廠商設(shè)計思路限制,使電路設(shè)計變得困難和缺乏靈活性。而最近幾年具有乘法器及內(nèi)存塊資源的大容量FPGA以及基于IP核嵌入的FPGA開發(fā)技術(shù)的出現(xiàn),可以將嵌入式微處理器、專用數(shù)字器件和高速DSP算法以IP核的形式方便的嵌入FPGA,以硬件編程的方法實現(xiàn)高速信號處理算法,這種形式的嵌入為高端應(yīng)用領(lǐng)域提供了超高性價比的解決方案。

2 高速數(shù)據(jù)采集處理卡工作原理及主要器件選用

該高速數(shù)據(jù)采集處理卡是基于DSP+FPGA架構(gòu)來設(shè)計的。FPGA是整個系統(tǒng)的時序控制中心和數(shù)據(jù)交換橋梁,而且能夠?qū)崿F(xiàn)對底層的信號快速預(yù)處理,在很多信號處理系統(tǒng)中,底層的信號預(yù)處理算法要處理的數(shù)據(jù)量很大,對處理速度要求很高,但算法結(jié)構(gòu)相對比較簡單,適于用FPGA進行硬件編程實現(xiàn)。而高層處理算法的特點是速據(jù)量較低,但算法控制結(jié)構(gòu)復(fù)雜,適于用運算速度快、尋址靈活、通信機制強大的DSP芯片來實現(xiàn)。

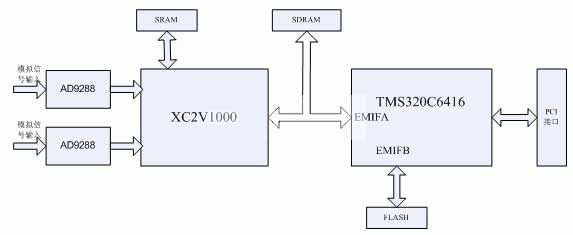

整個高速數(shù)據(jù)采集處理系統(tǒng)的主要硬件構(gòu)成為:高速ADC、RAM、高性能DSP和PCI接口、大容量FPGA。模擬輸入經(jīng)AD采樣進入FPGA,經(jīng)過FPGA里的信號預(yù)處理模塊處理后進入DSP,由DSP軟件進行后續(xù)高級算法處理,DSP通過PCI接口與主機交換數(shù)據(jù)。系統(tǒng)的原理框圖如圖1所示。

圖1:數(shù)據(jù)采集處理卡總體結(jié)構(gòu)框圖

DSP采用TI公司的TMS320C6000系列定點DSP中的TMS320C6416;ADC采用2片AD公司的AD9288,從而實現(xiàn)4路8位采樣,最高采樣頻率為100 MSPS;PCI接口采用TMS320C6416 芯片內(nèi)集成的PCI2.2控制器,理論最大數(shù)據(jù)傳輸速率為132MBps; DSP程序存儲在Flash存儲器中,器件選用AM29LV160。下面逐一介紹各個主要器件的特性:

2.1 AD9288

AD9288是一款雙8bit 高速模數(shù)轉(zhuǎn)換器,兩個ADC可以獨立工作,最高采樣率100MSPS,內(nèi)部集成了跟蹤保持電路和基準電路,單電源工作。平行輸出接口,兼容TTL/CMOS格式,工業(yè)標準溫度工作范圍, 48PIN LQFP封裝。適合應(yīng)用與高速信號測量儀器,無線通訊設(shè)備。

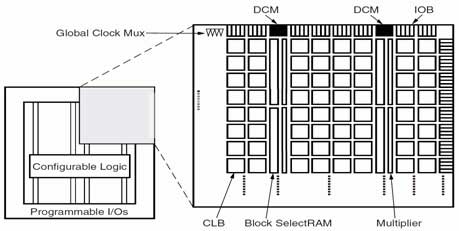

2.2 XC2V1000

單片XILINX公司的XC2V1000芯片,芯片集成度達100萬門,具有40個18×18乘法器及40個18Kbit塊內(nèi)存等資源,并有豐富的內(nèi)部邏輯及路由資源,非常適合實現(xiàn)高速DSP算法,并具有8個DCM可實現(xiàn)復(fù)雜的時鐘管理,支持不同形式的I/O接口。

圖2:Virtex2 結(jié)構(gòu)圖

2.3 TMS320C6416

本設(shè)計選用的TMS320C6416是TI公司近年推出的高性能定點DSP,其時鐘頻率達600MHz,最高處理能力4800MIPS,采用先進的甚長指令結(jié)構(gòu)(VLIW)的DSP內(nèi)核有8個運算功能單元,每個時鐘周期可以執(zhí)行8條指令,所有指令可以條件執(zhí)行。該DSP具有VITERBI譯碼協(xié)處理器(VCP)和turbo譯碼協(xié)處理器(TCP);采用二級緩存結(jié)構(gòu),一級緩存(L1)由128Kbit的程序緩存和128Kbit的數(shù)據(jù)緩存組成,二級緩存(L2)為8Mbit;有2個擴展存儲器接口EMIF,一個為64bit(EMIFA),一個為16bit(EMIFB),可以與異步(SRAM、EPROM)/同步存儲器的DMA通道;主機接口(HPI)總線寬度可由用戶配置(32/16bit),具有32bit/33MHz,3.3V的PCI主從接口,該接口符合PCI標準2.2版,有3個多通道串口(McBSPs),片內(nèi)還有一個16針的通用輸入輸出接口(GPIO)。

3 高速數(shù)據(jù)采集處理系統(tǒng)的硬件連接

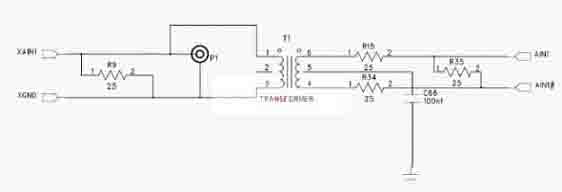

3.1 模擬信號輸入接口設(shè)計

AD9288的模擬信號輸入采用差分輸入方式。單端輸入方式連接比較簡單,但抗噪性能差,采取差分輸入方式可以盡量減少信號噪聲以及電磁的干擾。其AD芯片的單路AD輸入電路如圖2所示:

圖3:模擬信號輸入電路

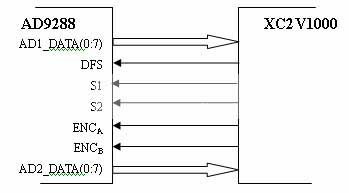

3.2 AD9288與FPGA芯片的連接

AD采樣時鐘ENC、采樣輸出數(shù)據(jù)AD_DATA及輸出數(shù)據(jù)格式選擇DFS等控制信號均接入FPGA,由FPGA靈活編程控制AD采樣。

圖4:AD與FPGA連接結(jié)構(gòu)圖

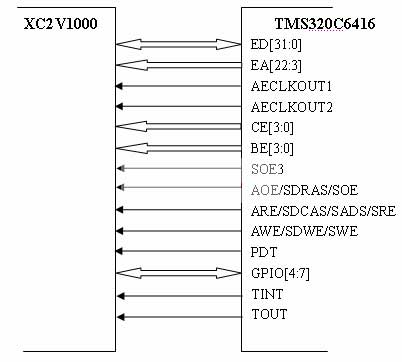

3.3 FPGA 與DSP芯片的連接

DSP 通過EMIFA口數(shù)據(jù)線、地址線、片選信號及其它接口控制信號與FPGA的IO連接,實現(xiàn)FPGA內(nèi)部生成FIFO或RAM等緩存組件與DSP連接,該部分電路主要功能是可以將FPGA內(nèi)存儲器映射到DSP地址空間,從而實現(xiàn)DSP對FPGA的直接高速數(shù)據(jù)交換。另將DSP 外部中斷IO信號、及定時器信號接入FPGA,以靈活的實現(xiàn)FPGA與DSP的控制通信。

圖5: FPGA與DSP連接結(jié)構(gòu)圖

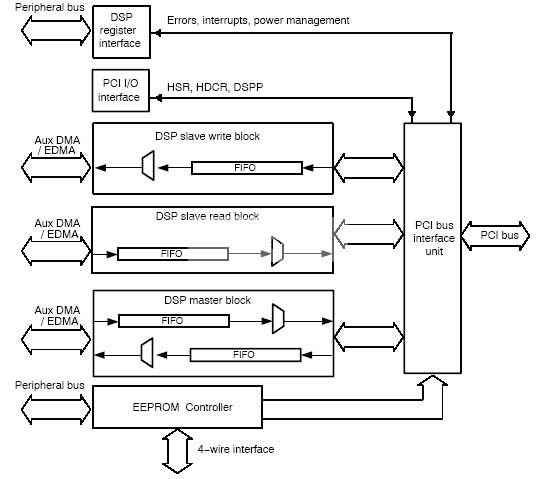

3.4 PCI硬件接口

TMS320C6416內(nèi)部集成33MHz/32位支持PCI主/從接口的PCI2.2接口控制器,無需額外的PCI控制芯片即可方便的與具有PCI接口的主機直接互連。DSP通過內(nèi)部的EDMA控制器實現(xiàn)集成的PCI接口控制器與DSP的接口。

圖6:PCI接口功能模塊圖

4 PCI接口軟件設(shè)計

PCI接口開發(fā)中有相當大的工作量是關(guān)于PCI軟件的開發(fā),PCI軟件主要包括兩方面的工作:驅(qū)動程序設(shè)計和主機端應(yīng)用程序的設(shè)計。本系統(tǒng)軟件的設(shè)計目標是實現(xiàn)數(shù)據(jù)采集卡與主機高速的DMA傳輸及對主機對DSP內(nèi)存空間的讀寫。

4.1 驅(qū)動程序設(shè)計

驅(qū)動程序根據(jù)Windows 驅(qū)動程序模型(WDM)設(shè)計,運行在Win2000 平臺上。支持即插即用,采用基于數(shù)據(jù)包的DMA 傳輸方式,采用Numega公司的開發(fā)包Driver Works和Microsoft公司的2000DDK,并以VC++6.0作為輔助開發(fā)環(huán)境。

當應(yīng)用程序請求從采集卡讀數(shù)據(jù)時,內(nèi)核I/O 管理器將此請求打包成一個IRP(I/O 請求包),驅(qū)動程序調(diào)用相關(guān)例程把應(yīng)用程序發(fā)來控制信息寫入DSP設(shè)置的控制寄存器,并調(diào)用驅(qū)動程序的讀例程。如果數(shù)據(jù)處理卡不忙,數(shù)據(jù)處理卡作為PCI主設(shè)備就啟動DMA傳輸;當本次DMA 傳輸完成時,處理卡產(chǎn)生中斷,I/O 管理器調(diào)用驅(qū)動程序的中斷服務(wù)例程和DpcForIsr完成此IRP,并從IRP 隊列中取出下一個IRP,啟動下一次DMA。下一次中斷發(fā)生時同樣處理。這樣不斷地進行DMA 傳輸,直到IRP 隊列空為止。

4.2 應(yīng)用程序設(shè)計

主機應(yīng)用程序是主要實現(xiàn)從高速數(shù)據(jù)采集處理板該取處理后的數(shù)據(jù)、存儲、顯示處理及結(jié)果以及向數(shù)據(jù)采集處理板發(fā)送控制命令。在Windows 2000下,我們使用的應(yīng)用程序開發(fā)工具是VC++6.0。通過CreatFile()函數(shù)得到PCI句柄,用DeviceIoControl()函數(shù)來向設(shè)備驅(qū)動程序發(fā)送請求及命令,完成數(shù)據(jù)的讀取與寫入。用ReadFile()函數(shù)調(diào)用驅(qū)動啟動DMA傳輸實現(xiàn)高速數(shù)據(jù)傳輸。

5 結(jié)束語

本高速采集數(shù)據(jù)處理卡應(yīng)用了大容量FPGA及高性能數(shù)字信號處理器DSP技術(shù)和PCI總線技術(shù)。DSP是為數(shù)字信號處理專門開發(fā)的芯片,其內(nèi)部的總線結(jié)構(gòu)和指令非常適合于數(shù)字信號處理,而FPGA高速硬件實現(xiàn)算法的特點使得大容量高速FPGA成為數(shù)據(jù)處理板級設(shè)計重要的選擇,PCI接口的高速可靠的傳輸速率滿足了與主機應(yīng)用軟件數(shù)據(jù)傳輸?shù)男枨蟆1驹O(shè)計主要是為了軟件無線電接收機預(yù)研所設(shè)計的實驗平臺,經(jīng)實際驗證,系統(tǒng)運行可靠,是一種比較好的高速數(shù)據(jù)采集與處理的解決方案,有著廣泛的應(yīng)用前景,也可以用于圖像處理、雷達信號處理等數(shù)據(jù)采集處理領(lǐng)域。