摘 要: 將Petri網(wǎng)" title="Petri網(wǎng)">Petri網(wǎng)與VHDL" title="VHDL">VHDL結(jié)合,運用Petri網(wǎng)建立硬件系統(tǒng)模型,然后采用VHDL語言進行設(shè)計,最終下載到CPLD" title="CPLD">CPLD,成功地實現(xiàn)了整個硬件系統(tǒng)的邏輯控制器設(shè)計。

關(guān)鍵詞: Petri網(wǎng) C/E模型" title="C/E模型">C/E模型 VHDL CPLD

Petri網(wǎng)是異步并發(fā)系統(tǒng)[1],沒有人為的控制流,直觀地表示了非確定性;且可以圖形化的方式描述復雜的系統(tǒng),并可運用數(shù)學工具進行分析。因此,其在軟件系統(tǒng)的建模與仿真中得到廣泛應用。Petri網(wǎng)自身具備的可運行性方便了系統(tǒng)形式化描述級的模擬,可以用于表達不同抽象級上的系統(tǒng)概念并清楚地描述整個系統(tǒng)的運作過程。筆者發(fā)現(xiàn)Petri網(wǎng)的應用目前僅局限于軟件系統(tǒng)的設(shè)計,例如網(wǎng)絡協(xié)議、物流管理等,而在硬件系統(tǒng)中卻很少涉足。硬件系統(tǒng)隨著功能的日益增強,其功能描述也越來越復雜。基于硬件系統(tǒng)描述的VHDL語言以其強大的硬件描述能力,已被廣大科研工作者所采用。VHDL語言也適用于描述異步并發(fā)系統(tǒng),因此可與Petri網(wǎng)建立的模型聯(lián)系起來。

本文采用自頂向下與層次分析相結(jié)合的設(shè)計方法,用Petri網(wǎng)的一個子類C/E系統(tǒng)(條件/事件系統(tǒng))對視頻輸入卡的邏輯控制器建立模型。針對控制器C/E模型中關(guān)心和需要觀察的變量,確定VHDL描述的實體和端口,由C/E系統(tǒng)網(wǎng)的拓撲結(jié)構(gòu)確定條件和事件間的邏輯關(guān)系,構(gòu)造VHDL語言中的結(jié)構(gòu)體。采用EDA開發(fā)工具MAX+PLUS II進行代碼設(shè)計,邏輯綜合,并對設(shè)計進行仿真,最后下載到CPLD,驗證了邏輯控制器設(shè)計的正確性。

1 應用背景及控制器功能要求

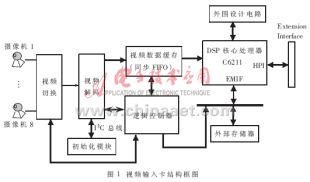

圖1為某一視頻輸入卡結(jié)構(gòu)框圖。前端視頻信號經(jīng)過解碼、緩沖后,將數(shù)據(jù)送入DSP處理。其中由邏輯控制器協(xié)調(diào)各部分之間的運作。從圖1中可以看出,邏輯控制器與視頻切換、視頻解碼、視頻數(shù)據(jù)緩存以及DSP等部分存在聯(lián)系,歸納起來需要完成五個基本功能:視頻通道切換控制;插入行標志信息;FIFO的初始化操作;寫FIFO;讀FIFO。

要完成上述五個基本功能,必須保證每個功能與另一功能之間不存在沖突,但允許存在并發(fā)行為,同時它們之間的邏輯順序應保持一致。因此需要一個主控模塊協(xié)調(diào)各部分的操作。各功能部分之間的邏輯關(guān)系比較復雜,涉及到圖像數(shù)據(jù)的行同步以及場同步等問題,一旦出錯,則接收的就不是有效的圖像數(shù)據(jù),后續(xù)工作也不能正常進行。為此,首先建立Petri網(wǎng)模型,并運用數(shù)學工具進行分析,最后采用VHDL語言實現(xiàn)。

2 控制器Petri網(wǎng)模型

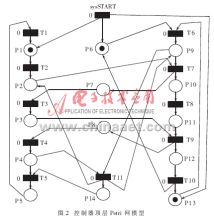

應用Petri網(wǎng)的一個子類C/E建立視頻輸入卡的邏輯控制器模型。控制器實現(xiàn)的五大功能,在滿足各自條件的情況下,能夠正確地完成相關(guān)操作。如果將每個功能展開進行Petri網(wǎng)模型設(shè)計,將會使整個C/E系統(tǒng)的節(jié)點過多。節(jié)點一多,則不易分析其性質(zhì)和計算它的可達樹、不變量等參數(shù)。Petri網(wǎng)特有的直觀易懂、適于交流的圖形表示也就失去了意義。采用層次分析的方法,首先在頂層根據(jù)各功能要求建立一個Petri網(wǎng)模型,然后在各個模塊內(nèi)部建立更詳細的子模型。鑒于頂層和底層的分析方法類似,只將頂層模型展開討論。網(wǎng)絡的一些動態(tài)特性,如庫所與變遷的含義如表1所示。

邏輯控制器頂層Petri網(wǎng)模型如圖2所示。該模型是一個基本網(wǎng)系統(tǒng),其狀態(tài)元素稱為條件,變遷元素稱為事件。事件的發(fā)生改變條件的狀態(tài)(成真與否),引起信息在網(wǎng)上的流動[1]。由條件和事件組成的有向網(wǎng)通常表現(xiàn)為三元組(B,E;F),其中B為條件集,E為事件集。同時該模型還滿足如下條件:

·(B,E;F)為簡單網(wǎng);

·B中每個條件都有機會成真,也有機會成假;

·E中每個事件都有機會發(fā)生;

·由初始情態(tài)ci導出的可達情態(tài)集是完全可到達關(guān)系R下的等價類。

因此,該模型還是一個C/E系統(tǒng)。在Petri網(wǎng)仿真軟件Visual Object Net++中進行仿真測試,結(jié)果表明該模型能很好地描述控制器各部分之間的邏輯關(guān)系。

3 VHDL程序的基本單元設(shè)計

CPLD(復雜可編程邏輯器件)是處于并行工作方式的基本電路單元構(gòu)成的高速、大規(guī)模集成器件[2],可作為一種并發(fā)系統(tǒng)模型與Petri網(wǎng)建立聯(lián)系。VHDL作為一種硬件描述語言,支持行為描述、數(shù)據(jù)流描述和結(jié)構(gòu)化描述等多種描述方法,可以用并行和順序多種語句方式描述實際的系統(tǒng),并可采用VHDL的并行語句描述C/E系統(tǒng)中條件/事件間的并發(fā)關(guān)系,用VHDL的順序語句描述條件/事件間的順序約束機制,為解決C/E系統(tǒng)中的有效沖突提供了可行的方法。

VHDL語言程序設(shè)計的基本單元稱為一個基本設(shè)計實體,其主要由實體說明(entity declaration)和構(gòu)造體(architecture body)兩部分構(gòu)成。實體說明部分規(guī)定了設(shè)計單元的輸入輸出接口信號或引腳。根據(jù)該控制器的C/E系統(tǒng)中關(guān)心和需觀察的變量選擇系統(tǒng)的輸入和輸出信號,以確定基本設(shè)計單元的實體及其端口。在控制器的C/E系統(tǒng)模型中,因為事件驅(qū)動條件是變化的,所以將發(fā)生的事件作為設(shè)計實體的輸入信號,系統(tǒng)條件作為實體的輸出信號。同時,為實體設(shè)計一個輸入端口sysSTART,使系統(tǒng)上電復位。當sysSTART觸發(fā)時賦予系統(tǒng)初始標識,系統(tǒng)資源(Token)流動使能。下面是具體的VHDL實體描述。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

……(其它庫)

ENTITY MainCtrl IS

PORT(sysSTART: IN 數(shù)據(jù)類型;

事件:IN數(shù)據(jù)類型;

條件:OUT數(shù)據(jù)類型);

END MainCtrl IS;

構(gòu)造體部分定義了設(shè)計單元的具體構(gòu)造和操作(行為)。C/E系統(tǒng)模型的拓撲結(jié)構(gòu)直觀地表達了條件和事件間的約束機制。這種約束機制映射為控制器內(nèi)部各模塊之間的邏輯關(guān)系。根據(jù)控制器C/E系統(tǒng)模型的特點,可采用多進程結(jié)構(gòu)描述C/E系統(tǒng)。進程內(nèi)部順序執(zhí)行,進程之間并發(fā)執(zhí)行。多進程結(jié)構(gòu)是并行執(zhí)行進程的網(wǎng)絡,多個進程并發(fā)執(zhí)行。因此從C/E系統(tǒng)的拓撲結(jié)構(gòu),可將各進程映射為C/E系統(tǒng)的各庫所狀態(tài),從而能夠描述出各條件庫所間的異步并發(fā)關(guān)系。各進程之間通過接口信號進行通信。接口信號是由新變化的參量引導進程產(chǎn)生的輸出結(jié)果。設(shè)計進程的程序,使之產(chǎn)生的輸出結(jié)果成為新的庫所狀態(tài),從而影響變遷觸發(fā)(fire)條件,以各進程的輸出結(jié)果作為進程間的通信接口信號。具體描述如下:

ARCHITECTURE behav OF MainCtrl IS

BEGIN

進程Ri:PROCESS(事件集) i∈[1,14]

BEGIN

Pi<= 進程Ri的輸出;

……

END PROCESS Ri;

......

END behav;

沖突是由系統(tǒng)資源的共享產(chǎn)生的,與并發(fā)是一對對偶的概念[1]。在實際的Petri網(wǎng)模型中可能存在沖突K=

(1)由用戶選擇,有沖突的地方通常是需要作出選擇和決策的地方。

(2)設(shè)置合適的觸發(fā)規(guī)則:確定性產(chǎn)生規(guī)則,如優(yōu)先級;不確定性產(chǎn)生規(guī)則,如發(fā)生概率。

(3)改變系統(tǒng)結(jié)構(gòu),即改寫Petri網(wǎng)的關(guān)聯(lián)矩陣,增加共享資源回收。

VHDL語言中的并行語句同樣不能解決沖突問題。使用VHDL并行語句描述沖突時將導致資源的丟失。而使用VHDL語言中的順序語句,如進程內(nèi)部的語句,采用設(shè)定不同優(yōu)先級的方法,可以解決Petri網(wǎng)中存在的沖突。本控制器C/E系統(tǒng)也存在沖突現(xiàn)象,如圖3所示。

對每個庫所Pi進程的變化(Token的有無),使用電平的高低來表征。事件發(fā)生與否,用脈沖出現(xiàn)與否表征。該C/E系統(tǒng)的結(jié)構(gòu)體共有14個并行處理的進程。根據(jù)對控制器進行形式描述的思想,在進程內(nèi)部采用下列結(jié)構(gòu):

進程Ri:PROCESS(事件參數(shù)表), i∈[1,14]

……

IF(<條件表達式>) THEN

<行為表達式>;

END IF;

END PROCESS 進程Ri;

事件參數(shù)表(也稱敏感量)中事件觸發(fā)進程的執(zhí)行過程是:在判斷事件的<條件表達式>為真后,順序執(zhí)行其后的<行為表達式>,由新變化的參量引導進程產(chǎn)生輸出結(jié)果;執(zhí)行完進程語句后,返回進程的事件參數(shù),等待事件集新的變化,引發(fā)進程的再一次進行,往復循環(huán)。

4 基于VHDL的仿真與CPLD實現(xiàn)

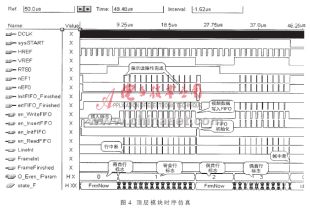

VHDL語言設(shè)計技術(shù)齊全,方法靈活,支持廣泛,對系統(tǒng)硬件描述能力強,具有多層次描述系統(tǒng)硬件的能力,可以從系統(tǒng)的數(shù)學模型直到門級電路[3]。對控制器的Petri網(wǎng)模型進行VHDL程序設(shè)計后,利用綜合器進行邏輯綜合和優(yōu)化,綜合后再經(jīng)仿真器進行時序仿真,得到涉及器件硬件特性的仿真結(jié)果,其結(jié)果正確。最后下載到Altera系列的EPM7128STC-6芯片上,從而實現(xiàn)視頻輸入卡邏輯控制器設(shè)計。行為仿真結(jié)果的仿真波形如圖4所示。

將Petri網(wǎng)與EDA技術(shù)結(jié)合,對視頻輸入卡邏輯控制器用Petri網(wǎng)的C/E系統(tǒng)建模,并使用VHDL對協(xié)議的C/E系統(tǒng)模型進行程序設(shè)計,最后由CPLD器件實現(xiàn)控制器模型,使之成為實際的邏輯控制電路。這為硬件電路的高層綜合設(shè)計提供了一種方法,也為軟件系統(tǒng)和硬件系統(tǒng)開辟了一條溝通的渠道。對于其它具有多因素、動態(tài)和并發(fā)特點的系統(tǒng),同樣可用Petri網(wǎng)建立模型,用CPLD器件對模型進行仿真和實現(xiàn)。

參考文獻

1 袁祟義. Petri網(wǎng)原理[M]. 北京:電子工業(yè)出版社,1998

2 MAX+PLUS II Programable Logic development System Altera Corporation[J]. 1997

3 林 敏,方穎立.VHDL數(shù)字系統(tǒng)設(shè)計與高層次綜合[M].北京:電子工業(yè)出版社,2002