EDN博客精華文章 作者:ilove314

FPGA/CPLD重要設(shè)計思想及工程應用

時序及同步設(shè)計篇

這是昨晚的課程,主要講時鐘同步,課上做了一個實驗仿真的對比。(08.4.24)

概述

數(shù)字電路中,時鐘是整個電路最重要、最特殊的信號。

第一, 系統(tǒng)內(nèi)大部分器件的動作都是在時鐘的跳變沿上進行, 這就要求時鐘信號時延差要非常小, 否則就可能造成時序邏輯狀態(tài)出錯.

第二, 時鐘信號通常是系統(tǒng)中頻率最高的信號.

第三, 時鐘信號通常是負載最重的信號, 所以要合理分配負載。出于這樣的考慮在FPGA這類可編程器件內(nèi)部一般都設(shè)有數(shù)量不等的專門用于系統(tǒng)時鐘驅(qū)動的全局時鐘網(wǎng)絡(luò)。這類網(wǎng)絡(luò)的特點是:一、負載能力特別強, 任何一個全局時鐘驅(qū)動線都可以驅(qū)動芯片內(nèi)部的觸發(fā)器; 二是時延差特別小; 三是時鐘信號波形畸變小, 工作可靠性好。

因此, 在FPGA設(shè)計中最好的時鐘方案是: 由專用的全局時鐘輸入引腳驅(qū)動單個主時鐘去控制設(shè)計項目中的每一個觸發(fā)器。同步設(shè)計時, 全局時鐘輸入一般都接在器件的時鐘端, 否則會使其性能受到影響。

對于需要多時鐘的時序電路, 最好選用一個頻率是它們的時鐘頻率公倍數(shù)的高頻主時鐘。

各個功能模塊要使用統(tǒng)一的復位電路。在使用帶時鐘的觸發(fā)器、計數(shù)器等有復位端的庫器件時, 一般應盡量使用有同步復位的器件。注意復位時保證各個器件都能復位, 以避免某些寄存器的初始狀態(tài)不確定而引起系統(tǒng)工作不可靠。

若想掌握時鐘設(shè)計方法首先需要了解建立時間和保持時間的概念。

建立時間(setup time):是指在觸發(fā)器的時鐘信號上升沿到來以前,數(shù)據(jù)穩(wěn)定不變的時間,如果建立時間不夠,數(shù)據(jù)將不能在這個時鐘上升沿被打入觸發(fā)器;保持時間(hold time):是指在觸發(fā)器的時鐘信號上升沿到來以后,數(shù)據(jù)穩(wěn)定不變的時間,如果保持時間不夠,數(shù)據(jù)同樣不能被打入觸發(fā)器。

對于一個設(shè)計項目來說,全局時鐘(或同步時鐘)是最簡單和最可預測的時鐘。在CPLD/FPGA設(shè)計中最好的時鐘方案是:由專用的全局時鐘輸入引腳驅(qū)動的單個主時鐘去鐘控設(shè)計項目中的每一個觸發(fā)器。只要可能就應盡量在設(shè)計項目中采用全局時鐘。CPLD/FPGA都具有專門的全局時鐘引腳,它直接連到器件中的每一個寄存器。這種全局時鐘提供器件中最短的時鐘到輸出的延時。

在許多應用中只將異步信號同步化還是不夠的,當系統(tǒng)中有兩個或兩個以上非同源時鐘的時候,數(shù)據(jù)的建立和保持時間很難得到保證,我們將面臨復雜的時間問題,那么這個時候怎么辦呢?

最好的方法是將所有非同源時鐘同步化,那么又怎么樣將非同源時鐘同步化呢?

我們可以使用帶使能端的D觸發(fā)器,并引入一個高頻時鐘(頻率高于系統(tǒng)中的所有源時鐘),便可以達到使系統(tǒng)中所有源時鐘同步的效果。

系統(tǒng)時鐘設(shè)計:

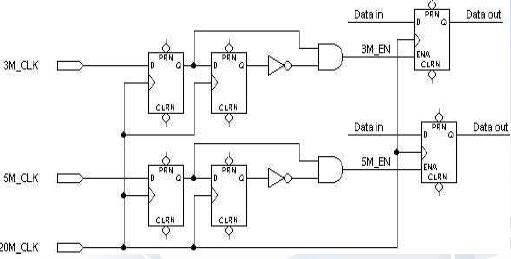

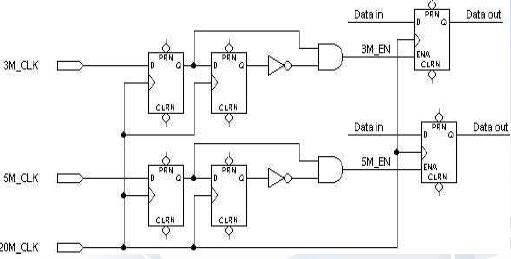

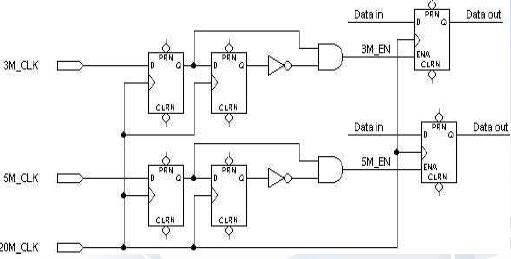

系統(tǒng)有兩個不同源時鐘,一個為3MHz,一個為5MHz,不同的觸發(fā)器使用不同的時鐘。為了系統(tǒng)穩(wěn)定,假設(shè)我們引入一個20MHz時鐘,那么這個20MHz的時鐘怎么才能將3M和5M時鐘同步化呢?

20M的高頻時鐘將作為系統(tǒng)時鐘,輸入到所有觸發(fā)器的的時鐘端。3M_EN 和5M_EN將控制所有觸發(fā)器的使能端。即原來接3M時鐘的觸發(fā)器,接20M時鐘,同時3M_EN 將控制該觸發(fā)器使能,原接5M時鐘的觸發(fā)器,也接20M時鐘,同時5M_EN 將控制該觸發(fā)器使能。這樣我們就可以將任何非同源時鐘同步化。

異步信號輸入總是無法滿足數(shù)據(jù)的建立保持時間,所以建議大家把所有異步輸入都先經(jīng)過雙觸發(fā)器進行同步化。

下面是用20MHz的時鐘作為同步時鐘得出的功能仿真波形:(下面一個小波形是將上面一個圖的EN_3信號的局部放大,可以明顯看出黃線前后兩個時鐘大小相差了一個主時鐘周期,這是因為20/3不為整數(shù)導致一個EN_3的脈沖周期有可能6個也有可能7個主時鐘周期)

15MHz的同步時鐘功能仿真波形,可以得到一致的EN_3和EN_5的脈沖,其高電平保持都為1/20M的時間。

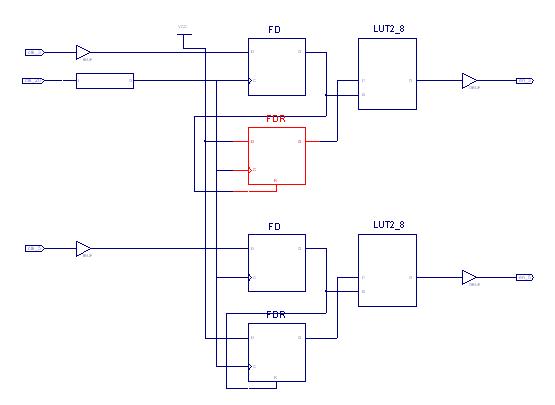

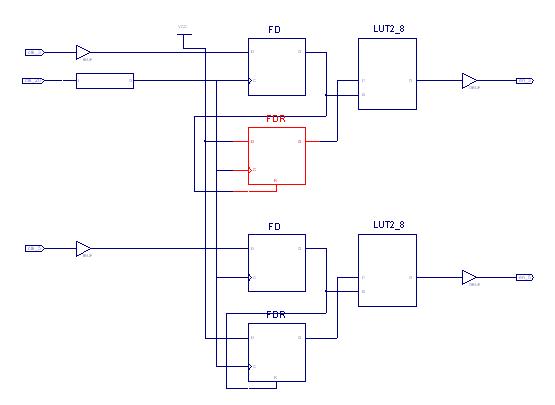

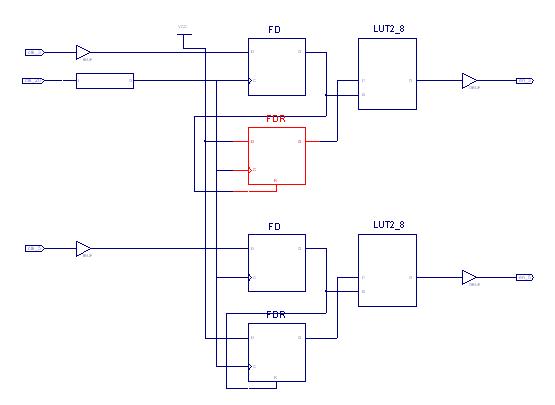

綜合后的原理圖:

在通常的FPGA設(shè)計中對時鐘偏差的控制主要有以下幾種方法:

1、控制時鐘信號盡量走可編程器件的的全局時鐘網(wǎng)絡(luò)。在可編程器件中一般都有專門的時鐘驅(qū)動器及全局時鐘網(wǎng)絡(luò),不同種類、型號的可編程器件,它們中的全局時鐘網(wǎng)絡(luò)數(shù)量不同,因此要根據(jù)不同的設(shè)計需要選擇含有合適數(shù)量全局時鐘網(wǎng)絡(luò)的可編程器件。一般來說,走全局時鐘網(wǎng)絡(luò)的時鐘信號到各使能端的延時小,時鐘偏差很小,基本可以忽略不計。

2、若設(shè)計中時鐘信號數(shù)量很多,無法讓所有的信號都走全局時鐘網(wǎng)絡(luò),那么可以通過在設(shè)計中加約束的方法,控制不能走全局時鐘網(wǎng)絡(luò)的時鐘信號的時鐘偏差。

3、異步接口時序裕度要足夠大局部同步電路之間接口都可以看成是異步接口,比較典型的是設(shè)計中的高低頻電路接口、I/O接口,那么接口電路中后一級觸發(fā)器的建立-保持時間要滿足要求,時序裕度要足夠大。

4、在系統(tǒng)時鐘大于30MHz時,設(shè)計難度有所加大,建議采用流水線等設(shè)計方法。

5、要保證電路設(shè)計的理論最高工作頻率大于電路的實際工作頻率。

復位和置位信號處理:

在設(shè)計時應盡量保證有一全局復位信號,或保證觸發(fā)器、計數(shù)器在使用前已經(jīng)正確清零狀態(tài)。在設(shè)計寄存器的清除和置位信號時,應盡量直接從器件的專用引腳驅(qū)動。另外,要考慮到有些器件上電時,觸發(fā)器處于一種不確定的狀態(tài),系統(tǒng)設(shè)計時應加入全局復位/Reset。

這樣主復位引腳就可以給設(shè)計中的每一個觸發(fā)器饋送清除或置位信號,保證系統(tǒng)處于一個確定的初始狀態(tài)。需要注意的一點是:不要對寄存器的置位和清除端同時施加不同信號產(chǎn)生的控制,因為如果出現(xiàn)兩個信號同時有效的意外情況,會使寄存器進入不定狀態(tài)。

![]()

![]()

![]()

![]()

![]()

![]()