由于獲取圖像的工具或手段的影響,使獲取圖像無法完全體現(xiàn)原始圖像的全部信息。因此,對圖像進(jìn)行預(yù)處理就顯得非常重要。預(yù)處理的目的是改善圖像數(shù)據(jù),抑制不需要的變形或者增強(qiáng)某些對于后續(xù)處理來說比較重要的圖像特征。

通常根據(jù)預(yù)處理目的的不同,把預(yù)處理技術(shù)歸為圖像增強(qiáng)技術(shù)和圖像分割技術(shù)兩類。圖像對比度處理是空間域圖像增強(qiáng)的一種方法。由于圖像灰度范圍狹窄會使圖像的對比度不理想,可用對比度增強(qiáng)技術(shù)來調(diào)整圖像灰度值的動態(tài)范圍。

圖像處理通常采用軟件或者DSP(數(shù)字信號處理器)來實(shí)現(xiàn)。如果利用軟件實(shí)現(xiàn),運(yùn)行時會耗費(fèi)較多的PC資源,而且算法越復(fù)雜時耗費(fèi)的資源就越多,對于需要高速處理的情況就不適用了;而如果采用DSP來實(shí)現(xiàn),提高并行性的同時指令執(zhí)行速度必然會提高,較高的指令速度可能導(dǎo)致系統(tǒng)設(shè)計(jì)復(fù)雜化,并增加功耗和成本。新一代的FPGA集成了CPU或DSP內(nèi)核,可以在一片F(xiàn)PGA上進(jìn)行軟硬件協(xié)同設(shè)計(jì),為實(shí)現(xiàn)SOPC提供了強(qiáng)大的硬件支持。本文介紹的是利用FPGA并行處理和計(jì)算能力,以Altera FPGA Stratix EP1S40為系統(tǒng)控制的核心實(shí)現(xiàn)的SOPC。

系統(tǒng)硬件平臺

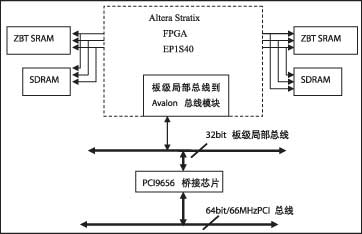

采用基于PCI總線的FPGA開發(fā)平臺,結(jié)構(gòu)如圖1所示。板上主要硬件資源有:PCI橋、FPGA、SRAM和SDRAM等其他外設(shè)。

PCI橋采用PCI9656橋接芯片實(shí)現(xiàn),用來連接PCI總線與32位/50MHz的板級局部總線;FPGA包括41 250個邏輯單元,14個DSP模塊,112個嵌入式乘法器,4個增強(qiáng)型PLL(鎖相環(huán))和4個快速型PLL等邏輯資源;SDRAM用來存儲圖像數(shù)據(jù)。Avalon總線模塊完成整個片上可編程系統(tǒng)組件之間的互連。Avalon總線是SOPC設(shè)計(jì)中連接片上處理器和其他IP模塊的一種簡單總線協(xié)議,規(guī)定了主、從構(gòu)件之間的端口連接以及通信時序關(guān)系,SOPC Builder來完成整個系統(tǒng)(包括Avalon)模塊的生成和集成。豐富的板級資源可以滿足圖像的高速預(yù)處理需求。

系統(tǒng)工作原理

設(shè)計(jì)采用DMA方式快速傳輸圖像數(shù)據(jù),這樣數(shù)據(jù)的傳輸和處理可以并行起來,使得系統(tǒng)的運(yùn)行效率大為提高。PC與PCI板卡之間建立軟件環(huán)境,在該環(huán)境下利用DMA通道把圖像數(shù)據(jù)從主機(jī)通過PCI總線、PCI橋、板級局部總線和Avalon總線傳到SDRAM存儲起來,然后送入算法邏輯模塊進(jìn)行處理,處理完成后再把圖像數(shù)據(jù)存儲到SDRAM中,最后再用DMA通道把圖像處理結(jié)果傳送回主機(jī)。

圖1 基于PCI總線的FPGA開發(fā)平臺

建立片上系統(tǒng)中的關(guān)鍵模塊

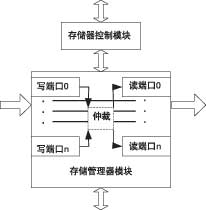

本文設(shè)計(jì)的圖像對比度增強(qiáng)系統(tǒng)是建立在Stratix EP1S40基礎(chǔ)上的SOPC。該設(shè)計(jì)在Quartus II 5.0中利用SOPC Builder將系統(tǒng)的工作頻率設(shè)為50MHz,器件系列設(shè)為Stratix,調(diào)用已經(jīng)建立的IP模塊和算法邏輯模塊,并設(shè)置各個模塊的時鐘和基地址,配置生成片上系統(tǒng)。根據(jù)任務(wù)要求,SOPC結(jié)構(gòu)框圖如圖2所示。

圖2 SOPC結(jié)構(gòu)框圖

圖2中,Avalon總線接口分為主(Master)和從(Slave)兩類,前者具有相接的Avalon總線的控制權(quán),后者是被動的。自定制的Avalon從外設(shè)根據(jù)對Avalon總線操作方式的不同分為兩類:一類是Avalon從(Slave)外設(shè),只是作為Avalon總線的一個從元件來處理;另一類是Avalon流模式從(Streaming Slave)外設(shè),需要使用Avalon總線的流傳輸模式,外設(shè)的設(shè)計(jì)更復(fù)雜。

● 板級局部總線與Avalon總線橋之間的通信模塊

在板級局部總線與FPGA內(nèi)部Avalon總線橋之間建立通信模塊。由于SOPC內(nèi)部各模塊之間的邏輯連接是由Avalon總線完成的,所以可以從主機(jī)通過PCI總線和板級局部總線訪問SOPC組件。該模塊作為Avalon總線的一個主控接口,對其他Avalon從外設(shè)和Avalon流模式從外設(shè)進(jìn)行訪問和控制。

● 控制模塊

控制模塊的工作時鐘獨(dú)立于系統(tǒng)時鐘,如圖3所示。包括兩個模塊的設(shè)計(jì):(1)用于對SDRAM存儲資源做合理分配的流模式存儲管理器模塊,它作為Avalon流模式從外設(shè),讀寫端口的數(shù)量可配置,這些讀寫端口可以以流傳輸模式把圖像數(shù)據(jù)讀出或?qū)懭隨DRAM。(2)存儲器控制模塊,它作為Avalon總線的另一主控接口,對作為Avalon總線從控接口的SDRAM控制器進(jìn)行控制。

圖3 控制模塊

● 圖像對比度增強(qiáng)算法及VHDL實(shí)現(xiàn)

在圖像對比度處理方法中,可以設(shè)計(jì)出不同的轉(zhuǎn)換函數(shù)。本系統(tǒng)是針對鋸齒形函數(shù)轉(zhuǎn)換設(shè)計(jì)的,鋸齒形轉(zhuǎn)換可以把幾段較窄灰度區(qū)間拉伸到較寬的灰度范圍內(nèi),這種處理可以把灰度變化較平緩的區(qū)域也較鮮明地顯示出來,從而增強(qiáng)圖像中感興趣的特征。

該設(shè)計(jì)對一幀3008×2000像素、數(shù)據(jù)寬度為8位的灰度圖像進(jìn)行處理,圖像共有2000行、3008列像素點(diǎn),行和列均從0開始計(jì)起。在系統(tǒng)時鐘上升沿、行有效信號與數(shù)據(jù)有效信號均有效時,把圖像數(shù)據(jù)讀入進(jìn)來,對其做相應(yīng)處理。每個系統(tǒng)時鐘上升沿讀入一個圖像數(shù)據(jù),在第N行像素點(diǎn)處理完后,第N+1行有效信號與數(shù)據(jù)有效信號必須同時有效才能繼續(xù)處理,在對第1999行、3007列像素點(diǎn)處理完畢后,行有效信號與數(shù)據(jù)有效信號置為無效,此時整幀圖像處理完畢。算法邏輯模塊中需要幀有效計(jì)數(shù)器和行有效計(jì)數(shù)器各一個,分別用來對幀和行進(jìn)行計(jì)數(shù),還需要一個像素計(jì)數(shù)器對某行像素做計(jì)數(shù)統(tǒng)計(jì)。由于該算法邏輯模塊是基于SOPC技術(shù),能夠在SOPC Builder工具中作為自定制模塊調(diào)用,需設(shè)置兩個寄存器,分別是幀有效計(jì)數(shù)寄存器和行有效計(jì)數(shù)寄存器,它們根據(jù)Avalon總線地址的不同,同時作為Avalon總線的讀或?qū)懠拇嫫鳎瑥亩棺远x模塊可以和Avalon總線進(jìn)行通信。每輸入一個像素點(diǎn)判斷其灰度值滿足設(shè)置的哪個區(qū)間范圍并做相應(yīng)轉(zhuǎn)換,從而實(shí)現(xiàn)一幀圖像的對比度增強(qiáng)處理。根據(jù)算法需求,采用VHDL語言對算法邏輯建模,并以Avalon總線從外設(shè)的方式在SOPC Builder 中調(diào)用。VHDL實(shí)現(xiàn)如下。

entity enhancement is

port (iLVAL : in std_logic;

iDVAL : in std_logic;

iFVAL : in std_logic := '1';

iCLK : in std_logic;

iDATA : in std_logic_vector(7 downto 0);

oLVAL : out std_logic; oDVAL : out std_logic;

oFVAL : out std_logic;

oDATA : out std_logic_vector (7 downto 0)

);

end enhancement;

這里iFVAL被置為“1”,說明是對一幀圖像進(jìn)行處理;iDATA與oDATA是圖像輸入、輸出二進(jìn)制數(shù)據(jù),寬度為8位。

圖像預(yù)處理系統(tǒng)的實(shí)現(xiàn)

用標(biāo)準(zhǔn)化硬件描述語言VHDL建立FPGA模塊實(shí)現(xiàn)。按照自頂向下的設(shè)計(jì)方法生成各設(shè)計(jì)階層,將設(shè)計(jì)任務(wù)分解為不同的功能元件,每個元件具有專門定義的輸入輸出端口并執(zhí)行各自的邏輯功能。該SOPC設(shè)計(jì)通過以下步驟實(shí)現(xiàn)。

(1)利用SOPC Builder工具編譯生成用戶自定制模塊,調(diào)用已建立的IP模塊并設(shè)置參數(shù),配置生成片上系統(tǒng);

(2)在頂層VHDL文件中調(diào)用模塊并示例化,進(jìn)行信號連接;

(3)對整個系統(tǒng)進(jìn)行管腳等約束設(shè)置,全編譯并進(jìn)行行為和時序驗(yàn)證;

(4)下載和硬件調(diào)試完成。

結(jié)束語

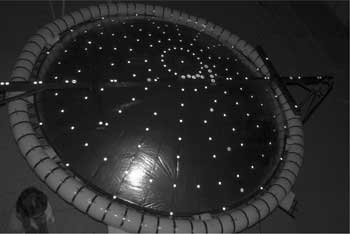

該系統(tǒng)對實(shí)驗(yàn)室在光線較弱情況下所拍的一幀3008×2000灰度圖像進(jìn)行對比度增強(qiáng)處理,處理前后如圖4、5所示。在SOPC系統(tǒng)時鐘為50MHz時,對于輸入大小為3008×2000像素點(diǎn)的灰度圖像,每一幀的處理時間為T=(1/(50×106))×3008×2000=0.120 32s。

圖4 原圖像

圖5 處理后圖像

而在3GHz Pentium 4、256MB內(nèi)存的PC上通過Matlab用代碼實(shí)現(xiàn)則需0.9850s。該設(shè)計(jì)采用FPGA實(shí)現(xiàn)圖像預(yù)處理系統(tǒng),與利用軟件處理圖像的方法比較起來,可以更快速地實(shí)現(xiàn)對圖像的預(yù)處理。同時系統(tǒng)構(gòu)成靈活,設(shè)計(jì)中模塊的可重復(fù)開發(fā)性降低了生產(chǎn)成本、縮短了生產(chǎn)周期,提高了工作效率。