目前,,變頻調速一般采用微處理器和專用芯片來實現(xiàn),。但是普通的專用芯片運算速度受微處理器系統(tǒng)時鐘影響,且開發(fā)周期長,,硬件調試不方便[1],。隨著微電子技術和EDA軟件的發(fā)展,出現(xiàn)的FPGA幾乎克服了所有這些不足,,所以本設計采用了FPGA方案,。

三相SPWM的產生一般可以通過三相相位上互差120°的正弦波與三角波比較來實現(xiàn)。三相正弦表可以由三個獨立的相位互差120°的正弦表組成,,這在設計思路上是簡單的,,但實際中卻有很大的浪費。

目前有人采用了分時復用的方法來減少三相正弦表所占用的邏輯門[1],。從正弦波的波形可以看出,,正弦波具有很好的對稱性,還能對正弦表再進行優(yōu)化,。

因此,,本文提出了利用分時復用以及正弦波的對稱性,對三相正弦表進一步優(yōu)化,,以進一步減少正弦表所占用的邏輯門,,提高FPGA的利用率。

1 數(shù)據的合成

數(shù)據合成由分時復用電路和運算電路兩部分組成,。通過分時復用,,使得所需的正弦表減少到原來的1/3,即產生三相正弦波只需一個正弦表,。運算電路利用正弦波的對稱性,,使得實現(xiàn)一個完整周期的正弦波只需1/4周期的正弦表。兩者結合,,從而完成三相正弦波只需一個1/4周期的 正弦表,,達到最大程度的節(jié)省資源的目的,。

1.1 分時復用原理及其應用

分時復用的原理是各路信號占用同一信道的不同時間間隙進行信號傳輸。具體到本電路就是利用對正弦表尋址的高速度,,使一個正弦表在不同時間段查詢不同相的正弦波的幅值,,以達到減少正弦表所占用的FPGA資源的目的?! ?/p>

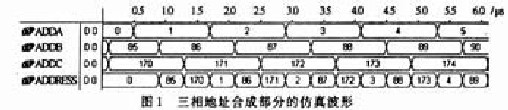

電路的具體實現(xiàn):三路在相位上互差120°的地址數(shù)據并行輸入,,通過一個三選一的選擇器來進行選擇,選擇器的控制端接三進制的計數(shù)器[1],。如,,計數(shù)器為0時,輸出的是A相的地址,。計數(shù)器為1時,,輸出的是B相的地址。計數(shù)器為2時,,輸出的是C相的地址,。因此只要使輸入的三相地址周期性變化,就實現(xiàn)了并行輸入的三相地址數(shù)據在時間上形成了連續(xù),,也就實現(xiàn)了三相地址數(shù)據的合成,。這樣就可以利用一個正弦表來得到三相的正弦值。把正弦表減少到沒有采用分時復用時的1/3,。該部分電路的仿真波形如圖1所示,。圖中ADDA,ADDB,,ADDC分別為A相,,B相和C相的相位值。ADDRESS為合成一路后的相位值,。

1.2 正弦波的對稱性及其應用

由正弦波波形可知,,正弦波具有很好的對稱性。π/2~π的幅值大小與0~π/2的幅值大小相同,,只是他們在時間上出現(xiàn)的順序剛好相反,。π~3π/2的幅值與0~π/2的幅值的絕對值相同,極性相反,。3π/2~2π部分的幅值與π~3π/2的大小相等,,只是時間上出現(xiàn)的順序相反。因此,,根據正弦波的對稱性,,只在正弦表ROM中存有相位0~π/2時的幅值。利用0~π/2相位時的幅值產生完整的正弦波波形。 產生正弦波首先需要對正弦表進行尋址,,把量化的相位值轉化為對應的量化的幅值,。由于正弦表ROM中僅存有相位0~π/2時的幅值,而π/2~π,,3π/2~2π的絕對值與相位0~π/2的幅值在時間上出現(xiàn)的順序相反,,因此,要獲得π/2~π,,3π/2~2π的幅值必須對相位0~π/2時的幅值進行反向尋址,。反相尋址通過地址輸入矢量取反來實現(xiàn)[2],。本設計把周期2π量化為8位,,即對一個正弦波周期進行256次取樣。因此對0~π/2相位尋址所需的地址線為64條,。ADDRESS定義為STD_LOGIC_VECTOR(7DOWNTO0),,ADDRESS低6位用于對ROM表進行尋址,當?shù)刂窋?shù)據ADDRESS(6)為“1”時,,對地址ADDRESS的低6位取反再對ROM尋址,。

正弦波的負半周的形成。由于負半周的幅值與正半周的幅值在極性上相反,,因此對輸出的對應的幅值取反,。幅值是否取反由輸入的地址數(shù)據ADDRESS(7)決定,當ADDRESS(7)為“1”時,,對應的輸出幅值取反[2],。并把ADDRESS(7)取反作為最終輸出的正弦波幅值的最高位。這樣做實際上把正弦波向Y軸正方向平移了一個幅值,,避免了幅值出現(xiàn)負值,。

這樣在分時復用的基礎上,通過利用正弦波的對稱性,,完成了三相數(shù)據只需一個1/4周期的ROM即可查詢,。在分時復用和利用正弦波對稱性2個相對獨立的模塊連接的過程中必須考慮到時序的問題。如果只是把2個模塊簡單的連接到一塊,,只能產生一相的SPWM,,如果時序上解決不好,產生的三相正弦波精度會受到影響,,一個周期的正弦波不再由256個點組成,,如果這樣,也就失去了優(yōu)化的意義,。

2 數(shù)據的分離

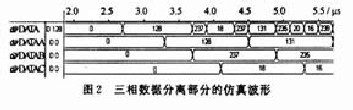

由以上可知,,從一個1/4正弦波周期的ROM表中可以得到三相相位互差120°的正弦波的幅值,但是由于輸入的三相地址在時間上是連續(xù)的,即對ROM表尋址的地址只有一路,,因此,,雖然得到了三相正弦波的幅值,可是他們是按ADDRESS中各相之間的關系混合在一起的,。因此,,必須對所得到的幅值進行分離,才能得到三相正弦波,。由波形ADDRESS中各相地址的相互關系可知,,分離數(shù)據只要把分時復用的合成部分反接即可,仿真波形如圖2所示(為了使在同一個波形中可以同時看清DATA中的各項數(shù)據,,圖2對MAXPLUSⅡ的仿真波形的2.0μs之前的輸出零部分進行了截去,。)圖中DATA為根據1/4周期正弦表所得的三相混合數(shù)據,DATAA,,DATAB,,DATAC分別為分離后A相,B相和C相的相位對應的幅值,。由三相正弦波幅值之間的相互關系和變化趨勢可以得知,,輸出的數(shù)據是正確的。最后把所得的三相數(shù)據鎖存,,再與產生的三角波比較產生三相六路SPWM,。

3 結語

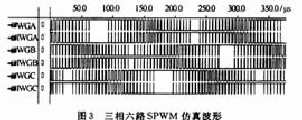

由以上分析及仿真可知,采用一個1/4周期的正弦表實現(xiàn)三相正弦數(shù)據的查詢是可行的,。這將極大的節(jié)省所用FPGA的門數(shù),,提高其利用率,極大地降低編程的勞動量,,且輸出的三相正弦波與不利用分時復用和正弦波對稱性時相比,,精度不受任何影響,每個正弦周期還是由256個點組成,,只是正弦波的頻率有所降低,,這是由于系統(tǒng)的速度和占用面積之間本來就是一種矛盾。圖3是本次設計產生的三相六路SPWM,,系統(tǒng)仿真的時鐘周期為200ns,,由于FPGA的系統(tǒng)時鐘頻率可以達到很高,所以不會對輸出的SPWM頻率產生影響,。

參考文獻

?。?]李明峰,葉劍利.分時復用時CPLD設計變頻系統(tǒng)中的應用[J].單片機與嵌入式系統(tǒng)應用,,2002.[2]DanielJ.Modulating direct digital synthesizer in a quicklogic FPGA.[3]潘松,,王國棟.VHDL實用教程[M].成都:電子科技大學出版社,2000.