隨著大規(guī)模集成電路及高速數(shù)字信號處理器的發(fā)展,通信領(lǐng)域的信號處理越來越多地在數(shù)字域付諸實(shí)現(xiàn)。軟件鎖相技術(shù)是隨著軟件無線電的發(fā)展和高速DSP的出現(xiàn)而開展起來的一個(gè)研究課題。在軟件無線電接收機(jī)中采用的鎖相技術(shù)是基于數(shù)字信號處理技術(shù)在DSP等通用可編程器件上的實(shí)現(xiàn)形式,由于這一類型鎖相環(huán)的功能主要通過軟件編程實(shí)現(xiàn),因此可將其稱為軟件鎖相環(huán)(software PLL)[1]。

盡管軟件鎖相環(huán)采用的基本算法思想與模擬鎖相環(huán)和數(shù)字鎖相環(huán)相比并沒有太大變化,然而其實(shí)現(xiàn)方式卻完全不同。本文將建立軟件鎖相環(huán)的Z 域模型,分析軟件鎖相環(huán)中的延時(shí)估計(jì)、捕獲速度及多速率條件下的軟件鎖相環(huán)模型問題[1]。

1軟件鎖相環(huán)的基本模型

在模擬鎖相環(huán)的基礎(chǔ)上,利用數(shù)字、模擬系統(tǒng)彼此之間的聯(lián)系,以二階二型鎖相環(huán)為例建立軟件鎖相環(huán)的Z 域模型。文獻(xiàn)[2]詳細(xì)給出了鎖相環(huán)的基本模型和原理。

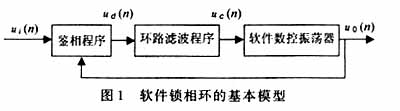

如果將鎖相環(huán)的基本部件采用軟件編程的形式實(shí)現(xiàn),就可以得到軟件鎖相環(huán)的基本組成,如圖1所示。

首先從模擬鎖相環(huán)的S域模型出發(fā)得到軟件鎖相環(huán)的Z 域模型(二階二型模擬鎖相環(huán)的S域模型請參閱文獻(xiàn)[2])。由于雙線性變換是聯(lián)系模擬系統(tǒng)與數(shù)字系統(tǒng)的一個(gè)重要方法,具有轉(zhuǎn)換簡單且表達(dá)式清晰明了的特點(diǎn)[3],因此本文選擇雙線性變換法作為模擬鎖相環(huán)與軟件鎖相環(huán)之間的轉(zhuǎn)換基礎(chǔ)。

式(1)是雙線性變換法的復(fù)頻域表達(dá)式:

![]()

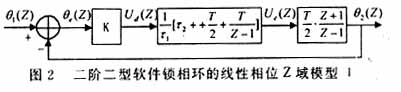

其中:T是聯(lián)系數(shù)字系統(tǒng)與模擬系統(tǒng)的采樣時(shí)間間隔,1/T表示采樣頻率。根據(jù)該轉(zhuǎn)換關(guān)系,對S域模型各部分對應(yīng)的數(shù)字復(fù)頻域表達(dá)式進(jìn)行轉(zhuǎn)換,可以得到如圖2所示的復(fù)頻域模型。

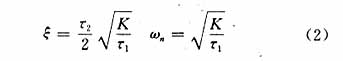

在實(shí)際應(yīng)用中,二階線性系統(tǒng)常采用阻尼因子ξ、無阻尼振蕩頻率ωn描述。在二階二型鎖相環(huán)中,τ1,τ2 ,K 與ξ,ωn之間的對應(yīng)關(guān)系如下:

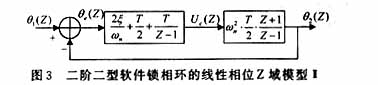

在式(1)和式(2)的基礎(chǔ)上對圖2進(jìn)行等效變換,可以得到軟件鎖相環(huán)的另一個(gè)線性相位Z域模型,如圖3所示。

在模型Ⅰ中,參數(shù)τ1,τ2和K與實(shí)現(xiàn)電路功能的電阻、電容、壓控振蕩器密切相關(guān)。而實(shí)現(xiàn)軟件鎖相功能的卻是乘法器、加法器與寄存器,因此采用模型Ⅱ表征軟件鎖相環(huán)線性相位Z域模型顯得更有實(shí)際意義。

2軟件鎖相環(huán)的數(shù)學(xué)模型

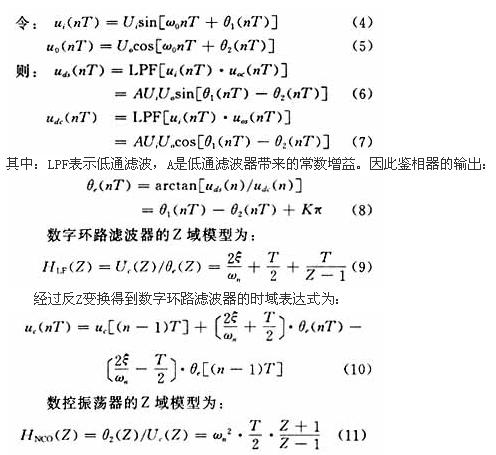

數(shù)字鑒相器的Z域模型如下:

![]()

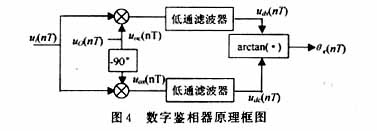

實(shí)現(xiàn)數(shù)字鑒相器的方法之一就是借助信號的正交分解,圖4是該方法的原理框圖。

如果以數(shù)字頻率描述數(shù)控振蕩器,則稱其數(shù)字中心頻率為ω0T,數(shù)字偏置頻率為ωn2·uc(nT)·T。因此,該數(shù)控振蕩器的靈敏度與數(shù)字靈敏度分別為·T。

3多速率條件下的軟件鎖相環(huán)

在數(shù)字化接收機(jī)中,經(jīng)常碰到多速率條件下的抽樣率轉(zhuǎn)換問題。所謂多速率系統(tǒng)是指在一個(gè)數(shù)字系統(tǒng)中存在2個(gè)或2個(gè)以上的抽樣率[4]。構(gòu)成軟件鎖相環(huán)鑒相器的混頻器通常工作在系統(tǒng)采樣頻率上。在滿足奈奎斯特采樣定律的前提下,數(shù)字化接收機(jī)的系統(tǒng)采樣率一般高達(dá)數(shù)10 M。而數(shù)字鑒相器組成部分的反正切表,由于混頻之后的數(shù)據(jù)經(jīng)過多倍抽取,工作頻率已經(jīng)下降到與信號波特率相近的水平。數(shù)據(jù)抽取同時(shí)也降低DSP的運(yùn)算量,由DSP完成的環(huán)路濾波的處理速度近似等于信號波特率。此外由于軟件鎖相環(huán)中的數(shù)控振蕩器需要給混頻器提供同樣速率的正交載波,其工作速率與混頻器相等,需要進(jìn)行內(nèi)插來調(diào)整速率。

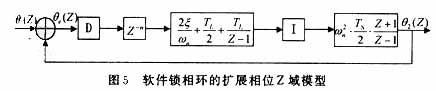

為了合理利用DSP有限的計(jì)算資源,總是在滿足同步需要的前提下盡可能地降低環(huán)路濾波的工作速率,也就是通常所說的環(huán)路頻率。環(huán)路頻率是軟件鎖相環(huán)的一個(gè)重要參數(shù),他同時(shí)決定著鎖相環(huán)算法的計(jì)算量與捕獲速度。環(huán)路頻率過高將帶來額外的計(jì)算負(fù)擔(dān),環(huán)路頻率太低又不能滿足捕獲速度的需要,在應(yīng)用中通常取系統(tǒng)波特率作為環(huán)路頻率的大小。該擴(kuò)展模型對應(yīng)的線性相位Z域模型如圖5所示。

其中:D表示數(shù)據(jù)抽取,I表示數(shù)據(jù)內(nèi)插。數(shù)據(jù)在抽取之前先要進(jìn)行抗混疊濾波,可用于抗混疊濾波的FIR濾波器有CIC濾波器、半帶濾波器等。

實(shí)際情形中,由于零階保持內(nèi)插幾乎不需要額外的運(yùn)算量,因此經(jīng)常被采用。實(shí)際上環(huán)路頻率fL總是能夠跟上環(huán)路濾波器輸出信號的變化速率。換言之,對環(huán)路濾波器輸出信號按照fL的速率進(jìn)行采樣保留了他的全部信息,因此零階保持內(nèi)插對系統(tǒng)性能不會有太大影響[4]。

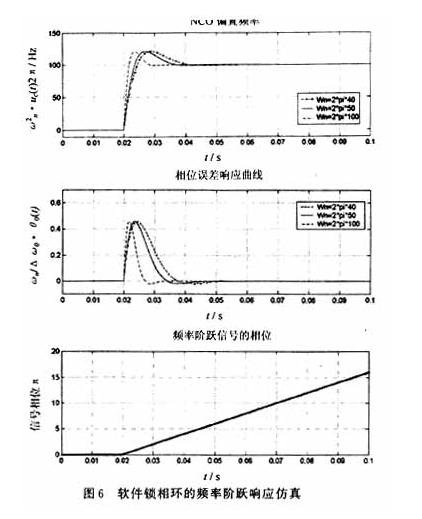

結(jié)合上述軟件鎖相環(huán)的基本原理,下面借助Matlab仿真觀察軟件鎖相環(huán)的系統(tǒng)響應(yīng)。本文以頻率階躍信號作為輸入,觀察軟件鎖相環(huán)的系統(tǒng)響應(yīng)從而進(jìn)一步驗(yàn)證本文建立的一系列軟件鎖相環(huán)模型。

設(shè)定系統(tǒng)采樣頻率為1 MHz,仿真時(shí)間0.1 s,信號中心頻率125 kHz,起始相位-π/4,輸入頻率階躍100 Hz,起始點(diǎn)為0.02 s,抽取因子為8。一般情況下,都希望環(huán)路工作在欠阻尼狀態(tài),取阻尼因子ξ=0.707,ωn由2π

ΔF(快捕帶寬)決定[2],分別取2π*40,2π*50,2π*100。仿真出相位誤差響應(yīng)曲線、NCO偏置頻率曲線和頻率階躍信號的相位曲線,如圖6所示。

從圖6可以看出,軟件鎖相環(huán)在[0,0.02]區(qū)間內(nèi)相位誤差為0,處于鎖定狀態(tài)。在t=0.02 s時(shí)刻,輸入信號頻率產(chǎn)生了大小為100 Hz的階躍,導(dǎo)致軟件鎖相環(huán)進(jìn)入捕獲過程。由于軟件鎖相環(huán)的校正作用,當(dāng)ωn=2π*50時(shí),系統(tǒng)在t=0.05 s時(shí)刻重又進(jìn)入同步狀態(tài),相位誤差依舊為0。由相位誤差響應(yīng)曲線可以看到,鎖相環(huán)可以無相差的跟蹤頻率階躍信號,同時(shí)表明雖然鎖相環(huán)鑒相誤差為0,但是由于環(huán)路濾波器的理想積分作用其輸出的控制信號并不為0,由該控制信號產(chǎn)生的100 Hz偏置頻率保證了NCO輸出與輸入信號的同步。當(dāng)快捕帶寬發(fā)生變化導(dǎo)致改變時(shí),鎖相環(huán)的捕獲速度也發(fā)生了變化,快捕帶寬越寬,捕獲速度越快。

4軟件鎖相環(huán)的DSP實(shí)現(xiàn)

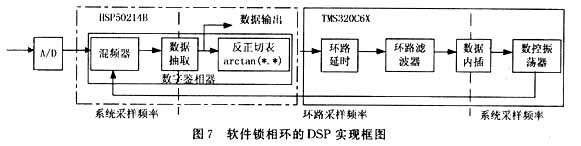

在寬帶數(shù)字化接收機(jī)的實(shí)現(xiàn)中,數(shù)字下變頻采用通用可編程下變頻器HSP50214B。在實(shí)現(xiàn)載波同步、碼元同步軟件鎖相環(huán)的整個(gè)反饋環(huán)路中,數(shù)控振蕩器、鑒相器由HSP50214B完成,環(huán)路濾波在TMS320C6X中完成。DSP實(shí)現(xiàn)框圖如圖7所示。

環(huán)路延時(shí)是一個(gè)應(yīng)該重視的因素。帶來軟件鎖相環(huán)環(huán)路延時(shí)主要有以下2種原因:

(1)環(huán)路內(nèi)FIR濾波器帶來的延時(shí);

(2)數(shù)據(jù)等待處理帶來的額外延時(shí)。

在數(shù)字化接收機(jī)中,采用粗同步與細(xì)同步兩級。粗同步環(huán)路時(shí)延大,反應(yīng)速度慢;細(xì)同步環(huán)路時(shí)延小,反應(yīng)速度快,粗同步保證有效信號落在濾波器的通帶之內(nèi),細(xì)同步可以在粗同步基礎(chǔ)上獲得較大捕獲帶和同步帶。此外還采用拋棄若干采樣點(diǎn),消除不必要的環(huán)路延時(shí)。

可以看出,軟件鎖相環(huán)具有處理靈活的優(yōu)點(diǎn),他擺脫了復(fù)雜的硬件電路設(shè)計(jì),解決了許多模擬環(huán)遇到的難題。目前,由于DSP功能越來越強(qiáng)大,工作速度越來越高,也為軟件鎖相技術(shù)的發(fā)展創(chuàng)造了必要的條件。

參考文獻(xiàn)

[1]Best R LPhase locked loops design simulation and applications[M]. 3rd EditionMcGraw Hill, 1997

[2]張厥盛鎖相技術(shù)[M].西安:西安電子科技大學(xué)出版社,1994

[3]丁玉美數(shù)字信號處理[M].西安:西安電子科技大學(xué)出版社,1995

[4]宗孔德多抽樣率信號處理[M].北京清華大學(xué)出版社,1996

[5]HARRIS公司,The principle and application of HSP50214B

[6]John Proakis GDigital communications[M].北京:電子工業(yè)出版社,1999