使用創(chuàng)新性邏輯技術(shù)降低移動(dòng)設(shè)計(jì)功耗

Sean Ryan

飛兆半導(dǎo)體

摘要: 當(dāng)前的移動(dòng)設(shè)計(jì)努力在高耗能(power-rich)的功能性和更長(zhǎng)電池壽命的需求之間取得平衡。本文將探討在混合電壓供電的移動(dòng)設(shè)計(jì)中,混合電壓電平如何提高ICC電源電流及邏輯門(mén)如何降低功耗。

Abstract:

Key words :

當(dāng)前的移動(dòng)設(shè)計(jì)努力在高耗能(power-rich)的功能性和更長(zhǎng)電池壽命的需求之間取得平衡。本文將探討在混合電壓供電的移動(dòng)設(shè)計(jì)中,混合電壓電平如何提高ICC電源電流及邏輯門(mén)如何降低功耗。

低ICCT技術(shù)有利于節(jié)能

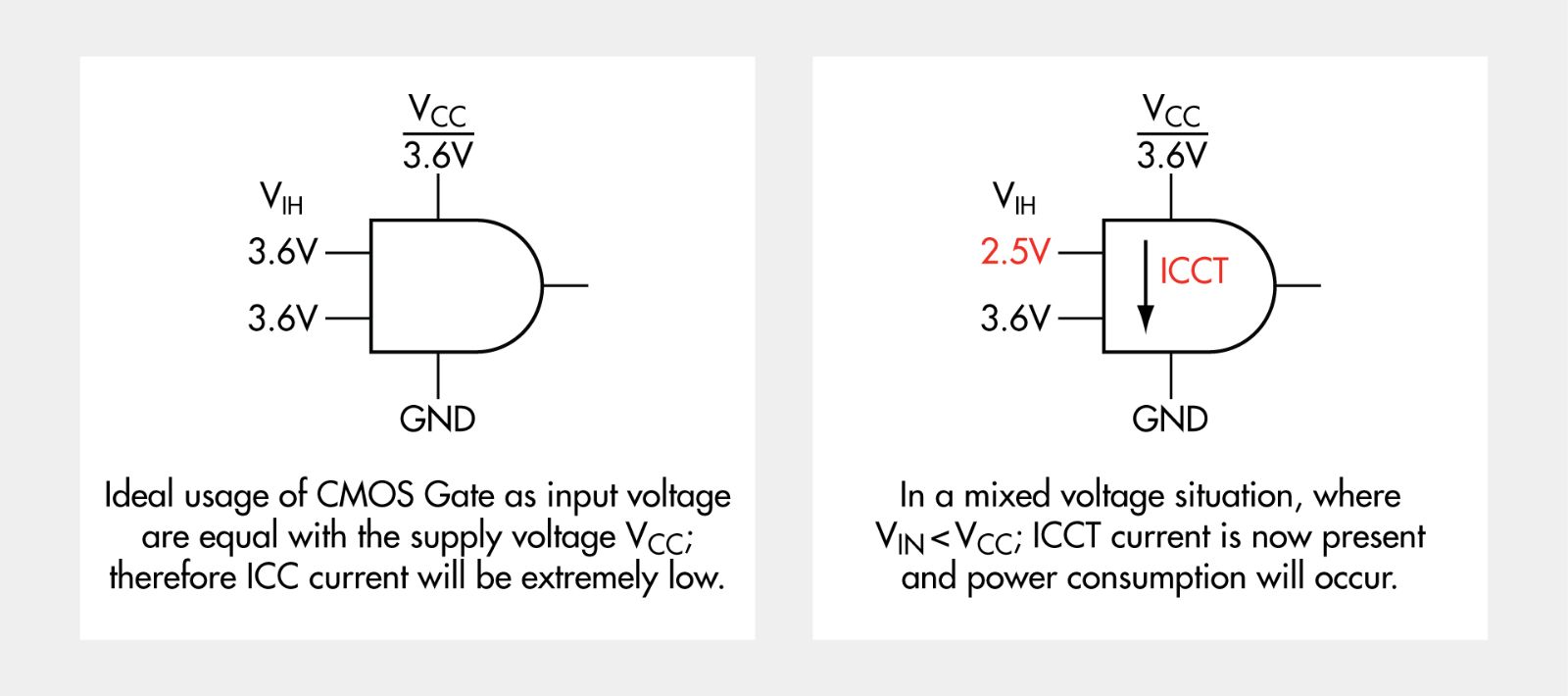

目前,大多數(shù)便攜設(shè)備都備有多個(gè)電源軌,但在輸入高電平(VIH)低于電源電壓(VCC)時(shí),仍可能產(chǎn)生不定功耗。當(dāng)輸入電壓為電源軌電平(VIL = Gnd 或 VIH = VCC)時(shí),CMOS一般具有極低的靜態(tài)ICC和泄漏電流,故是移動(dòng)應(yīng)用中邏輯器件的首選技術(shù)。不過(guò),若VIH < VCC,會(huì)發(fā)生這種情況:輸入級(jí)的PMOS和NMOS晶體管可能均在不同級(jí)“導(dǎo)通”,此時(shí)傳導(dǎo)電流,在這個(gè)狀態(tài)期間,靜態(tài)電流ICC增加,存在一條從VCC到Gnd的路徑。這個(gè)增加的電流被稱(chēng)為ICCT電流,亦是輸入電壓逼近閾值時(shí)的電源電流。圖1描述了這種情況。

圖1 邏輯門(mén)和輸入電壓條件

注釋?zhuān)?輸入電壓等于電源電壓Vcc時(shí)為使用CMOS門(mén)電路的理想狀態(tài);這時(shí)ICC電流極低。

*在混合電壓情況下,若Vin < VCC,ICCT電流出現(xiàn),功耗也隨之產(chǎn)生。

一般在CMOS門(mén)電路的設(shè)計(jì)中,輸入電壓閾值或輸入切換點(diǎn)為VCC/2;不過(guò),飛兆半導(dǎo)體的低ICCT門(mén)電路采用專(zhuān)有的輸入電壓設(shè)計(jì),可降低輸入閾值電壓,增大輸入電壓范圍,同時(shí)不影響有效邏輯低電平VIL。如前所述,當(dāng)輸入電壓為0V或VCC時(shí),CMOS門(mén)電路的耗電量極低,而產(chǎn)品數(shù)據(jù)手冊(cè)通常會(huì)注明該條件下的ICC。因此,系統(tǒng)設(shè)計(jì)人員在VIH值小于VCC時(shí)看到ICC電流增大可能頗為驚訝。圖2顯示了一個(gè)重新設(shè)計(jì)的輸入結(jié)構(gòu)的優(yōu)點(diǎn)。

VIN - ICC圖比較了一個(gè)標(biāo)準(zhǔn)CMOS輸入器件(紅色線條)和一個(gè)低ICCT輸入器件(藍(lán)色線條)。靜態(tài)功率由基本DC功率公式?jīng)Q定:P = ICC * VCC。在本例中,輸入VIH為2.5V,標(biāo)準(zhǔn)CMOS門(mén)電路輸入的功耗等于3.0mW (3.6V x 0.83mA) ,而低ICCT門(mén)電路的功耗只有0.003mW (3.6V x 0.99uA);也就是說(shuō),利用Low ICCT器件,靜態(tài)功耗降低了100%。

圖2 ICC -VIN輸入曲線 (Vcc = 3.6V, VIN = 2.5V)

ICC電流的增大十分重要,因?yàn)樗鼤?huì)大幅度增加器件的靜態(tài)功耗。飛兆半導(dǎo)體的專(zhuān)有低ICCT輸入結(jié)構(gòu)可在ICCT電流出現(xiàn)期間限制其范圍,如圖2所示。

表1 不同VIH條件下的節(jié)能潛力

|

|

|

ICCT 電流

|

|

|

|

VCC

|

VIN

|

標(biāo)準(zhǔn) CMOS 門(mén)電路

|

低ICCT 門(mén)電路

|

節(jié)能

|

|

3.6

|

3.6

|

5.1 nA

|

1.5 nA

|

70%

|

|

3.6

|

2.5

|

830 uA

|

996 pA

|

100%

|

|

3.6

|

1.8

|

7.0 mA

|

2.7 uA

|

100%

|

|

3.6

|

1.5

|

2.8 mA

|

3.5 uA

|

100%

|

|

2.5

|

2.5

|

1.2 nA

|

983 pA

|

23%

|

|

2.5

|

1.8

|

21.4 uA

|

39.2nA

|

100%

|

|

2.5

|

1.5

|

417 uA

|

577 nA

|

100%

|

|

1.8

|

1.8

|

835 pA

|

656 pA

|

21%

|

|

1.8

|

1.5

|

2.6 nA

|

713 pA

|

73%

|

|

1.8

|

1.2

|

2.6 uA

|

4.6 nA

|

100%

|

表1比較了不同VCC/VIN條件下的ICCT電源電流級(jí)。從表中可看出,飛兆半導(dǎo)體的低ICCT門(mén)電路具有很大的節(jié)能潛力。在混合電壓系統(tǒng)中,利用低ICCT門(mén)電路,與邏輯門(mén)電路相關(guān)的功耗可降至微不足道。

請(qǐng)參考表2列出的低ICCT門(mén)電路供貨情況。根據(jù)需要可以提供額外的功能。當(dāng)現(xiàn)有應(yīng)用因前面討論的輸入條件而出現(xiàn)功耗過(guò)大時(shí),用戶(hù)可利用標(biāo)準(zhǔn)引腳輸出,直接簡(jiǎn)便地進(jìn)行替換。

表2 飛兆半導(dǎo)體的NC7SVL 低ICCT門(mén)電路

|

門(mén)電路功能

|

產(chǎn)品編號(hào)

|

封裝

|

供貨

|

|

逆變器

|

NC7SVL04L6X

|

MicroPak™

|

現(xiàn)貨

|

|

NC7SVL04FHX

|

MicroPak 2

|

||

|

NC7SVL04P5X

|

SC-70

|

||

|

AND(與門(mén))

|

NC7SVL08L6X

|

MicroPak

|

|

|

NC7SVL08FHX

|

MicroPak 2

|

||

|

NC7SVL08P5X

|

SC-70

|

||

|

OR(或門(mén))

|

NC7SVL32L6X

|

MicroPak

|

|

|

NC7SVL32FHX

|

MicroPak 2

|

||

|

NC7SVL32P5X

|

SC-70

|

總結(jié)

延長(zhǎng)電池壽命的要訣是降低各級(jí)的功率。隨著便攜設(shè)備整合更多的功能,功耗問(wèn)題越來(lái)越令人擔(dān)憂。飛兆半導(dǎo)體的NC7SVL低ICCT TinyLogic產(chǎn)品為解決這些難題提供了一個(gè)具成本效益的解決方案。此外,飛兆半導(dǎo)體先進(jìn)的小尺寸MicroPak封裝技術(shù),以及新推出的更小的1.0x1.0mm MicroPak 2封裝技術(shù),可顯著降低線路板空間要求。

對(duì)于功率預(yù)算十分緊張的便攜應(yīng)用產(chǎn)品來(lái)說(shuō),耗電量的增加是不能接受的。NC7SVL低 ICCT門(mén)電路能夠幫助系統(tǒng)設(shè)計(jì)人員在將功率保持在預(yù)算之內(nèi),并延長(zhǎng)電池壽命。

此內(nèi)容為AET網(wǎng)站原創(chuàng),未經(jīng)授權(quán)禁止轉(zhuǎn)載。