目前廣泛應(yīng)用的MIMU/GPS組合導(dǎo)航系統(tǒng)的實(shí)現(xiàn)形式,依應(yīng)用領(lǐng)域的不同而復(fù)雜多樣,但是導(dǎo)航計(jì)算機(jī)板卡負(fù)責(zé)的工作則相對(duì)固定,其主要包括:采集各路傳感器輸入信號(hào);濾波、融合計(jì)算;將計(jì)算結(jié)果輸送給機(jī)電控制子系統(tǒng);提供各種人機(jī)交互接口,如LCD,鍵盤等。

長(zhǎng)期以來,針對(duì)各種應(yīng)用領(lǐng)域或相同領(lǐng)域的不同場(chǎng)合,由于對(duì)控制計(jì)算能力、接口電路數(shù)據(jù)吞吐能力等要求的差異,我們習(xí)慣于把功能相對(duì)固定的導(dǎo)航計(jì)算機(jī)子系統(tǒng)設(shè)計(jì)成不同的實(shí)現(xiàn)形式,這就造成了對(duì)硬件重復(fù)研發(fā),相應(yīng)軟件重復(fù)調(diào)整等低效率現(xiàn)狀。

SOPC(System On Programmable Chip)技術(shù)是Altera公司提出的一種靈活高效的SOC解決方案。它的宗旨是將處理器、存儲(chǔ)器、I/O口、硬件協(xié)處理器或加速器、一般的用戶邏輯等系統(tǒng)的設(shè)計(jì)需要的功能模塊都集成到一個(gè)FPGA芯片里,構(gòu)建一個(gè)可編程的片上系統(tǒng)。它具有硬件上靈活裁剪、擴(kuò)充和在線升級(jí)的優(yōu)點(diǎn),而且市場(chǎng)上有豐富的IP 核資源可選,能成功地解決上述問題。

1.組合導(dǎo)航系統(tǒng)硬件電路的實(shí)現(xiàn)

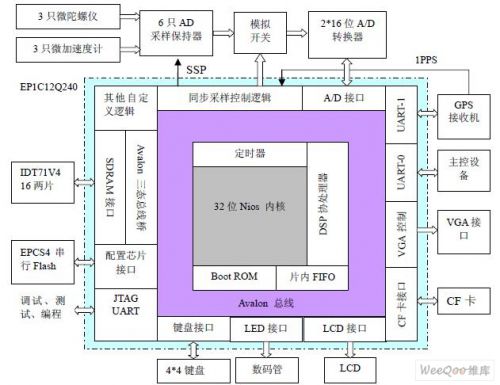

硬件框圖如圖1所示,它主要包括以Nios處理器為主體的片內(nèi)邏輯(圖中虛線包圍部分,下文簡(jiǎn)稱片內(nèi)邏輯)、MIMU與GPS數(shù)據(jù)采集電路和人機(jī)交互接口電路三個(gè)部分組成。

1.1片內(nèi)邏輯的設(shè)計(jì)

本文采用了Altera公司Cyclone系列FPGA EP1C12Q240、NIOS軟核處理器及其開發(fā)和仿真工具(包括 SOPC Builder,DSP Builder,Simulink,Quatus II等)。在設(shè)計(jì)中利用的IP核里,比如Nios核,片內(nèi)Boot ROM,用于FIFO的片內(nèi)雙口RAM,定時(shí)器,Avalon片上總線,Avalon三態(tài)總線橋,SDRAM接口,JTAG UART等都來自SOPC Builder軟件,在此不必贅述。下面重點(diǎn)討論其他IP核及其接口電路的設(shè)計(jì)和功用。

圖 1 基于Nios的SOPC組合導(dǎo)航系統(tǒng)設(shè)計(jì)框圖

6 DSP協(xié)處理器 通過定制一些傳統(tǒng)的DSP運(yùn)算指令或反復(fù)出現(xiàn)的計(jì)算密集型算法指令,來硬件加速CPU的處理能力。IP核可以通過硬件描述語(yǔ)言自己編寫,也可以借助Simulink和DSP Builder來輔助實(shí)現(xiàn)。

7 UART 基于RS232通信協(xié)議的串行通路接口。UART-0負(fù)責(zé)傳遞主控設(shè)備的命令(如復(fù)位、初始化等)、輸入主控設(shè)備提供的電子地圖的庫(kù)信息,輸出處理結(jié)果等。UART-1則負(fù)責(zé)導(dǎo)入GPS OEM板的數(shù)據(jù)。該IP核來自于SOPC Builder軟件。

8 A/D接口 除了片選信號(hào),A/D接口時(shí)序基本遵循SPI協(xié)議,因此選用了SOPC中相應(yīng)的IP, 而對(duì)于片選信號(hào),在系統(tǒng)中額外添加一個(gè)通用I/O口來控制之。這樣每次對(duì)A/D的操作分兩步進(jìn)行:先置低GPIO,再進(jìn)行SPI操作。

9 同步采樣控制邏輯 負(fù)責(zé)控制MIMU和GPS信號(hào)的同步采集,為數(shù)據(jù)融合提供準(zhǔn)確的輸入。該IP核由設(shè)計(jì)者自行編制,詳述請(qǐng)見MIMU和GPS信號(hào)采集系統(tǒng)的設(shè)計(jì)部分。

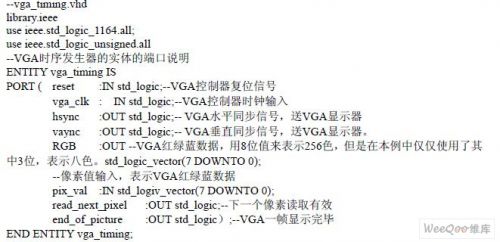

10 VGA控制 基于Avalon流模式的VGA控制器。它主要由VGA時(shí)序發(fā)生器,F(xiàn)IFO存儲(chǔ)器,Avalon流模式接口組成。該IP由設(shè)計(jì)者用VHDL語(yǔ)言自行編制,人機(jī)接口部分將詳述之。

11 ATA橋 連接CF卡,保存電子地圖信息庫(kù)、中英文字符點(diǎn)陣庫(kù)等海量信息。該IP核來自于SOPC Builder軟件。

12 GPIO 最常規(guī)的外設(shè)控制接口,本系統(tǒng)的LCD、LED、鍵盤都是采用該接口進(jìn)行連接,時(shí)序上的驅(qū)動(dòng)控制則是由軟件實(shí)現(xiàn)的。該IP核來自于SOPC Builder軟件。

13 ASMI EPCS4系列配置芯片的專門接口。該IP核來自于SOPC Builder軟件。與之相連的Flash存貯空間中有如下內(nèi)容:一部分是FPGA的配置文件。另一部分作為常規(guī)程序存儲(chǔ)器用。采用此方案可以省去片外專門的程序存儲(chǔ)Flash,充分利用了配置芯片的資源。由于串行器件的帶寬限制,我們可以通過將主程序裝載入SDRAM中運(yùn)行來提高程序的運(yùn)行速度。

1.2 MIMU和GPS信號(hào)采集系統(tǒng)的設(shè)計(jì)

MIMU的信號(hào)采集工作由微型慣性測(cè)量組合、采樣/保持器AD1154、多路開關(guān)MAX4540、A/D 轉(zhuǎn)換器完成;而GPS的信號(hào)采集工作則主要由GPS接收機(jī)完成。接收機(jī)采用了Jupiter OEM 板,可輸出位置、速度、偽距、偽距率、載波相位、衛(wèi)星星歷等數(shù)據(jù)。系統(tǒng)啟動(dòng)期間,主控設(shè)備通過UART-0向片上邏輯發(fā)送命令并獲取信息反饋,對(duì)系統(tǒng)導(dǎo)航參數(shù)進(jìn)行初始化;接收的初始化數(shù)據(jù)可由片上邏輯的UART-1傳遞給GPS接收機(jī),以實(shí)現(xiàn)GPS的快速初始化和快速鎖定衛(wèi)星.

我們所討論的MIMU和GPS信號(hào)的同步,是指需要同步的兩個(gè)數(shù)據(jù)源在原始信息更新時(shí)刻對(duì)齊,而不是在經(jīng)過計(jì)算或A/D轉(zhuǎn)換延時(shí)等不同通信路徑傳輸后,在輸出結(jié)果的時(shí)刻對(duì)齊。GPS接收機(jī)解碼轉(zhuǎn)換后輸出的秒同步脈沖(1PPS,每秒一個(gè)脈沖)是與UTC秒點(diǎn)對(duì)齊的。接收機(jī)嚴(yán)格地在每個(gè)1PPS脈沖邊沿進(jìn)行一次偽距、偽距變化率、載波相位、GPS 標(biāo)準(zhǔn)授時(shí)、定位等測(cè)量,其脈沖沿為GPS數(shù)據(jù)更新時(shí)刻。我們把1PPS脈沖接入FPGA中,由同步采樣控制邏輯保證脈沖到來的同時(shí)產(chǎn)生一個(gè)SSP(同步采樣脈沖,synchronous sampling pulse),實(shí)現(xiàn)MIMU和GPS數(shù)據(jù)在整秒時(shí)刻同步。當(dāng)然,MIMU數(shù)據(jù)更新率遠(yuǎn)小于1秒,我們可以把1PPS脈沖作為FPGA內(nèi)部的1秒定時(shí)器的標(biāo)準(zhǔn)同步觸發(fā)時(shí)刻,通過邏輯倍頻產(chǎn)生相應(yīng)頻率的SSP輸出。在GPS信號(hào)丟失的情況下,F(xiàn)PGA內(nèi)部的秒定時(shí)器則作為MIMU采樣信號(hào)的時(shí)基標(biāo)準(zhǔn)。

1.3人機(jī)交互接口的設(shè)計(jì)

七段數(shù)碼管負(fù)責(zé)標(biāo)識(shí)系統(tǒng)的工作狀態(tài);而鍵盤除了作為初始化參數(shù)輸入的備用接口外,還可以負(fù)責(zé)切換LCD、VGA顯示器等的顯示模式;液晶屏則相應(yīng)地顯示輸入與輸出的導(dǎo)航參數(shù);VGA接口形象的輸出電子地圖背景、車輛當(dāng)前位置及運(yùn)行軌跡等信息。

excalibur.h 頭文件定義了七段數(shù)碼管、按鍵數(shù)據(jù)結(jié)構(gòu)指針na_seven_seg_pio 和na_button_pio通過對(duì)指針?biāo)窹IO數(shù)據(jù)結(jié)構(gòu)內(nèi)的np_piodata數(shù)據(jù)寄存器操作,來讓數(shù)碼管顯示特定的字符或判斷是否有按鍵按下,以及是哪個(gè)按鍵。

本文采用型號(hào)Optrex 16027的LCD屏,頭文件pio_lcd16027.h定義了九個(gè)控制子程序,通過這些程序完成對(duì)LCD的控制。標(biāo)準(zhǔn)VGA畫面大小是640*480,每秒60幀左右。像素時(shí)鐘高達(dá)25.175MHZ。如果每個(gè)點(diǎn)都由Nios軟件掃描實(shí)現(xiàn),那么在40ns的間隔內(nèi),最多能讓共作在50MHZ的CPU執(zhí)行兩條指令。所以,我們采用DMA控制器在流模式VGA控制器和SRAM之間建立一條DMA傳送通道,讓硬件完成像素信息的自動(dòng)讀取,緩解了CPU的工作壓力。VGA時(shí)序發(fā)生器的設(shè)計(jì)源程序由VHDL語(yǔ)言實(shí)現(xiàn),下面是部分示意代碼:

2.系統(tǒng)工作原理

系統(tǒng)上電后,串行配置器件EPCS4配置FPGA;然后NIIOS啟動(dòng),運(yùn)行片內(nèi)ROM中的Bootloader。Bootloader根據(jù)選擇端的控制選擇工作模式,模式分為兩種:調(diào)試模式和運(yùn)行模式。在調(diào)試模式下,Bootloader啟動(dòng)GERMS監(jiān)控程序,我們可以對(duì)系統(tǒng)進(jìn)行開發(fā)調(diào)試。在運(yùn)行模式下,Bootloader將EPCS4中存儲(chǔ)的主程序裝載到SRAM中全速運(yùn)行。然后,程序指針復(fù)位指向SRAM中的系統(tǒng)主程序。主程序先初始化并配置系統(tǒng),然后開始正常工作。

3.軟件設(shè)計(jì)

由于本控制系統(tǒng)架構(gòu)龐大,我們?cè)谲浖O(shè)計(jì)時(shí)使用實(shí)時(shí)操作系統(tǒng)microC/OS作為軟件內(nèi)核。該操作系統(tǒng)具有內(nèi)核小,代碼公開等優(yōu)點(diǎn),而且Altera公司提供了關(guān)于此系統(tǒng)移植方面比較詳細(xì)的技術(shù)文檔,操作起來簡(jiǎn)單易行。系統(tǒng)軟件分為三個(gè)層次設(shè)計(jì):一、驅(qū)動(dòng)層。主要包括了UART驅(qū)動(dòng),LED驅(qū)動(dòng),鍵盤驅(qū)動(dòng),LCD驅(qū)動(dòng),VGA驅(qū)動(dòng),SPI總線設(shè)備驅(qū)動(dòng)等等。二、內(nèi)核層。包括系統(tǒng)任務(wù)和內(nèi)核調(diào)度。三、應(yīng)用層。

任務(wù)主要有數(shù)據(jù)采集任務(wù),數(shù)據(jù)融合任務(wù),數(shù)據(jù)濾波任務(wù),導(dǎo)航計(jì)算任務(wù),顯示任務(wù)等。其中還有一些用于控制管理性質(zhì)的任務(wù),包括錯(cuò)誤捕捉任務(wù)及其相應(yīng)的處理方程序等。

系統(tǒng)的核心是操作系統(tǒng)的內(nèi)核調(diào)度,負(fù)責(zé)整個(gè)軟件的運(yùn)作。系統(tǒng)相關(guān)的層面是以任務(wù)為單位的系統(tǒng)模塊,這些任務(wù)模塊負(fù)責(zé)市實(shí)現(xiàn)導(dǎo)航系統(tǒng)的正常運(yùn)行,負(fù)責(zé)系統(tǒng)模塊的配置控制和差錯(cuò)檢測(cè),響應(yīng)處理用戶的操作。硬件相關(guān)的層面以驅(qū)動(dòng)任務(wù)為單位,它們作為操作系統(tǒng)和硬件系統(tǒng)中介,直接負(fù)責(zé)對(duì)硬件設(shè)備的驅(qū)動(dòng)控制。軟件分層封裝,用任務(wù)調(diào)度的方法來實(shí)現(xiàn),可以提高軟件設(shè)計(jì)的效率,降低設(shè)計(jì)風(fēng)險(xiǎn),利于移植和升級(jí)。

4.結(jié)論

NIOS符合工業(yè)技術(shù)的潮流,即硬件設(shè)計(jì)軟件化。此設(shè)計(jì)方法可以對(duì)硬件做全面細(xì)致的模擬仿真,減少硬件設(shè)計(jì)的錯(cuò)誤,有效降低了開發(fā)成本,增強(qiáng)了產(chǎn)品的競(jìng)爭(zhēng)力。而且由于它屬于單片解決方案,不僅提高系統(tǒng)的魯棒性,還可以有效地保護(hù)開發(fā)者的知識(shí)產(chǎn)權(quán)。