摘要:基于FPGA的三相函數(shù)信號(hào)發(fā)生器以DDS為核心,在Altera公司CycloneⅡ系列EP2C8T144C8上實(shí)現(xiàn)正弦波、方波、三角波和鋸齒波信號(hào)的產(chǎn)生,利用單片機(jī)PICl8F4550控制波形的頻率及相位差。同時(shí)單片機(jī)通過(guò)DAC0832控制波形數(shù)據(jù)轉(zhuǎn)換DAC902參考電壓實(shí)現(xiàn)在波形幅度的控制,D/A輸出的波形經(jīng)過(guò)放大、濾波后輸出。波形參數(shù)的輸入輸出通過(guò)觸摸屏和液晶屏實(shí)現(xiàn),測(cè)試結(jié)果顯示該系統(tǒng)具有較高的精度和穩(wěn)定性。

模擬函數(shù)信號(hào)發(fā)生器輸出波形易受輸入波形的影響,難以實(shí)現(xiàn)移相控制,移相角度隨所接負(fù)載和時(shí)間等因素的影響而產(chǎn)生漂移,頻率、幅度的調(diào)節(jié)均依賴電位器實(shí)現(xiàn),因此精度難以保證,也很難達(dá)到滿意的效果。基于FPGA的數(shù)字式三相信號(hào)發(fā)生器,精度較高,移相控制方便,實(shí)現(xiàn)頻率為1 Hz~10 MHz、幅度0.1~10 V,分辨率為1°,頻率和幅度的調(diào)節(jié)均可程控的三相函數(shù)信號(hào)發(fā)生器。系統(tǒng)還具有輸出靈活、易于系統(tǒng)升級(jí)等優(yōu)點(diǎn)。

1 函數(shù)信號(hào)發(fā)生器的原理

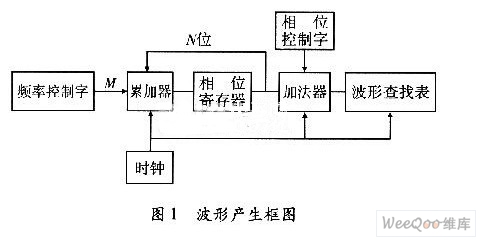

基于DDS原理,頻率控制字M和相位控制字P分別控制DDS輸出波形的頻率和相位。相位累加器是整個(gè)波形產(chǎn)生的核心,它有一個(gè)累加器和一個(gè)N位相位寄存器組成。每來(lái)一個(gè)時(shí)鐘脈沖,相位寄存器以步長(zhǎng)M增加,如圖1所示。相位寄存器的輸出與相位控制字相加,其結(jié)果作為波形查找表的地址。波形查找表由ROM構(gòu)成,內(nèi)部存有一個(gè)完整周期的波形的數(shù)字幅度信息,每個(gè)查找的地址對(duì)應(yīng)波形中0°~360°范圍的一個(gè)相位點(diǎn)。查找表輸入的地址信息映射達(dá)成波形幅度信號(hào),同時(shí)輸出到數(shù)模轉(zhuǎn)換器的輸入段,DAC輸出的模擬信號(hào)經(jīng)過(guò)程控濾波器,可得到一個(gè)頻譜純凈的波形。

相位寄存器每經(jīng)過(guò)2N/M個(gè)fc時(shí)鐘周期后回到初始裝狀態(tài),相應(yīng)地波形查表經(jīng)過(guò)一個(gè)循環(huán)回到初始位置,DDS輸出一個(gè)波形。輸出的波形周期為Tout=(2N/M)Tc,頻率為

DDS的最小分辨率為fmin=fc/2N,當(dāng)M=2N-l(即一個(gè)周期內(nèi)只取兩個(gè)點(diǎn))時(shí),DDS最高的基波合成頻率為foutmax=fc/2,根據(jù)取樣定理,這在理論上是可行的,考慮到失真度的問(wèn)題,取i(i>2)個(gè)點(diǎn),則最高頻率為當(dāng)M=2N-3時(shí),foutmax=fc/i。

2 系統(tǒng)總體設(shè)計(jì)

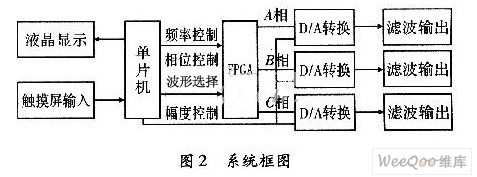

系統(tǒng)由單片機(jī)控制模塊、FPGA波形產(chǎn)生模塊、數(shù)模轉(zhuǎn)換模塊、濾波輸出模塊、觸摸屏輸入和液晶顯示模塊組成,單片機(jī)控制FPGA產(chǎn)生輸入頻率和相位差的三相正弦波、方波、三角波和鋸齒波,經(jīng)過(guò)D/A轉(zhuǎn)換后濾波輸出,三相波形的幅度也由單片機(jī)通過(guò)改變D/A的參考電壓控制。具體系統(tǒng)框圖,如圖2所示。

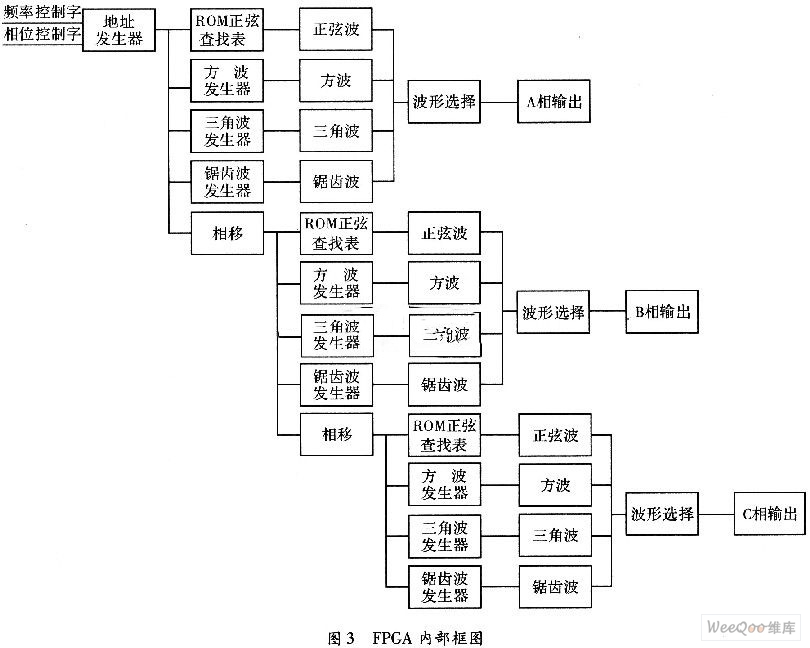

FPGA部分具體框圖,如圖3所示,基于DDS原理,主要由相位累加器、正弦波ROM查找表、方波發(fā)生器、三角波發(fā)生器、鋸齒波發(fā)生器和波形選擇模塊組成。根據(jù)單片機(jī)設(shè)置相移值調(diào)整三相波形的相位差,波形選擇也由單片機(jī)控制。

2.1 分頻模塊設(shè)計(jì)

為了對(duì)波形頻率精確控制,不同頻率段需要不同的輸入頻率。項(xiàng)目設(shè)計(jì)中采用50 MHz外部有源晶振,利用FPGA內(nèi)部鎖相環(huán)將頻率鎖定在40.96 MHz,然后該頻率進(jìn)行10 MHz,100 MHz,1 000 MHz,10 000 MHz,如圖4所示,這樣就得到了5個(gè)不同的頻率區(qū)間,最后通過(guò)5選1數(shù)據(jù)選擇器由單片機(jī)選擇所需要的時(shí)鐘頻率。時(shí)鐘頻率與輸出波形頻率之間具體關(guān)系,如表l所示。

2.2 波形產(chǎn)生模塊設(shè)計(jì)

2.2.1 正弦波

正弦波的數(shù)據(jù)需要轉(zhuǎn)換為*.mif文件后存放到ROM中,mif文件有固定格式規(guī)定了每個(gè)字的位寬WIDTH、總字?jǐn)?shù)DEPTH、地址進(jìn)制基數(shù)ADDR-ESS_RADIX和數(shù)據(jù)進(jìn)制基數(shù)DATA_RADIX。在Matlab環(huán)境中編程計(jì)算出正弦波數(shù)據(jù),然后生成mif文件。

EP2C8T144C8擁有較充裕的存儲(chǔ)空間。因此,設(shè)計(jì)中為了提高精度在ROM中存放4 096個(gè)正弦數(shù)據(jù),頻率控制字、相位控制字由單片機(jī)控制產(chǎn)生,經(jīng)過(guò)相位累加器組成地址發(fā)生器,產(chǎn)生的地址連到ROM的地址線上進(jìn)行查表得到波形數(shù)據(jù)。

2.2.2 方波

方波算法比較容易實(shí)現(xiàn)。由于其只有高低電平兩種狀態(tài)。因此,只需要在一個(gè)周期的時(shí)間中間位置翻轉(zhuǎn)電平即可。由于相位累加器的值是線形累加的,地址address的值也是線形累加的,對(duì)所給地址值address進(jìn)行判斷,當(dāng)?shù)刂分档淖罡呶粸镺時(shí),便將波形幅值各字位賦值1,否則賦值0。就可以實(shí)現(xiàn)最簡(jiǎn)單的占空比50%的方波。

為了實(shí)現(xiàn)占空比可調(diào),設(shè)計(jì)中增加一個(gè)變量PWM_zkb[11..0],讓地址值與WM_zkb[11..O]比較,Adress[11..0]

2.2.3 三角波

三角波的生成原理與方波生成原理相似,也是對(duì)地址Address的值進(jìn)行判斷,當(dāng)其最高位為0時(shí),取其O~ll位為三角波的波形幅值,即令Data_out[11..0]=Address[11..0]。當(dāng)其最高位為l時(shí),對(duì)其0~1l位的值取反后再作為三角波的波形幅值,即令Data_out[11..0]=not(Address[11..0])。

2.2.4 鋸齒波

鋸齒波的產(chǎn)生也是基于上述原理,是對(duì)地址Address的值進(jìn)行判斷,當(dāng)其最高位為O時(shí),取其0~ll位為三角波的波形幅值,即令。Data_ out[11..0]=Address[11..0]。當(dāng)其最高位為1時(shí),對(duì)其最高位的值取反后作為鋸齒波的波形幅值,即令Data_out,[11..0]=Address[11..0]and“011111111111”。

2.3 相移的實(shí)現(xiàn)

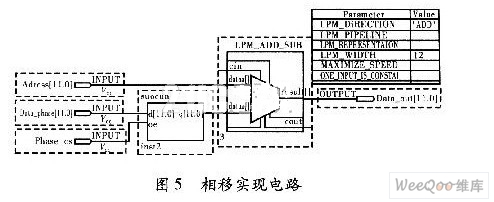

在A相地址的基礎(chǔ)上,增加一個(gè)累加器,輸入段分別是A相地址和偏移值,經(jīng)過(guò)累加之后得到B相波形地址,然后根據(jù)此地址對(duì)ROM尋址或者在地址的基礎(chǔ)上生成方波、三角波和鋸齒波。如圖5所示,A相、B相及B相、C相之間的偏移量有單片機(jī)控制,數(shù)據(jù)經(jīng)過(guò)鎖存后送入累加器。

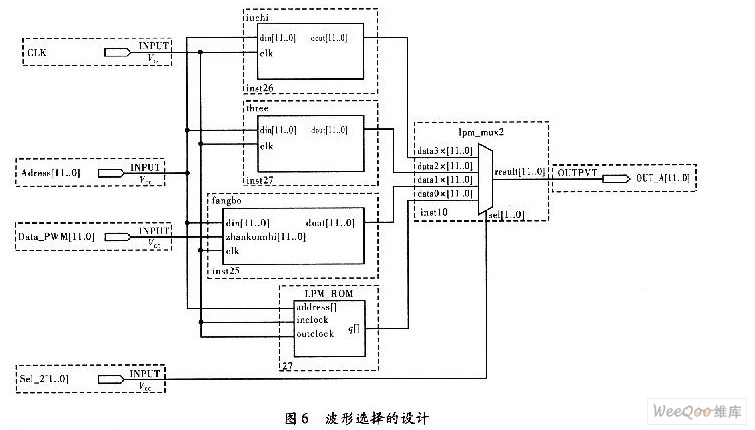

2.4 波形選擇的實(shí)現(xiàn)

根據(jù)設(shè)計(jì)要求,每一相都可以實(shí)現(xiàn)正弦波、方波、三角波和鋸齒波任意一種波形的輸出,設(shè)計(jì)了一個(gè)4選1數(shù)據(jù)選擇器,控制端Sel[1.-.0]與單片機(jī)IO口相連,如圖6所示,以A相為例。

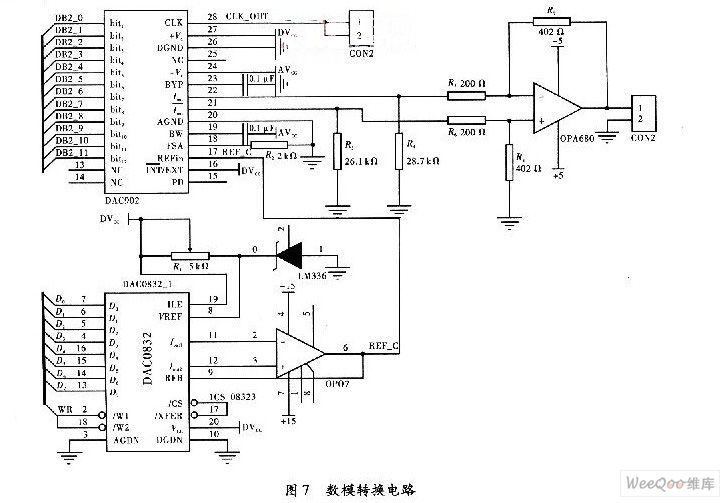

2.5 幅度控制的實(shí)現(xiàn)

參考電壓可通過(guò)INT/EXT端選擇內(nèi)部和外部。當(dāng)該端口為高電平時(shí)選擇外部參考電壓,只要改變參考電壓,就可以改變輸出波形的幅值。DAC902外部參考電壓范圍0.10~1.25 V,因此只需采用8位D/A既可實(shí)現(xiàn)0.01 V的步進(jìn)。如圖7所示,DAC0832輸出接到DAC902參考電壓輸入端REFin,通過(guò)單片機(jī)控制DAC0832輸出,進(jìn)而控制DAC902參考電壓。

3 系統(tǒng)測(cè)試

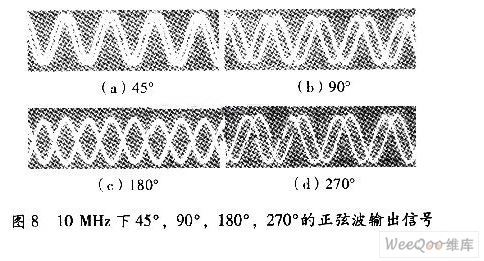

本系統(tǒng)波形參數(shù)設(shè)置通過(guò)觸摸屏輸入完成,用示波器測(cè)試50 Ω負(fù)載下的輸出波形,比較設(shè)置值與測(cè)試值之間的誤差,圖8為信號(hào)源輸出頻率為10 MHz,峰峰值為5 V,兩路信號(hào)相移分別為45°、90°、180°、270°時(shí),在使用Fluck PM3394B 200 MHz Combiscope Instrument的“Analog”模式下,用數(shù)碼相機(jī)拍攝的正弦波的輸出波形。

經(jīng)過(guò)多次測(cè)試和反復(fù)改進(jìn),最終實(shí)現(xiàn)了如下技術(shù)指標(biāo):

(1)輸出波形:正弦波、方波、三角波、鋸齒波。

(2)輸出波形頻率范圍:0.1 Hz~10 MHz。

(3)輸出頻率調(diào)節(jié)步長(zhǎng):0.01 Hz~10 kHz。

(4)輸出電壓范圍:10 mV~10 V(峰峰值)可調(diào),幅度步進(jìn)最小10 mV。

(5)方波占空比調(diào)節(jié)范圍:1%~99%。

由于示波器只有兩個(gè)通道,因此只能測(cè)量?jī)身?xiàng)信號(hào)之間的相位差。

在頻率穩(wěn)定度方面,正弦波、三角波、方波和矩形波輸出波形穩(wěn)定,這正是體現(xiàn)了DDS技術(shù)的特點(diǎn),輸出頻率穩(wěn)定度和晶振穩(wěn)定度在同一數(shù)量級(jí)。由于采用了FPGA的內(nèi)部時(shí)鐘,在倍頻分頻的結(jié)果后還是無(wú)法達(dá)到計(jì)算的時(shí)鐘,因此存在著誤差,但在頻率較高部分誤差稍明顯,因此設(shè)計(jì)中采用了軟件修正,從而減少了頻率較高部分的誤差。

對(duì)于波形幅度的控制上,由于波形在電路網(wǎng)絡(luò)存在一定的衰減,因此在程序中采用軟件補(bǔ)償進(jìn)行修正。從測(cè)試結(jié)果可以看書軟件補(bǔ)償做得越細(xì)致誤差越小。

4 結(jié)束語(yǔ)

本項(xiàng)目以多功能、低功耗、操作方便、結(jié)構(gòu)合理、易于調(diào)試為主要設(shè)計(jì)原則,在系統(tǒng)設(shè)計(jì)過(guò)程中,力求硬件線路簡(jiǎn)單,充分發(fā)揮軟件編程方便靈活的特點(diǎn),并最大限度挖掘FPGA片內(nèi)資源,來(lái)滿足系統(tǒng)設(shè)計(jì)要求。

利用硬件描述語(yǔ)言VHDL編程,借助Ahera公司的Quartus II軟件環(huán)境下進(jìn)行了編譯及仿真測(cè)試,在FPGA芯片上設(shè)計(jì)了函數(shù)發(fā)生器,產(chǎn)生正弦波、三角波、方波等多種波形,系統(tǒng)的頻率分辨率高,頻率切換速度比較快。設(shè)計(jì)采用了EDA技術(shù),縮短了開發(fā)研制周期,提高了設(shè)計(jì)效率,而且使系統(tǒng)具有結(jié)構(gòu)緊湊、設(shè)計(jì)靈活、實(shí)現(xiàn)簡(jiǎn)單、性能穩(wěn)定的特點(diǎn)。