數(shù)字視頻產(chǎn)品需求近些年出現(xiàn)猛增,。主流應(yīng)用包括視頻通信,、視頻監(jiān)控與工業(yè)自動化,而最熱門的要算娛樂應(yīng)用,,如 DVD,、HDTV、衛(wèi)星電視,、標(biāo)清(SD)或高清 (HD) 機(jī)頂盒,、數(shù)碼相機(jī)與 HD 攝像機(jī)、高端顯示器(LCD,、等離子顯示器,、DLP)以及個(gè)人攝像機(jī)等。這些應(yīng)用都向高質(zhì)量的視頻編解碼算法及其標(biāo)準(zhǔn)提出巨大需求,,目前主流壓縮標(biāo)準(zhǔn)主要有MPEG2,、MPEG4和H.264/AVC,而針對這些編解碼標(biāo)準(zhǔn)有各種各樣的實(shí)現(xiàn)方案,。本文主要探討基于TI 的C64系列DSP的視頻解碼算法標(biāo)準(zhǔn)系統(tǒng)優(yōu)化過程中需要考慮的若干因素,。

TI的C64系列DSP以其強(qiáng)大的處理能力被廣泛用于視頻處理領(lǐng)域,,然而由于大家對C64系列DSP的結(jié)構(gòu)、指令,、的理解程度不一樣,,造成算法實(shí)現(xiàn)時(shí)的效果有許多的差異。具體體現(xiàn)在實(shí)現(xiàn)算法時(shí)所使用的CPU的資源上,。如實(shí)現(xiàn)H.264 MP@D1解碼時(shí)所占用CPU的資源上,,會有所差異,或者是所包含的算法工具子集上,,如實(shí)現(xiàn)H.264 MP@D1解碼時(shí)使用CAVLC而不使用CABAC,。造成這些差異,主要原因有如下因素:

算法關(guān)鍵模塊的優(yōu)化

算法系統(tǒng)集成時(shí)Memory的管理

算法系統(tǒng)集成時(shí)的EDMA的資源分配管理

本文從這三方面逐步探討算法優(yōu)化集成中需要考慮的若干因素,。

算法關(guān)鍵模塊的優(yōu)化

一般而言,,對于目前主流視頻解壓縮標(biāo)準(zhǔn)都有類似的很消耗DSP CPU的模塊,如H.264/AVC,、MPEG4,、AVS等編碼中運(yùn)動矢量搜索很占用資源,而且這些模塊在整個(gè)系統(tǒng)實(shí)現(xiàn)過程中調(diào)用相當(dāng)頻繁,,因此我們首先找出這些模塊,,這點(diǎn)TI的CCS提供了工程剖析工具(Profile),可以很快找到整個(gè)工程中占用DSP CPU資源最多的模塊,;然后對這些模塊進(jìn)行優(yōu)化,。

對這些關(guān)鍵算法模塊的優(yōu)化我們分可以分三步進(jìn)行,如圖2所示,,先認(rèn)真分析這部分代碼,,并進(jìn)行相應(yīng)的調(diào)整,如盡量減少有判斷跳轉(zhuǎn)的代碼,,特別是for循環(huán)中,,判斷跳轉(zhuǎn)會打斷軟件流水。使用的方法,,可是使用查表或者使用_cmpgtu4,、_cmpeq4等Intrinsics來代替比較判斷指令,從而巧妙替代判斷跳轉(zhuǎn)語句,。同時(shí)使用TI的CCS中所提供的#pragma提供編譯器盡量多的信息,,這些信息包括for循環(huán)的次數(shù)信息、數(shù)據(jù)對齊信息等,。如果經(jīng)過這部分優(yōu)化無法滿足系統(tǒng)要求,,則對這部分模塊使用線性匯編實(shí)現(xiàn),線性匯編是介于C和匯編之間的一種語言實(shí)現(xiàn)形式,,可以控制指令的使用,,而不必特別關(guān)心寄存器,、功能單元(S、D,、M,、L)的分配和使用,,使用線性匯編一般會比使用C語言具有更高的執(zhí)行效率,。如果線性匯編還無法滿足要求,則使用匯編實(shí)現(xiàn),,要編寫出高并行,、深軟件流水的匯編需要經(jīng)過畫相關(guān)圖,創(chuàng)建時(shí)序表(Scheduling table)等步驟,,由于篇幅所限,,這里就不熬述。

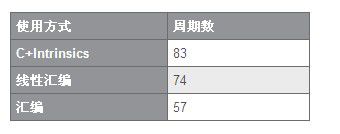

表1

優(yōu)化選項(xiàng):-pm, -o3,,基于C64plus內(nèi)核,,C+Instrinsics 是指在C中使用Instrinsics。

表1是運(yùn)動搜索中所需要的計(jì)算16×16宏塊SAD值時(shí),,不同方式下所消耗的DSP CPU的周期數(shù),。由此可見,匯編實(shí)現(xiàn)所消耗的CPU的周期數(shù)最少,,但前提是需要充分了解DSP CPU的結(jié)構(gòu),、指令以及算法模塊的結(jié)構(gòu),從而能夠編寫出高并行,、深軟件流水的匯編,,否則有可能所寫出的匯編還沒有線性匯編或者C效率更高。為此一個(gè)行之有效的方法是,,充分利用TI所提供的算法庫中的函數(shù),,因?yàn)樗惴◣熘械暮瘮?shù)都是已經(jīng)充分優(yōu)化過的算法模塊,而且大都提供對對應(yīng)的C,、線性匯編和匯編源代碼,,并有文檔進(jìn)行API介紹。

算法系統(tǒng)集成時(shí)Memory的管理

由于在基于DSP的嵌入式系統(tǒng)開發(fā)中,,存儲資源特別是片內(nèi)高速存儲資源有限,,在算法系統(tǒng)集成時(shí)Memory的管理對于提高整個(gè)系統(tǒng)的優(yōu)化是非常重要的,這一方面影響數(shù)據(jù)的讀取,、搬移速度,;另一方面還影響Cache的命中率,下面分程序和數(shù)據(jù)兩方面分析,。

程序區(qū):最大原則是將經(jīng)常調(diào)度使用的算法模塊放片內(nèi),。為做到這點(diǎn),,TI的CCS中提供了#pragma CODE_SECTION,可以把需要單獨(dú)控制存放的函數(shù)段從.text段中獨(dú)立出來,,從而在.cmd文件中對這些函數(shù)段進(jìn)行單獨(dú)物理地址映射,。還可以使用程序動態(tài)的方式,將需要運(yùn)行的代碼段先調(diào)度進(jìn)片內(nèi)memory,,如H.264/AVC中CAVLC和CABAC兩個(gè)算法模塊具有互斥性,,因此可以將這兩個(gè)算法模塊放在片外而且對應(yīng)于片內(nèi)同一塊運(yùn)行區(qū),在運(yùn)行其中某一個(gè)算法模塊之前,,先將其調(diào)入片內(nèi),,從而充分利用片內(nèi)有限的高速存儲區(qū)。程序區(qū)的管理考慮到一級程序Cache(L1 P)的命中率,,最好將具有先后執(zhí)行順序的函數(shù)按地址先后順序配置在

程序空間中,,同時(shí)對代碼比較大的處理函數(shù)將其拆分成小函數(shù)。

數(shù)據(jù)區(qū):在視頻標(biāo)準(zhǔn)編解碼中,,由于數(shù)據(jù)塊都很大,,如一幀D1 4:2:0的圖像有622k大小,而且在編解碼中都需要開3~5幀甚至更多的緩沖幀,,因此數(shù)據(jù)基本上無法在片內(nèi)存放,。為此在系統(tǒng)的Memory優(yōu)化管理中,需要開C64系列DSP的二級Cache(對于TMS320DM642用于視頻編解碼中二級Cache開64k的情況比較多),。同時(shí)最好將放片外的被Cache所映射的視頻緩沖區(qū)的數(shù)據(jù)以128 byte對齊,,這是因?yàn)镃64系列的DSP的二級Cache的每行大小為128 byte,以128 byte對齊有利于Cache的刷新和一致性維護(hù),。

算法系統(tǒng)集成時(shí)的EDMA的資源分配管理

由于在視頻處理中,,會經(jīng)常有塊數(shù)據(jù)的搬移,而且C64系列DSP提供了EDMA,,邏輯上有64個(gè)通道,,因此對EDMA的配置使用對優(yōu)化系統(tǒng)是非常重要的。為此可以使用下述步驟進(jìn)行充分配置系統(tǒng)的EDMA資源,。

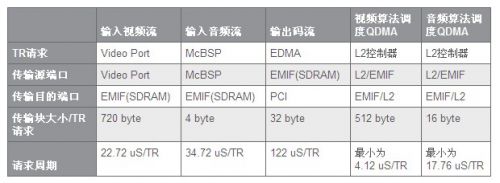

1. 統(tǒng)計(jì)系統(tǒng)中各種需要使用EDMA的情況及其大概需要占用的EDMA物理總線的時(shí)間,,如表2所示:

注意:該表針對視頻通過視頻端口(Video Port)(720*480,4:2:0,,30Frame/s),,音頻通過McBSP(采樣率為44k)進(jìn)入DSP,壓縮好的數(shù)據(jù)數(shù)率在2Mbps左右,,數(shù)據(jù)通過PCI每488uS輸出一個(gè)128byte的包(PCI口工作頻率為33MHz),,外掛SDRAM的時(shí)鐘頻率為133MHz,只做一個(gè)參考應(yīng)用例子。

2. 統(tǒng)計(jì)好這些信息后,,需要依據(jù)系統(tǒng)對各種碼流實(shí)時(shí)性,、及其傳輸數(shù)據(jù)塊大小對各個(gè)被使用的EDMA通道進(jìn)行優(yōu)先級分配。一般而言,,由于音頻流傳輸塊小,,因此占用EDMA總線的時(shí)間短,而視頻傳輸塊比較大,,占用EDMA總線的時(shí)間較長,,因此將輸入音頻所對應(yīng)的EDMA通道的優(yōu)先級設(shè)定為Q0(urgent),視頻的優(yōu)先級設(shè)定為Q2(medium),,輸出碼流所對應(yīng)的EDMA通道的優(yōu)先級設(shè)定為Q1(high),,音視頻算法處理中所調(diào)度的QDMA的優(yōu)先級設(shè)定為Q3(low)。當(dāng)然這些設(shè)定在真正系統(tǒng)應(yīng)用中可能還需要調(diào)整的,。

實(shí)際的基于TI DSP視頻算法優(yōu)化集成過程,會是基于圖1所示的步驟,,先初步配置Memory,,并選擇相應(yīng)編譯優(yōu)化選項(xiàng),如果編譯的結(jié)果已經(jīng)可以達(dá)到實(shí)時(shí)性要求之后就結(jié)束后面的優(yōu)化,;否則開始優(yōu)化Memory和EDMA的配置,,從而提高對Cache和內(nèi)部總線的利用率;如果還無法達(dá)到要求則通過剖析整個(gè)工程確定消耗CPU資源最高的代碼段或者函數(shù),,對這些關(guān)鍵模塊進(jìn)行優(yōu)化,,采用線性匯編、甚至匯編直到整個(gè)系統(tǒng)可以滿足要求為止,。

參考文獻(xiàn):

TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide (SPRU732)

TMS320C6000 EDMA IO Scheduling and Performance (SPRAA00)

TMS320C6000 Optimizing Compiler User's Guide (spru187)

TMS320C64x EDMA Architecture (SPRA994)

TMS320C6000 EDMA Controller Reference Guide (SPRU234)

TMS320C64x DSP Two-Level Internal Memory Reference Guide (SPRU610)

Cache Usage in High-Performance DSP Applications With the TMS320C64x (SPRA756)