介紹一種利用帶通采樣定理及多相濾波的方式實現(xiàn)數(shù)字相干檢波的方法,,由于采用數(shù)字信號處理的方式獲取I,、Q基帶信號,因此具有鏡頻抑制能力強,、線性動態(tài)范圍大,、系統(tǒng)設(shè)備簡單、一致性好等優(yōu)點,。文章主要從理論及工程實現(xiàn)兩個方面展開論述,。

1 基本原理

設(shè)某一數(shù)字濾波器的脈沖響應(yīng)為h(n),則其Z變換H(z)定義為

對式(1)展開變換后,,可得

令 則

則

式(2)即為數(shù)字濾波器H(z)多相濾波結(jié)構(gòu),,顯然H(z)由D個EK(z),K=0,,1,,2,…,,D-1分支濾波器構(gòu)成,,并且每個濾波器的階數(shù)為H(z)階數(shù)的1/D,這種多相濾波的結(jié)構(gòu)不僅能夠提高系統(tǒng)實時處理能力,,而且可以降低傳統(tǒng)濾波器濾波運算后的累計誤差,。下面對多相濾波技術(shù)在數(shù)字相干檢波中的應(yīng)用進行理論分析。

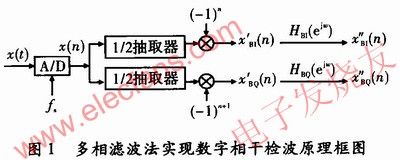

通常,,對于載頻為fo的帶限(帶寬B)中頻信號,,若以采樣率為fs=4fo/(2m+1),m=O,,1,,2,…,,且fs≥2B對其采樣,,通過符號修正及多相濾波的方式可準(zhǔn)確獲得正交的兩路基帶信號,如圖1所示,。

設(shè)信號x(t)=a(t)cos[2πfot+φ(t)],,若以采樣率為fs=4fo/(2m+1),m=0,,1,,2,…,,且fs≥2B對x(t)采樣后得到的采樣序列為

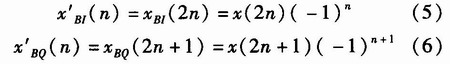

式中,,![]() 分別為信號的同向分量和正交分量,,對x(n)進行奇偶分路和符號變換,可以得到

分別為信號的同向分量和正交分量,,對x(n)進行奇偶分路和符號變換,可以得到

顯然,,![]() 和

和![]() 分別為同向分量和正交分量的2倍抽取序列,,容易證明

分別為同向分量和正交分量的2倍抽取序列,,容易證明![]() 和

和![]() 的數(shù)字譜為

的數(shù)字譜為

式(7)和式(8)描述了正交解調(diào)后同向I及正交Q支路的頻譜,但二者的數(shù)字譜相差一個延遲因子![]() ,,這相當(dāng)于在時域上相差O.5個采樣點,,需要兩個延遲濾波器校正,這兩個濾波器需要滿足

,,這相當(dāng)于在時域上相差O.5個采樣點,,需要兩個延遲濾波器校正,這兩個濾波器需要滿足![]()

![]() ,,兩路延遲濾波器需要具有相似的幅度或相位特性,,保證、支路嚴(yán)格匹配,。

,,兩路延遲濾波器需要具有相似的幅度或相位特性,,保證、支路嚴(yán)格匹配,。

理論分析知,,可以采用多相濾波的方式從一原型低通濾波器中取出數(shù)字譜相差![]() 的兩個支路分別對I、Q兩路延遲濾波,,由于兩個濾波器是從同一個原型濾波器中抽取出來的兩個分支,,因此具有相似的幅度及相位特性。

的兩個支路分別對I、Q兩路延遲濾波,,由于兩個濾波器是從同一個原型濾波器中抽取出來的兩個分支,,因此具有相似的幅度及相位特性。

設(shè)原型濾波器的沖擊響應(yīng)為h(n),,由(1)式知,,其多相結(jié)構(gòu)第K條支路的沖擊響應(yīng)為

則EK(z)頻率響應(yīng)為

令D=4,則式中除i=0項不為零外,,其余均為零,,所以求得

提取K=3及K=1作為式(7)及式(8)I、Q兩路延遲濾波,,得

由此可見,,經(jīng)過![]() 濾波,兩個正交得基帶信號

濾波,兩個正交得基帶信號![]() 在時間上完全對齊,,滿足數(shù)字正交相干檢波的要求,。

在時間上完全對齊,,滿足數(shù)字正交相干檢波的要求,。

2 仿真分析

下面采用多相濾波的方法對帶寬B=5 MHz,載頻fo=60 MHz,,信號頻率fd的帶限信號直接中頻采樣提取正交的基帶分量,,采樣頻率fs=80 MHz,依照多相濾波原理,,設(shè)計階數(shù)為N,,截止頻率為B的FIR原型低通濾波器,,并從中抽取出數(shù)字譜相差![]() 兩個支路分別對I,、Q兩路延遲濾波,測試不同頻率點的鏡頻抑制比,,仿真測試結(jié)果如表1所示,。

兩個支路分別對I,、Q兩路延遲濾波,測試不同頻率點的鏡頻抑制比,,仿真測試結(jié)果如表1所示,。

從數(shù)據(jù)中可以看出,,原型濾波器階數(shù)n越大,鏡頻抑制比IR越高,,fd越大,,鏡頻抑制比IR有下降趨勢。圖2和圖3分別表示N=32,,fd=2.3 MHz的及N=64,,fd=3 MHz的帶限信號相參處理后的功率譜分析。

對于N=32,,fd=2.3 MHz的帶限信號鏡頻抑制比IR高達106.14 dB,,可見結(jié)合帶通采樣定理及多相濾波方式實現(xiàn)對帶限信號直接中頻采樣獲取基帶信號能夠達到很高的鏡頻抑制比,這是傳統(tǒng)的模擬相干檢波難以實現(xiàn)的,。

如上文所述,,對寬B=5 MHz,載頻fo=60 MHz的線性調(diào)頻信號直接中頻采樣,,利用多項濾波的方式實現(xiàn)數(shù)字下變頻仿真輸出波形,,如圖4所示。

圖4低通濾波輸出的是B=5 MHz,,時寬T=10μs的基帶線性調(diào)頻信號,,從零點的輸出看,I,、Q兩路完全正交,。仿真分析表明,利用多項濾波的方式可實現(xiàn)對基帶視頻信號的提取,,完成數(shù)字檢波的功能,。

3 FPGA實現(xiàn)

在一款脈沖壓縮體制的雷達中頻數(shù)字化接收機工程項目中,系統(tǒng)需要實現(xiàn)對帶寬B=5 MHz,,時寬T=10μs,,載頻fS=60 MHz的線性調(diào)頻信號進行直接中頻采樣,依據(jù)帶通采樣原理,,采樣頻率選為fS=80 MHz,。硬件設(shè)計原理框,如圖5所示,。硬件設(shè)計中,,采用AD9853對微波信號源送的80 MHz的連續(xù)波轉(zhuǎn)換為TTL信號的采樣時鐘及FPGA的工作時鐘,同時分頻產(chǎn)生20 MHz時鐘信號作為DDS芯片AD9854的外部工作時鐘,,DDS產(chǎn)生60 MHz的脈沖調(diào)制的中頻信號,,A/D轉(zhuǎn)換器采用AD6645,信號和采樣時鐘同源,,具有嚴(yán)格的相位關(guān)系,,采樣后的數(shù)字下變頻采用Xilinx公司Virtex-Ⅱ系列的XC2V1000來完成,,主要包括功能模塊為數(shù)據(jù)的奇偶抽取、符號修正,、正交兩路延遲濾波,,降速抽取、低通濾波以及時序電路設(shè)計,。

FPGA設(shè)計中,,奇偶抽取電路對80 MHz的時鐘分頻為40 MHz,利用時鐘上升及下降沿分別將采樣后的I(0),、Q(1),、I(2)、Q(3)……的序列進行奇偶抽取,,對抽取的正交兩路數(shù)據(jù)分別進行符號修正,,修正的目的主要是解決采樣時符號反向的問題,符號修正電路實現(xiàn)可通過對采樣時鐘4分頻,,高電平時I,、Q兩路數(shù)據(jù)分別保持不變,低電平時,,I,、Q兩路數(shù)據(jù)求其每一位邏輯反后加1,功能上相當(dāng)于乘以-1,,修正后的兩路輸出序列分別為I(0),、I(2)、I(4),、Q(6)……及Q(1),、Q(3)、Q(5),、Q(7)……,,由上述理論分析知,兩路數(shù)據(jù)在時間上相差一個采樣點,,對于數(shù)字頻率相差![]() 個相位,,需要通過延遲濾波器來實現(xiàn)時間上對齊,延遲濾波器采用多項濾波的方式實現(xiàn),,即I,、Q兩路的濾波器的系數(shù)由同一個原型濾波器設(shè)計而成,F(xiàn)PGA中濾波器設(shè)計采用Xilinx的IP核中的FIR模塊,,延遲濾波后的數(shù)據(jù)經(jīng)4倍降速抽取,,并通過低通濾波器濾除高階分量后送外部D/A變換器,低通濾波器采用32階的FIR數(shù)字濾波器,濾波器設(shè)計同樣采用IP核實現(xiàn),,F(xiàn)PGA設(shè)計原理框,如圖6所示,。

個相位,,需要通過延遲濾波器來實現(xiàn)時間上對齊,延遲濾波器采用多項濾波的方式實現(xiàn),,即I,、Q兩路的濾波器的系數(shù)由同一個原型濾波器設(shè)計而成,F(xiàn)PGA中濾波器設(shè)計采用Xilinx的IP核中的FIR模塊,,延遲濾波后的數(shù)據(jù)經(jīng)4倍降速抽取,,并通過低通濾波器濾除高階分量后送外部D/A變換器,低通濾波器采用32階的FIR數(shù)字濾波器,濾波器設(shè)計同樣采用IP核實現(xiàn),,F(xiàn)PGA設(shè)計原理框,如圖6所示,。

4 結(jié)束語

文中討論了直接中頻采樣下,,利用多相濾波的方法實現(xiàn)數(shù)字檢波的基本原理及實現(xiàn)方法,并給出FPGA實現(xiàn)的工程樣例,。計算機仿真表明,,利用帶通采樣定理及多相濾波方式對帶限信號直接中頻采樣能夠準(zhǔn)確可靠地將一定帶寬范圍內(nèi)的基帶信息提取出來,而且相對傳統(tǒng)的模擬相干檢波能夠獲得較高的鏡頻抑制比,,利用FPGA單片資源便可實現(xiàn)單通道甚至多通道的數(shù)字相干檢波的功能,,簡化了系統(tǒng)設(shè)計,而且在技術(shù)指標(biāo)上又可有效地克服正交通道不一致的問題,,具有較高的工程應(yīng)用價值,。