引言

在電子信息領(lǐng)域,函數(shù)發(fā)生器(信號源)是通用的設(shè)備。近年來電子信息技能 的飛速發(fā)展,使得各領(lǐng)域?qū)π盘栐吹囊笤诓粩嗵岣摺2坏笃漕l率穩(wěn)定度和精確 度高,要求頻率改動 的方便性,而且還要求可以產(chǎn)生任意波形,輸出不同幅度的信號等。而實現(xiàn)頻率合成要領(lǐng) 有許多種,但基本上可以歸納為直接頻率合成和間接頻率合成兩大類要領(lǐng) 。采用傳統(tǒng)的頻率合成技能 要實現(xiàn)上述要求,幾乎是不可能的。DDFS技能 是自21世紀(jì)70年代出現(xiàn)的一種新型的直接頻率合成技能 。DDFS 技能 是在信號的采樣定理的基礎(chǔ)上提出來的,從“相位”的概念出發(fā),執(zhí)行 頻率合成,不但可運(yùn)用 晶體振蕩的高頻率穩(wěn)定度、高精確 度,且頻率改動 方便,轉(zhuǎn)換速度快,便于產(chǎn)生任意波形等,因此,DDFS技能 是目前高精密度信號源的核心技能 。目前已有專用的DDFS芯片,如美國AD公司的AD9850等可用于DDS 信號源的開發(fā),但其成本較高。

1 DDFS原理

DDFS的原理:將對正弦等各種信號的采樣量化數(shù)據(jù)存入ROM存儲器中,在時鐘的控制下,依次或隔一定步進(jìn)讀取ROM中的數(shù)據(jù),再通過D/A轉(zhuǎn)換芯片及后級的低通濾波器來實現(xiàn)頻率合成的一種要領(lǐng) 。其原理框圖如圖1所示。其主要的組成部分包括:相位累加器(也可理解為ROM存儲單元的讀地址發(fā)生單元)、正弦信號采樣量化數(shù)據(jù)存儲ROM表、D/A轉(zhuǎn)換及低通濾波器。

DDFS參數(shù)計算:DDFS的主要參數(shù)包括正弦信號的采樣點(diǎn)數(shù),最高輸出頻率fomax,最低輸出頻率fomax及頻率分辨率△fo等。根據(jù)DDFS原理可知,在時鐘控制下將所有ROM存儲數(shù)據(jù)依次讀出,則輸出的信號周期最長Tomax=NTc,即輸出頻率最低為fomax;只讀出兩個點(diǎn)(∏/2和 3∏/2)的采樣數(shù)據(jù),則輸出的信號周期最短Tomin=2Tc,即輸出頻率最高為fomax。其中Tc為時鐘周期。相應(yīng)計算如下。(1)輸出信號頻率通式:fo=Sfc/2n,其中2n為采樣點(diǎn)個數(shù)N,故可知n為采樣后ROM的地址位數(shù);其中S為步進(jìn)長度,即每S個地址取一個采樣點(diǎn);

(2)輸出最低頻率

(3)輸出最高頻率

查看原圖(大圖)雖然根據(jù)奈奎斯特采樣定理,一個周期采樣兩個點(diǎn)即可保證信號的頻譜信息不丟失,但為了輸出信號濾波后失真較小,一個周期至少采樣8個點(diǎn);故可知S的取值范圍應(yīng)該為1~2n-3;

(4)頻率分辨率△fo:△fo=fc/2n,與最低頻率一致。

2 DDFS的FPGA實現(xiàn)的參數(shù)計算

本設(shè)計充分運(yùn)用 CycloneII系列FPGA芯片EP2C35的片上資源來實現(xiàn)一個基于DDFS的正弦信號源。由于此芯片的片上可用ROM單元為483,840位二進(jìn)制,因此,片上ROM資源只能夠存儲215(32768)個8位二進(jìn)制采樣點(diǎn)的數(shù)據(jù)。

(1)ROM資源優(yōu)化:由于是正弦信號,因此只要采樣其(0,n/2)區(qū)間上的函數(shù)值,即可根據(jù)其周期性及對稱性,求出其他區(qū)間上的相應(yīng)的函數(shù)值。故,雖然片上資源只能存儲215(32768)個8位二進(jìn)制數(shù)據(jù),但運(yùn)用 正弦信號的對稱性,可實現(xiàn)217點(diǎn)采樣。由于正弦信號在(n~2n)間為負(fù)值,因此輸出函數(shù)值時,須要 執(zhí)行 補(bǔ)碼轉(zhuǎn)換;

(2)地址位長度:ROM的尋址地址為15位二進(jìn)制數(shù);

(3)步進(jìn)位長度:步進(jìn)最大應(yīng)為217/23=214,即步進(jìn)為14位的二進(jìn)制數(shù);

(4)相位控制字:相位是指讀取數(shù)據(jù)時,應(yīng)該屬于(0,2n)上的哪個區(qū)間,由于共有4個不同的區(qū)間。故可采用2位的二進(jìn)制數(shù)來標(biāo)識;不同的相位區(qū)間,決定著地址的讀取方向及輸出函數(shù)值能無法 取補(bǔ)碼運(yùn)算;

(5)任意波形的產(chǎn)生:要產(chǎn)生任意波形,可運(yùn)用 任意波形如矩形脈沖、三角波、鋸齒波等的傅利葉級數(shù)分解表達(dá)式,取其前有限次(如10次)諧波執(zhí)行 求和并存入指定的RAM單元,再依次讀出數(shù)據(jù),即可產(chǎn)生任意的信號。也可以將相應(yīng)波形的數(shù)據(jù)執(zhí)行 采樣,存入ROM中,按一定步進(jìn)執(zhí)行 讀取。通過以上剖析 ,在充分運(yùn)用 片上存儲單元,不擴(kuò)展外部存儲器,地址時鐘為10 MHz的基礎(chǔ)上,可得頻率分辨率為△f=78 Hz,輸出信號最高頻率(一個周期最少采樣8個點(diǎn))為fomax=fc/8=1.25 MHz;輸出信號最低頻率為fomin=Sfc/2ns=1=fc/217=78 Hz。若采樣點(diǎn)達(dá)到232個及以上,頻率分辨率可以做到0.015 Hz,達(dá)到mHz量級。可見運(yùn)用 Cyclone II系列芯片設(shè)計出性能優(yōu)良的信號源。根據(jù)DDFS的原理,其FPGA設(shè)計原理如圖2所示。其中控制單元由有限狀態(tài)機(jī)構(gòu)成。雖然整個系統(tǒng)的控制不一定須要 運(yùn)用 有限狀態(tài)機(jī),但由于運(yùn)用 的FPGA 芯片不支撐 異步的ROM,即從地址鎖存進(jìn)入ROM單元,到數(shù)據(jù)從ROM中讀出有至少一個時鐘周期以上的延時。因此采用狀態(tài)機(jī)來執(zhí)行 控制,可以達(dá)到較好的輸出與時鐘同步。控制流程為:時鐘信號進(jìn)入控制單元,由它產(chǎn)生地址發(fā)生單元的輸入時鐘adrclk,地址發(fā)生單元在時鐘adrclk的驅(qū)動下,結(jié)合輸入的步進(jìn)信號Step,產(chǎn)生地址及此地址所對應(yīng)的象限Phase,此地址產(chǎn)生后立即輸入到ROM單元中,過兩個時鐘周期后,控制單元從ROM存儲單元中讀出輸入地址對應(yīng)的數(shù)據(jù),并在時鐘的控制下,將前面所產(chǎn)生的象限值Phase與ROM數(shù)據(jù)一起送到補(bǔ)碼轉(zhuǎn)換單元,補(bǔ)碼轉(zhuǎn)換單元根據(jù)Phase的值來決定能無法 須要 執(zhí)行 補(bǔ)碼轉(zhuǎn)換,若須要 ,則執(zhí)行 補(bǔ)碼運(yùn)算并將數(shù)據(jù)輸出,若不須要 ,則直接將數(shù)據(jù)輸出。下面給出各模塊的詳細(xì) 設(shè)計細(xì)節(jié)。

(1)控制單元:控制單元是整個系統(tǒng)的核心部件。由一個基本 的有限狀態(tài)機(jī)構(gòu)成。其狀態(tài)轉(zhuǎn)換圖如圖3所示。

(2)地址發(fā)生單元:設(shè)計思路為根據(jù)輸入的Step值,計算出總共四個象限所需取值的點(diǎn)數(shù),也就可以計算出一個象限所要取值的點(diǎn)數(shù)m,然后在時鐘作用下執(zhí)行 計數(shù),當(dāng)計數(shù)值達(dá)m個時,說明一個象限內(nèi)已經(jīng)取完點(diǎn),此時phase自加1,計數(shù)變量重新置零。由于在(0,π/2)sin的函數(shù)值為從0→1變化; (π/2,π)函數(shù)值從1→0變化;(π,3π/2)函數(shù)值從0→-1變化;(3π/2,2π)函數(shù)值從-1→0變化。故在(0,π/2)和 (π,3π/2)地址值從0→32767,每隔一個步進(jìn)Step讀一個數(shù)據(jù),當(dāng)然后者的數(shù)據(jù)要經(jīng)過補(bǔ)碼單元的處理;而在(π/2,π)和 (3π/2,2π)象限,地址值則從32767→0,每隔一個步進(jìn)Step讀一個數(shù)據(jù)即可,同樣的,后者的數(shù)據(jù)也要經(jīng)過補(bǔ)碼單元的處理。(4)補(bǔ)碼轉(zhuǎn)換單元:根據(jù)目前地址所處象限來決定能無法 須要 執(zhí)行 補(bǔ)碼轉(zhuǎn)換。如產(chǎn)生正弦信號時,(0,π)象限sin函數(shù)值為正,而(π,2π)象限上sin 函數(shù)值為負(fù),因此在(π,2π)象限時,須要 對輸出數(shù)據(jù)執(zhí)行 補(bǔ)碼轉(zhuǎn)換。補(bǔ)碼轉(zhuǎn)換單元較基本 ,根據(jù)二進(jìn)制數(shù)取補(bǔ)的原理執(zhí)行 設(shè)計即可。

4 結(jié)果剖析

本設(shè)計在QuartusII6.0的平臺上完成設(shè)計工作,其仿真波形如圖4所示。在仿真波形中配置 的步進(jìn)長度為1024點(diǎn)。由于有狀態(tài)機(jī)執(zhí)行 流程控制,產(chǎn)生的波形較平滑,元多滑毛刺產(chǎn)生。若要進(jìn)一步提高輸出信號頻率范圍,則設(shè)計流程 中,不應(yīng)對時鐘信號執(zhí)行 分頻。

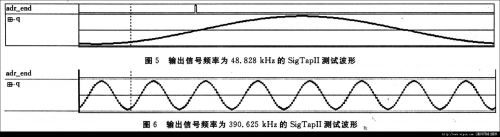

同時,還可以運(yùn)用 QuartusII的SigTapII工具對所設(shè)計的程序執(zhí)行 硬件驗證,配置 好相應(yīng)步進(jìn)后,相應(yīng)的輸出波形如圖5及圖6所示。可見所產(chǎn)生的低頻正弦信號波形平滑,而頻率較高時有一定的毛刺,這可以通過后級的低通濾波電路(如切比雪夫低通濾波網(wǎng)絡(luò)等)來執(zhí)行 濾除。

本設(shè)計運(yùn)用 的邏輯單元只占FPGA片上資源的1%,存儲單元占54%,I/O口占13%。可見主要資源為片上的存儲單元,如果提高一位地址位,則數(shù)據(jù)量翻倍,F(xiàn)PGA片上ROM不夠用。通過QuartusII6.0的時鐘剖析 ,本設(shè)計可達(dá)到的最高時鐘為149.41 MHz,而地址發(fā)生的時鐘為時鐘的4分頻,故地址發(fā)生單元的最高時鐘可達(dá)37.352 5 MHz,相應(yīng)的輸出信號最高頻率可達(dá)4.665 MHz,相應(yīng)的最低頻率及頻率步進(jìn)為284.976 Hz。

5 結(jié)束語

本設(shè)計在不向外擴(kuò)展ROM存儲器的情況下,對DDFS設(shè)計執(zhí)行 優(yōu)化,充分運(yùn)用 Cyclone II系列FPGA的片上資源,其輸出正弦信號最高頻率可達(dá)4 MHz以上。只要采用更好的方案執(zhí)行 設(shè)計,使采樣點(diǎn)可以做到232個及以上,頻率分辨率可以做到0.015 Hz,達(dá)到mHz量級,進(jìn)一步提高信號源的輸出信號頻率范圍及頻率分辨率等技能 指標(biāo),可運(yùn)用 Cyclone II系列芯片設(shè)計出性能優(yōu)良的信號源,達(dá)到實用信號源的要求。